Архив новостей из мира FPGA

Техника проектирования на ПЛИС

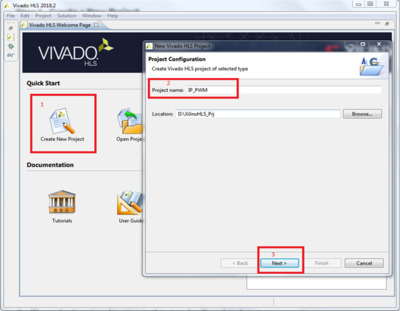

Для успешной реализации цифровых схем в ПЛИС необходимо глубокое знание основ цифровой схемотехники. Использование HDL упрощает цикл разработки, но для этого разработчик должен обладать хорошими знаниями в области проектирования цифровых схем. Хотя большинство разработчиков в основном знают цифровые компоненты, очен ... Читать дальше »

1289

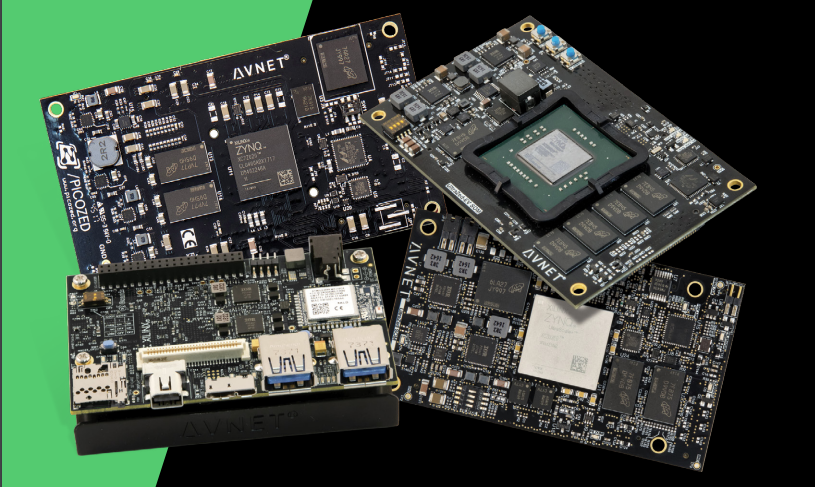

Экскурсия по легендарной серии отладок Zed

От ZedBoard до UltraZed, изучите краткую историю и узнайте, как вы можете воспользоваться преимуществами Zed в своем следующем проекте

Еще в 2011 году Xilinx представила семейство Zynq-7000, первую в отрасли расширяемую платформу обработки (EPP). Семейство Zynq-7000 состоит из процессора ARM &r ... Читать дальше »

1146

0

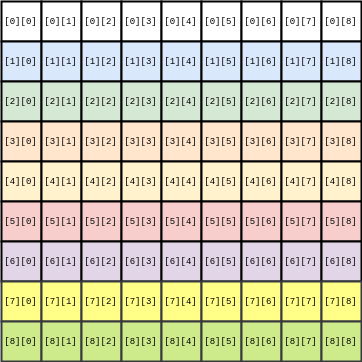

Решаем судоку на SystemVerilog

Наткнулся на пару любопытных заметок по не совсем традиционному использованию SystemVerilog. Автор сделал две заметки (раз и ... Читать дальше »

987

0

Lattice запускает Certus-NX Pro

Компания Lattice анонсировала расширение линейки Certus-NX. Новые FPGA серии Certus-NX Pro могут похвастаться: ... Читать дальше »

893

0

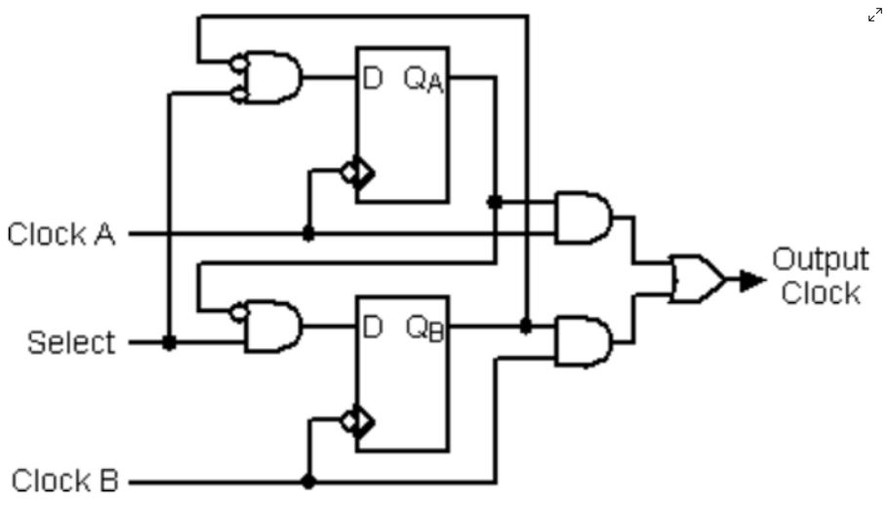

Мультиплексор тактовых сигналов

В блоге Адама тейлора появилась интересная заметка по переключению тактовых сигналов. В целом рассматривается, как устроены специальные мультиплексоры переключения тактовых сигналов, которые избавлены от глитч эффектов, которые можно словить, если использовать для мультиплексирования клоков обычные мультиплексоры. ... Читать дальше »

800

0

Вебинары по верификации от Trias Mikroelektronik

На сайте Trias Mikroelektronik выложена серия по UVVM верификации. Если при переходе по ссылке что-то по-немецки попадётся - пугаться не надо, т.к. сами вебинары - на английском. Чтобы получить доступ к вебинару - нужно указать емэйл и имя.

675

0

LPCV - Хакатон по компьютерному зрению

Цель хакатона - привлечь внимание к энергоэффективности ускорителей искусственного интеллекта и побудить исследователей к разработке новой архитектуры нейронных сетей, оптимизированной для ускорителей искусственного интеллекта.

Участникам необходимо создать эффективную модель машинного обучения, которая как ... Читать дальше »

768

0

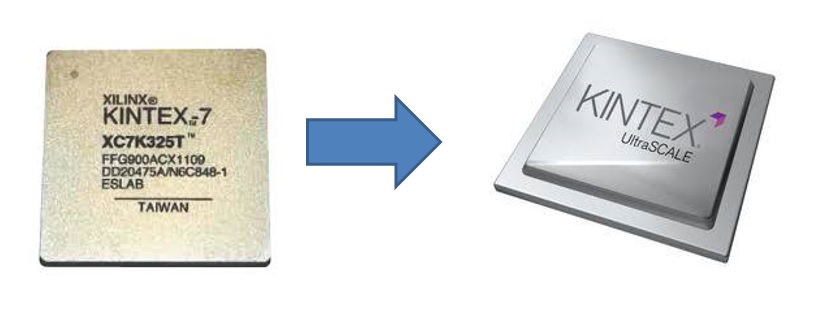

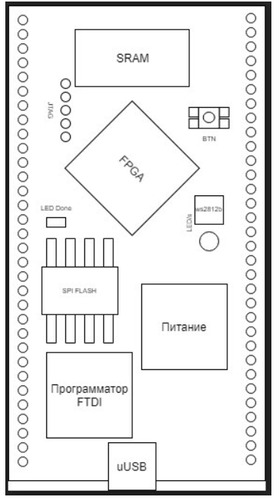

Перевод проектов с ПЛИС и СНК Xilinx серии 7 на UltraScale/UltraScale+

Как известно, новые серии ПЛИС и СнК сразу после выхода на рынок продаются значительно дороже, чем устройства уже присутствующие на рынке некоторое время. Затем цена новых устройств стремительно падает, и наступает момент, когда становится экономически выгоднее применять более современные серии устройств. В настояще ... Читать дальше »

879

0

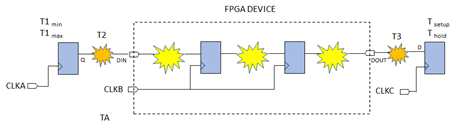

О важности временных ограничений при проектировании ПЛИС

“The LEC2 Workbench” запускает серию заметок в блоге Lattice Semiconductor, посвященных разработке приложений с использованием продуктов Lattice. Эти посты написаны экспертами по проектированию ПЛИС из Центра компетенций Lattice Education (LEC2), полной учебной и образовательной программы, разработанной ... Читать дальше »

766

0

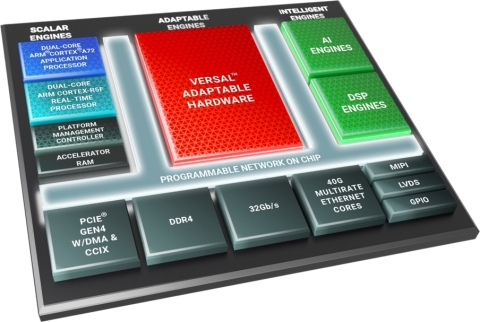

Анонсированы Xilinx Versal ACAP серии AI Edge

Компания Xilinx представила Versal™ серии AI Edge. Обладая в 4 раза большей производительностью ИИ на ватт по сравнению с GPU и в 10 раз большей плотностью вычислений по сравнению с адаптивными SoC предыдущего поколения, серия Versal AI Edge является самым масштабируемым и адаптируемым изделием в мире для распределенных интеллектуальных систем следующего поколения ... Читать дальше »

1091

0

0