Архив новостей из мира FPGA

Итоги российского форума «Микроэлектроника 2022»

Российский форум «Микроэлектроника 2022», прошедший с 2 по 8 октября 2022 года на горном курорте Роза Хутор (Сочи), стал самым масштабным событием в отрасли микро- и радиоэлектронной промышленности России. 8-й по счету форум состоялся в традиционном очном формате с использованием новейших цифровых технологий. В нем приняли участие 1710 делегатов из 665 госкорпораций, ведущих производственных предприятий, дизайн-центров, научных учреждений, вузов, коммерческих структур, СМИ и бизнес-сообществ. ... Читать дальше »

774

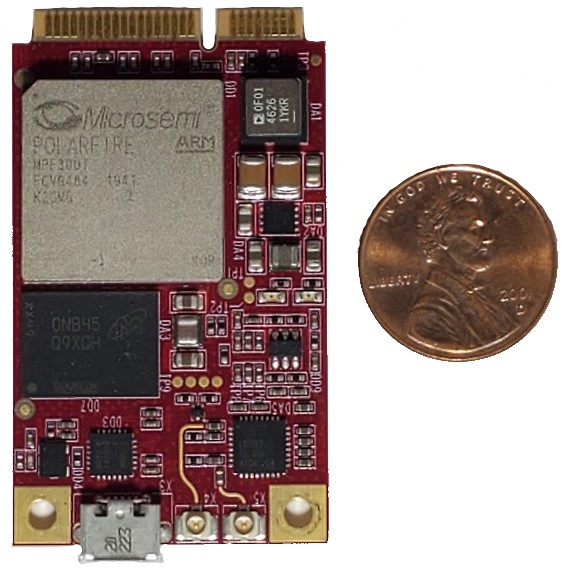

Модуль ввода-вывода и обработки Mini PCIe на базе FPGA Microsemi PolarFire MPF300T-1FCVG484

SE50-3G-SDI — это небольшая плата mini-PCIe с поддержкой видео 3G/SDI. Он использует PolarFire MPF300T-1FCVG484E FPGA для обработки и взаимодействия с хостом. Чип TI LMH0397 используется для функциональности 3G/SDI. Он имеет 2 разъема U.FL, которые можно использовать в качестве 2 выходов или как один вх

...

Читать дальше »

406

0

Серия из 3-х семинаров Vitis AI Development on AMD Xilinx Adaptive Platforms

Среда Vitis™ AI — это комплексная платформа для разработки выводов искусственного интеллекта на устройствах, девайсах и платах AMD Xilinx и картах ускорения центров обработки данных Alveo™. Он предлагает богатый набор моделей ИИ, оптимизированный IP-адрес процессора глубокого обучения (

...

Читать дальше »

1093

0

Быстрое создание передовых решений для искусственного интеллекта на ПЛИС

На этом вебинаре будут рассмотрены идеи по выявлению и развертыванию обученных моделей искусственного интеллекта на ПЛИС. Технический сотрудник Doulos, доктор Рахул Дубей, расскажет о современных программных инструментах и API, которые помогают в создании решения Edge AI на базе ПЛИС.

...

Читать дальше »

272

0

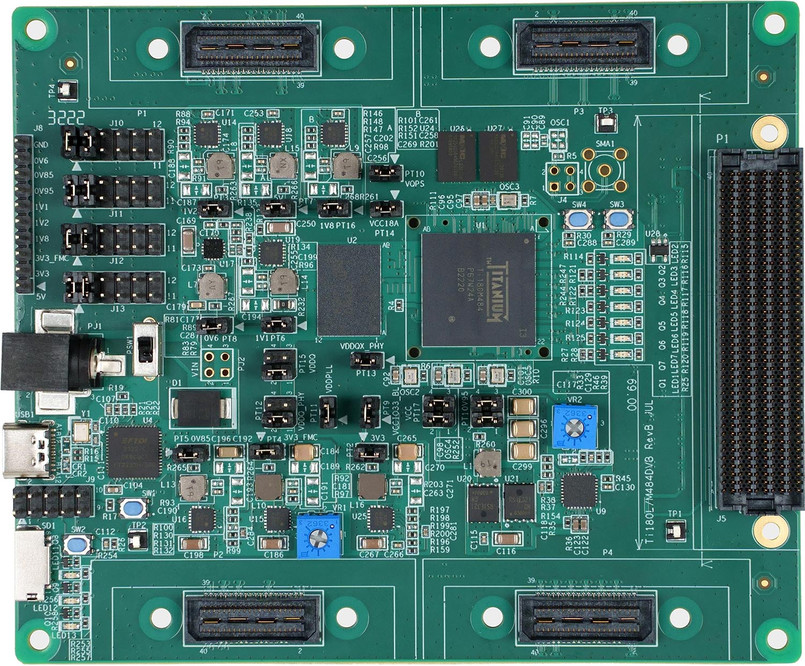

Девкит Titanium Ti180 M484 от Efinix

Набор для разработки Titanium Ti180 M484 содержит все необходимое для разработки и создания прототипов на ПЛИС Ti180. Этот комплект имеет MIPI D-PHY Ti180, поддерживающий скорость до 2,5 Гбит/с на полосу, и контроллеры LPDDR4x. У ... Читать дальше »

603

0

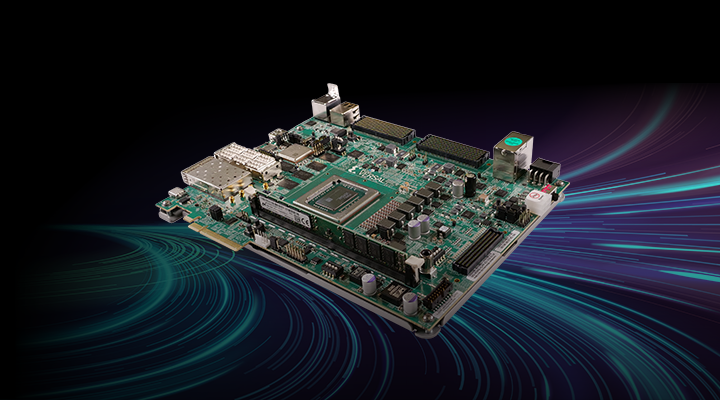

Ускорение электронной торговли с помощью новой серии Alveo™ X3

Сегодняшние ведущие маркет-мейкеры, хедж-фонды и биржи требуют исполнения сделок с низкой задержкой и управления рисками для получения конкурентных преимуществ. Новая серия Alveo™ X3 — это первые сетевые карты AMD, разработанные с использованием screened FPGA (напишите в комментах что за screened FPGA) и оптимизированные специально для торговли с низкой задержкой. В настоящее время карты в производстве и отгружаются. ... Читать дальше »

499

0

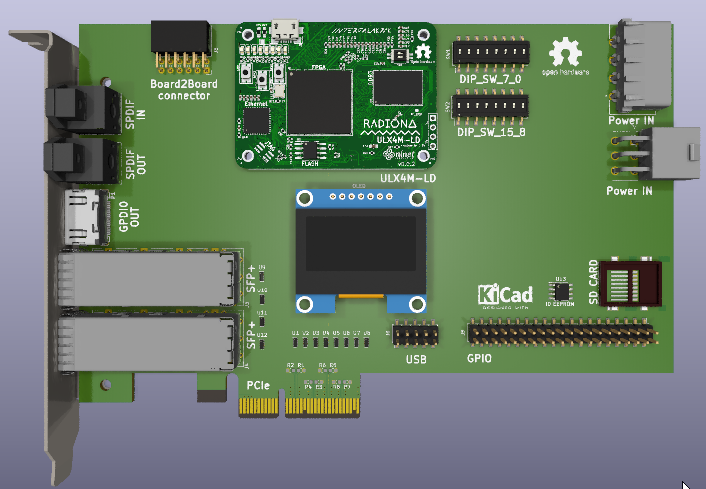

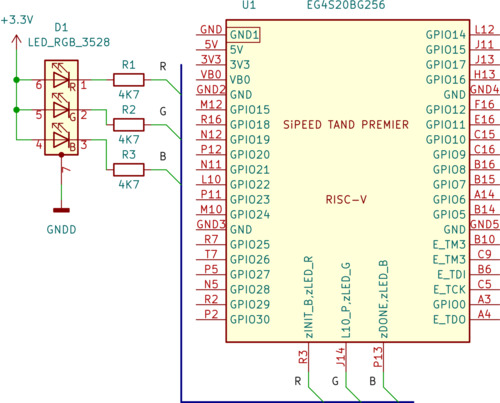

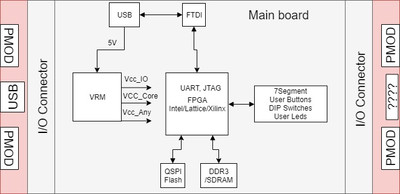

OpenSource отладка ULX4M-PCIe-IO

Компания NLnet выложила в открытый доступ исходники в KiCad несущей платы для другого opensource модуля ULX4M ... Читать дальше »

439

0

Вебинар: Hacking FPGAs & SoC FPGAs

ПЛИС все чаще используются в критически важных приложениях.

Например:

- национальная инфраструктура (электросети, сетевые маршрутизаторы и спутники)

- транспорт (самолеты, поезда и автомобили)

...

Читать дальше »

1105

0

Микроэлектроника 2022: анонс пленарного заседания и трека обзорно-дискуссионных заседаний «Развитие экосистемы создания доверенной ЭКБ и РЭА

Одной из центральных тематических линий Форума в этом году является обеспечение доверенности ЭКБ и РЭА как важнейшего составного элемента конкурентоспособности изделий. ... Читать дальше »

337

0

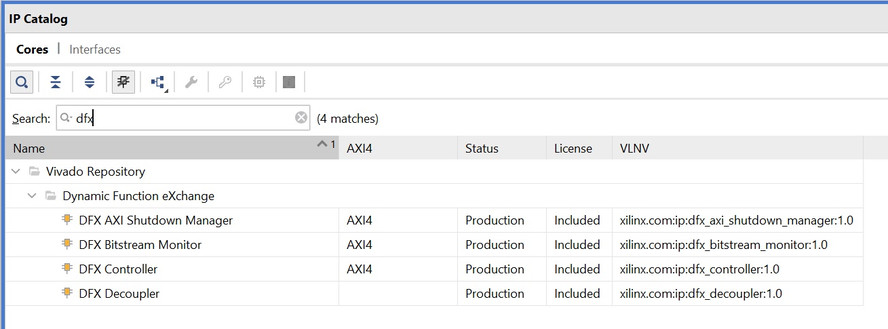

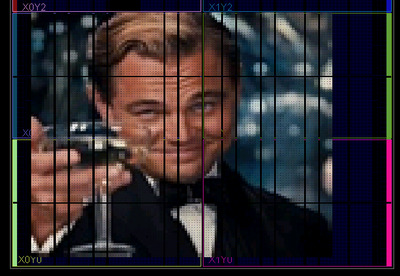

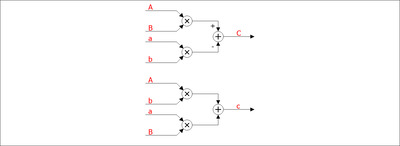

Введение в технологию DFX от Xilinx. Вебинар

Современная технология реализации частичной реконфигурации (DFX – Dynamic Function eXchange) позволяет загружать в ПЛИС только те ядра, которые используются в данный момент, и, таким образом, эффективно и экономно использовать объём за счет разделения ресурсов ПЛИС. В текущих условиях экономия ресурсов – это актуальная задача. Кроме того, на технологии DFX построены аппаратные ускорители Xilinx. Разработка c использованием DFX значительно сложнее, чем стандартный маршрут проектирования. ... Читать дальше »

447

0

0