III КОНФЕРЕНЦИЯ FPGA РАЗРАБОТЧИКОВ

## FPGA-Systems 2021.2

Доступно в записи на Youtube

Конференция в Москве

Конференция в Санкт-Петербурге

#### Приходи на следующую конференцию

fpga-systems.ru/meet

Поддержи мероприятие

Способ 1

Способ 2

## FPGA-Systems 2021.2

## ALDEC: Программная и аппаратная верификация ПЛИС по стандарту КТ-254

Александр Акулин Технический директор компании PCB SOFT Официальный дистрибьютор ALDEC, Cadence, Downstream akulin@pcbsoftware.com

#### Что такое стандарт КТ-254 и DO-254

- KT-254 это руководство по гарантии конструирования бортовой электронной аппаратуры

- Российский стандарт КТ-254 основан на зарубежном аналоге под названием DO-254

#### Что такое верификация (по КТ-254)

- Назначение: подтвердить, что реализация оборудования соответствует поставленным требованиям

- Включает в себя: рассмотрение проекта, анализ, испытания

- Анализ можно выполнить с помощью моделирования, но испытания должны быть проведены как функциональный тест

реального оборудования

#### Назначение продуктов ALDEC для верификации

- Обеспечить эффективную и удобную верификацию выполнения требований путем аппаратного тестирования

- Увеличить покрытие верификации

- Предоставить адаптированное программно-аппаратное решение для тестирования ПЛИС на рабочей скорости

- Предоставить единую автоматизированную среду для верификации всех требований на уровне ПЛИС

- Сократить цикл верификации

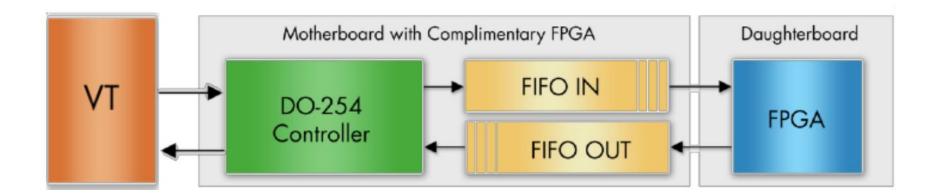

#### Состав комплекса ALDEC DO-254/CTS для программно-аппаратного тестирования

Программное обеспечение DO-254 CTS CVT Конвертирует тестовые вектора Управляет процессом тестирования

• Материнская плата DO-254 COTS

Дочерняя плата с целевой ПЛИС

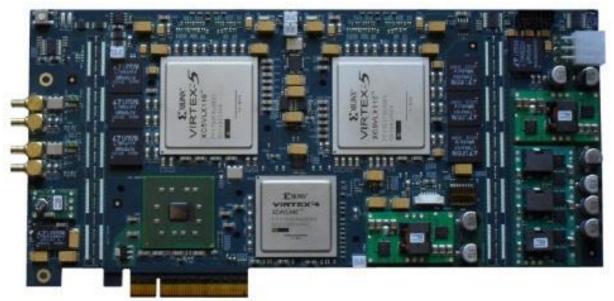

#### Материнская плата DO-254 COTS

- Передает тестовые вектора в ПЛИС «на скорости»

- Принимает отклики ПЛИС «на скорости»

- Интерфейс PCI/е и память DDRII 4 Гбайт

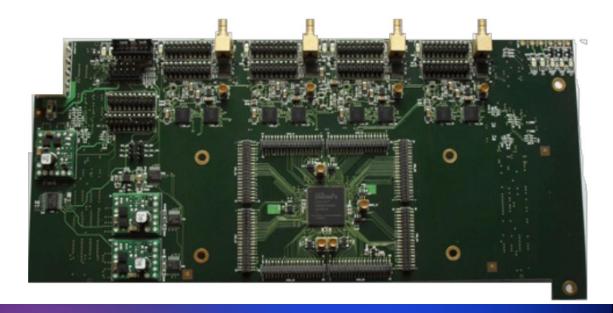

#### Дочерняя плата (кастомизированная под проект)

- Содержит «целевую» ПЛИС с «целевой» прошивкой

- Адаптирована под задачи конкретного проекта или группы проектов

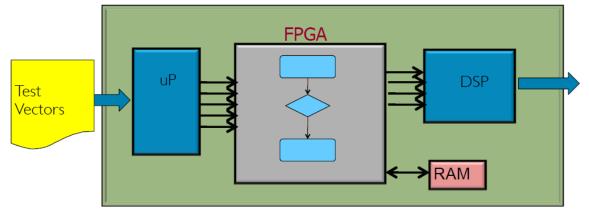

#### Принцип тестирования

#### Процесс тестирования

VT – Verification Tool программирует целевую ПЛИС, считывает входные вектора, управляет тестированием, генерирует выходные вектора

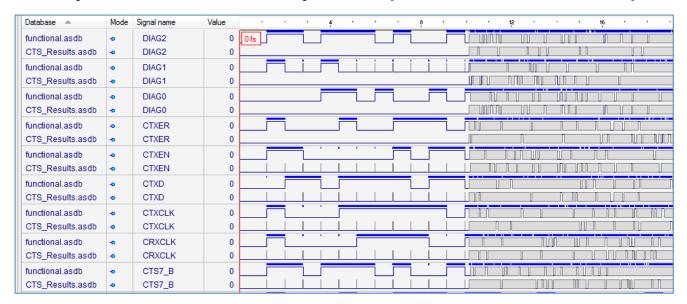

#### Анализ результатов тестирования

- Система показывает места несовпадений выходных векторов с «золотыми» векторами, полученными при моделировании

- Результат можно визуализировать в виде диаграмм

## Преимущества по сравнению со способом тестирования «в составе изделия»

- При обычном подходе к тестированию ПЛИС в составе изделия:

- Через ПЛИС проходят только реальные данные

- Выходы ПЛИС подсоединены к другим устройствам на плате

- Нет «пробников» на каждом входе/выходе ПЛИС

**Board Under Test**

#### Недостатки теста «в составе изделия»

- Трудно убедиться, что результаты моделирования и физического тестирования совпали

- Трудно разработать входные данные для тестирования выполнения всех требований

- Ограниченные возможности контроля входов/выходов

- Покрытие тестами в большинстве случаев недостижимо

- Сложно документировать результаты тестирования

- Сложно автоматизировать тестовую среду для реализации большого количества тестовых кейсов

#### Преимущества теста с ALDEC DO-254/CTS

- Верификация «целевой» ПЛИС на полной скорости

- Повторное использование Testbench как тестовых векторов

- Повторное использование тестовых кейсов

- Тестирование на основе требований

- Не требуется изменять проект или Testbench

- Проверка ПЛИС не требует отладки целевой печатной платы

- Упрощена проверка надежности функционирования проекта ПЛИС. Можно создать такие входные воздействия и отклонения, которые трудно искусственно воссоздать на целевой плате

- Упрощено считывание результатов, анализ и документирование

#### Проверка надежности с ALDEC DO-254/CTS

- Для уровней гарантии аппаратуры A и B по стандарту КТ-254 требуется проверка надежности проекта ПЛИС

- В реальной целевой плате трудно создать такие тесты:

- Неверные комбинации сигналов или прерывание потока данных

- Выход сигнала синхронизации за пределы допуска

- Управление частотой сигнала

- Вставка лишнего импульса синхронизации

- Варьирование граничных условий по времени Setup/Hold

- Проверка защелкивания значений данных в регистр

- Пересечение доменов синхронизации

- Варьирование уровня напряжений сигнала на входах ПЛИС

#### Примеры реальных проектов дочерних плат 1

- Целевая ПЛИС Microsemi ProASIC A3P1000-FG484-2

- Тактовая частота: 66 МГц

- Количество входов/выходов: 62

- Время верификации: 50 мс

- Верификация целевой ПЛИС «на полной скорости» Использование тестовых векторов RTL Результаты тестирования сохранены и задокументированы для отчетности по стандарту DO-254

#### Примеры реальных проектов дочерних плат 2

- Целевая ПЛИС Altera Cyclone III EP3C40F780C8

- Тактовая частота: три клока @65MHz, @13MHz, @66MHz

- PLL для управления клоками

- Количество входов/выходов: 370, включая LVDS и SERDES

- Время верификации: 300 мс

- Нюанс тестирования варьирование напряжений +-10%

- Верификация целевой ПЛИС «на полной скорости» Использование тестовых векторов RTL Результаты тестирования сохранены и задокументированы для отчетности по стандарту DO-254

#### Примеры реальных проектов дочерних плат 3

- Целевая ПЛИС Xilinx SPARTAN 3A XC3S700A-FG400I

- Тактовая частота: 2 клока @48 MHz, @40MHz

- DCM (Digital Clock Manager) для управления клоками

- Количество входов/выходов: 212

- Время верификации: 200 мс

- Нюанс незадействованные входы/выходы и клоки, тем не менее, добавлены в проект дочерней платы «на будущее»

- Верификация целевой ПЛИС «на полной скорости» Использование тестовых векторов RTL Результаты тестирования сохранены и задокументированы для отчетности по стандарту DO-254

## Пример информационного листа для заказа дочерней платы

| DO-254/C                              | ТЅ Инфор                                                       | мацио                     | нный л         | ист описа                                                                                           | ния входов                                                         | в/выход                           | ов ПЛИ                                       | C                                                                                                            |

|---------------------------------------|----------------------------------------------------------------|---------------------------|----------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Инструкция: Заполните нижеследующу    | ∣<br>/ю информацию. На осн                                     | <br> ове этой инфор       | мации будет вы | олнена кастомизация <i>,</i>                                                                        | <br>цочерней платы DO-254/CT                                       | S, программного с                 | рбеспечения матер                            | инской платы,                                                                                                |

| диагностических проектов и руководств | а пользователя.                                                |                           |                | ·                                                                                                   |                                                                    |                                   |                                              |                                                                                                              |

| Компания:                             |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

| Проект:                               |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

| Дата:                                 |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

| Планируемая дата поставки DO-254/     | CTS:                                                           |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

| Имя сигнала                           | Тип сигнала<br>(отметьте CLK для<br>сигналов<br>синхронизации) | Режим (IN,<br>OUT, INOUT) |                | Имя сигнала синхронизации, который тактирует данный сигнал (впишите ASYNC для асинхронных сигналов) | Частота тактирования<br>(не заполнять для<br>асинхронных сигналов) | Номер вывода<br>в целевой<br>ПЛИС | Используемое<br>Vi/o (например,<br>LVCMOS33) | Резистор<br>Pullup/Pulldown<br>для размещения<br>на дочерней<br>плате (оставьте<br>пустым, если не<br>нужен) |

|                                       |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

|                                       |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

|                                       |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

|                                       |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

|                                       |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

|                                       |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

|                                       |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

|                                       |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

|                                       |                                                                |                           |                |                                                                                                     |                                                                    |                                   |                                              |                                                                                                              |

#### Оценка и квалификация инструментов ALDEC

- Ошибка в инструменте конструирования может вызвать ошибку в элементе аппаратуры

- Ошибка в инструменте верификации может привести к пропуску ошибки в элементе аппаратуры

- Прежде чем использовать инструмент, необходимо выполнить его оценку.

- Результаты этой оценки и, если необходимо, квалификация инструмента, должны быть документированы.

- В маршруте, предложенном ALDEC, инструменты конструирования (симулятор Active-HDL и средство проверки RTL-кода ALINT-PRO) разнесены со средствами верификации (система DO-254/CTS)

#### Ответы на вопросы

Александр Акулин

Технический директор компании PCB SOFT

Официальный дистрибьютор ALDEC, Cadence, Downstream

akulin@pcbsoftware.com

# DISCOVER. DESIGN. DEVELOP.

yadro.com

Генеральный партнер конференции FPGA-Systems 2021.2

## tech@exponenta.ru exponenta.ru

- Технические консультации

- Подбор инструментов

- Обучение специалистов

- Работа на заказ

Генеральный партнёр конференции FPGA-Systems 2021.2

Первая современная отечественная САПР, реализующая сквозной цикл проектирования печатных плат

#### Информационные партнеры

Портал инженерной

культуры\_

### Где найти FPGA комьюнити?

- > youtube.com/c/fpgasystems

- admin@fpga-systems.ru