## III конференция грса разработчиков FPGA-Systems 2021.2

#### Доступно в записи на Youtube

Конференция в Москве

Конференция в Санкт-Петербурге

#### Приходи на следующую конференцию

#### Поддержи мероприятие

#### третья конференция FPGA разработчиков FPGA-Systems 2021.2

## YET ANOTHER FPGA MEZZANINE

#### **DMITRY MURZINOV**

#### **TELEGRAM CHANNEL**

### **FPGASIC BOOK**

### WHO AM I

#### **DMITRY MURZINOV**

- ★ Ms Degree in Radio Engineering

- ★ 17 years FPGA experience

- ★ 13 years ASIC experience

- ★ 7 years Signal Processing

- ★ 3 years in HW Cryptography

- ★ 2 years in ML implementation on HW

### DISCLAIMER

- User of DevBoard Point of View

- **The time-limited presentation**

- □ A quite prepared audience

- □ The Final|Draft specs doesn't exist at the moment

#### AGENDA

#### **EXISTING SOLUTIONS (HISTORY)** THE MAIN ISSUES OF CURRENT SOLUTIONS WHY NEXT GEN MEZZANINE? (PROS ANS CONS) **USECASES** ROADMAP CONCLUSION

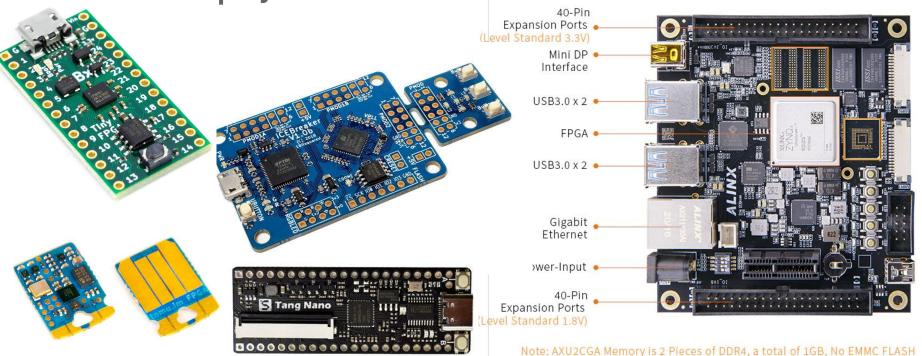

HSMC (High Speed Mezzanine Card) (Altera) VITA57 2008: FMC HPC/LPC, FMC+ (FPGA Mezzanine Card) **PMOD** (Digilent) ZMOD (Digilent, based on SYGYZY by Opal Kelly) VHDCI (Vmod from Digilent) \*MicroMod (NGFF based with modified mounting)

#### CRUVI

#### Working Group Members:

- Flinders University

- FOSSi Foundation

- MicroFPGA UG

- Symbiotic EDA

- Trenz Electronic GmbH

- Samtec

#### Some crowdfunding projects:

#### **Random FPGA-projects from Web:**

#### FMC'S ISSUES

#### 1. Connectors' lead time (time-to-deployment)

#### 5767056-1

| ETE                      | Mouser No:          |  |

|--------------------------|---------------------|--|

| Accreditor contribution  | Mfr. No:            |  |

| Bunnet                   | Mfr.:               |  |

| Concession of the second | Customer No:        |  |

|                          | Description:        |  |

| Q Enlarge                |                     |  |

| Images are for reference | Datasheet:          |  |

| only<br>See Product      | ECAD Model:         |  |

| Specifications           | Download the free l |  |

#### 571-5767056-1 5767056-1 TE Connectivity / AMP Customer No Board to Board & Mezzanine Connectors .025 PLG 2X019P VRT > 5767056-1 Datasheet PCB Symbol, Footprint 3D PCB Symbol & 3D Model Download the free Library Loader to convert this file for your ECAD Tool. Learn more about the ECAD Model.

#### Compare Product

Add To Project | Add Notes

#### In Stock: 260

| Stock:                | 260 Can Dispatch Immediately      11 Weeks ?     Minimum: 1 Multiples: 1     Buy |            |

|-----------------------|----------------------------------------------------------------------------------|------------|

| Factory Lead<br>Time: |                                                                                  |            |

| Enter<br>Quantity:    |                                                                                  |            |

| Pricing (EUR          | )                                                                                |            |

| Qty.                  | Unit Price                                                                       | Ext. Price |

| 1                     | 20,14 €                                                                          | 20,14 €    |

| 10                    | 18,18 €                                                                          | 181,80€    |

| 21                    | 17,41 €                                                                          | 365,61€    |

| 42                    | 16,33 €                                                                          | 685,86 €   |

| 105                   | 15,78 €                                                                          | 1.656,90 € |

| 252                   | 14,91 €                                                                          | 3.757,32€  |

| 504                   | 14,47 €                                                                          | 7.292,88 € |

#### Pinned Message

Всем-FPGA! Вот и осень, а это значит, что нас.

#### Sergey Brazhnikov

#### Kostya Dobrosolets On-board не канает?

Хотим использовать плату в качестве отладки для ASIC системы, для этого используем свисток на FTDI и собственный отладчик на OpenOCD. Проект влазит только в эту плату, а GPIO у нее только на высокоскоростные интерфейсы выведен, разъем для которых в поставке 3 недели. Я решил спросить, может кто видел готовые варианты перехода от разъема 5767056-1, чтобы не тратить время на разводку своей платы. 10:42

#### Alexander Kim

я там фмц вижу две штуки. они обычно тоже 2-3 недели едут, но переходники на pls точно есть, возможно они тоже поставкой 2-3 недели, а возможно в наличии есть.

как вариант, в комплекте к плате должна быть fmc loop back card, туда можно проводов напаять, если только жытаг нужен (4-5 проводов), но жалко карточку портить. с другой стороны её обычно никто не пользуеит 🔥 1 10:46

#### Sergey Brazhnikov

Alexander Kim

-9-

как вариант, в комплекте к плате должна быть fmc loop b... Тут согласен, жалко карточку портить 10:48

#### Alexander Kim

ну это если вот прям срочно надо, а на долгосрок есть смысл либо купить, либо сделать свой fmc переходник, а то и несколько, он рано или поздно понадобится. потому что большинство современных отладок как у ксайлинкса, так и у альтеры уже не имеют классических pls c gpio **A** 2 10:49

#### Sergey Brazhnikov

Alexander Kim

ну это если вот прям срочно надо. а на долгосрок есть с...

будем делать свой тогда, спасибо за совет. Может на гите где есть готовые решения? 10:50

## FMC'S ISSUES

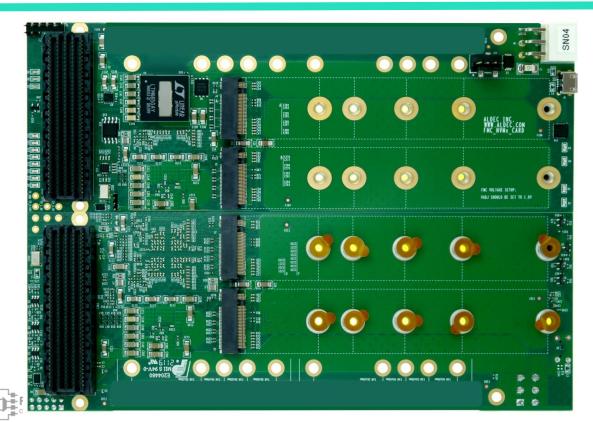

- 2. Daughter boards cost (a quite expensive):

- **Connector's cost**

- **PCB** cost:

- □ Should be Multilayer (to routing 40x10 pins' array)

- **Dimension (defined by FMC standard)**

- **Soldering procedure:**

- BGA-like footprint (do not try at home)

## **MEET NEXT GEN FPGA MEZZANINE**

## **DOKARD'S MOTIVATION**

- □ Nearly Zero Waste

- Rapid time-to-deploy

- Daughter boards as cheap as possible (e.g. "no cost" connectors by design)

Flexibility in terms of purpose (usecases)

- Powerful Plug&Play capabilities

#### See next slides for detail

## NEARLY ZERO WASTE

No plastic for connectors (on daughter-board side)

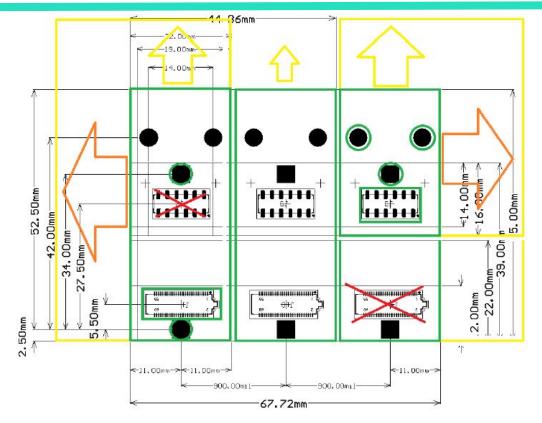

Minimal PCB size started from 22mm x 30mm (enough for most "single IC" daughter-boards)

Reuse and Aftermarket (hopefully DOKARD boards will be widely accessibility)

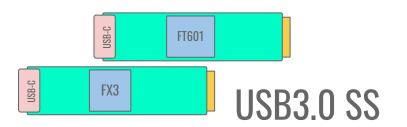

## **RAPID TIME-TO-DEPLOY**

## **BOARD'S COST**

- (DOKARD-based) Daughter boards might be as cheap as possible.

- **Decided to move some components on MainBoard:**

- Connector and ESD clamps

- DC/DC for Vadj generating

- □ Source clocks synthesizing capabilities

- □ LEDs, DIP switches

- Terminals

- **USB-hubs/USB-connectors**

- Signal level translators (see slide UNDER CONSIDERATION)

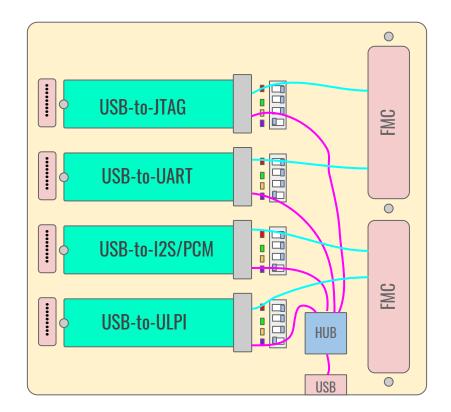

### **USECASES**

- 1. MVP of FPGA projects (before releasing HW rev.1)

- 2. ASIC prototyping (HW in loop)

- 3. PoC (Proof of Concept) of SBC/SoC projects

- $\circ~$  Including small production batches

- 4. HW Electronics Enthusiasts

## **MVP OF FPGA PROJECTS**

MVP of FPGA projects (e.g. before releasing HW rev.1)

Early build on real HW-environment and bring-up procedures

Production of tiny batches for rapid time-to-market (it might be faster and cheaper in comparison with FMC-based design)

## **ASIC PROTOTYPING**

Hardware-in-the-Loop capabilities

Included all advantages of previous item

## PoC OF SBC/SoC PROJECTS

- **Proof of Concept and Small Batches for SBC/SoC-based projects**

- Rapid time-to-market and small batches production

- **End-user features configurability**

## **DIY ELECTRONICS ENTHUSIASTS**

## **PLUG & PLAY CAPABILITIES**

#### T.B.D. (See ROADMAP slide)

## **DOKARD DISADVANTAGES**

- 1. 0.8mm PCB thickness required

- 2. Highly recommend ENIG finishing for PCB

- 3. Low mechanical hardness (PCB strength)

- 4. Poor availability of DOKARD boards (hopefully temporary)

## **DOKARD'S SERVICE SIGNALS**

- MA[0:2]

- 2. I2C

- 3. CLK P/N

- Vadi 4.

- 5.

- LED[0:3] 6.

- DIP[0:3]

- be considering)

- USB DP/DM 9

- To mainboards USB-hub/USB-connector

- Module address (to I2C EEPROM or/and future use)

- Plug & Play config from I2C EEPROM

- Clock's differential pair or two single ended clocks

- DC/DC to produce required voltage level (same as FMC)

- PWR\_EN/RESET Power enable for module and reset (both are redundant)

- For indications onto mainboard

- To set up settings from mainboard's DIP switches

- 8. TERMINAL[0:7] Mainboard's EXTernal connector (IDC or most proper should

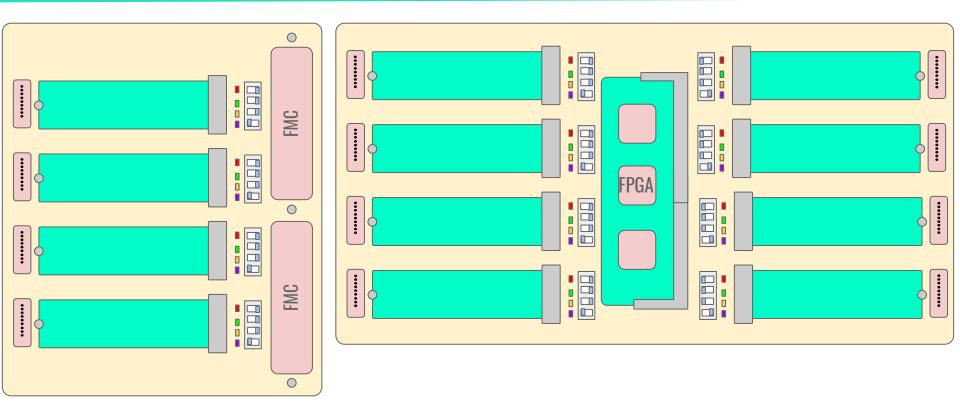

### ROADMAP

- □ A kind of several types of boards:

- Low cost (1-layer PCB solution w/o P&P)

- □ "Standard" (LPC & HPC as in FMC)

- □ HighSpeed (replica of NVMe-pinout for example)

- Enhancement plug&play capabilities (inspired by Litex and IPMI)

- Design FMC-to-DOKARD PCB adapter

- Design FPGA DevKit with DOKARD mezzanine supports

- **Based on FPGA SoM**

- □ Allow 2 layer PCB to demonstrate convenience\*

#### ROADMAP

## **UNDER CONSIDERATION**

- **Right place and principles of using signal level shifters**

- Compatibility issue: should we use NGFF M-key for HighSpeed edition (e.g. for NVMe SSD bolt-on) in addition of NGFF B-key usage

- □ Scalability: implementing of cards teaming by 1x, 2x, 4x (see next slide)

- Mechanical uncertainty:

- □ Card's length dimensions (currently: only 30mm and 80mm)

- □ Card's width dimensions (NGFF refs: 22mm and 30mm)

- Mounting methods

- On-card connectors placement (hot topic)

## **UNDER CONSIDERATION**

## Non-NGFF dimensions and mountings

Cards teaming by 2x (increase the available pins count)

### **FEEDBACK / REFERENCES\***

#### github.com/dokard

## CONCLUSION

#### PROS:

- Nearly Zero Waste

- Rapid time-to-deploy

- **Daughter boards as cheap as possible**

- □ Flexibility in terms of purpose usage

- Powerful Plug and Play capabilities

#### CONS:

- O.8mm PCB thickness required

- Highly recommend special finishing for PCB

- □ Relatively low mechanical hardness (PCB strength)

- Poor availability of DOKARD boards (hopefully temporary)

## DISCOVER. DESIGN. DEVELOP.

yadro.com

Генеральный партнер конференции FPGA-Systems 2021.2

Технические консультации Подбор инструментов Обучение специалистов Работа на заказ

# EREMEX

Генеральный партнёр конференции FPGA-Systems 2021.2

Первая современная отечественная САПР, реализующая сквозной цикл проектирования печатных плат

<sup>SDK</sup> Комплект программиста (SDK)

EREMEX

www.eremex.ru

........

#### Информационные партнеры

Сообщество приборостроителей

культуры\_

## Где найти FPGA комьюнити?

t.me/fpgasystems <=> @fpgasystems

#### youtube.com/c/fpgasystems

admin@fpga-systems.ru