IV КОНФЕРЕНЦИЯ FPGA РАЗРАБОТЧИКОВ

# FPGA-Systems 2023.1

Актуальное расписание FPGA слётов fpga-systems.ru/meet

Доступно в записи на Youtube

Москва

Санкт-Петербург

# Где найти FPGA комьюнити?

fpga-systems.ru

t.me/fpgasystems <=> @fpgasystems

## Поддержи комьюнити и будущие слёты

Вариант\_0

Bapuant\_1

boosty

# FPGA-Systems 2023.1

# FPGA vs ASIC сравнение маршрутов

Как мы пришли к созданию внутреннего курса FPGA to ASIC

Александр Огурцов

Александр Огурцов

TeamLead по FPGA прототипированию, YADRO

ФГБОУ ВО НИУ МЭИ, "Радиотехника", 2009

### Milestones

Разница в архитектуре FPGA и ASIC

FPGA vs. ASIC: достоинства и недостатки

Маршрут проектирования FPGA vs ASIC

Поговорим о нашем курсе

Что нужно чтобы попасть на наш курс

Milestones

### Разница в архитектуре FPGA и ASIC

FPGA vs. ASIC: достоинства и недостатки

Маршрут проектирования FPGA vs ASIC

Поговорим о нашем курсе

Что нужно чтобы попасть на наш курс

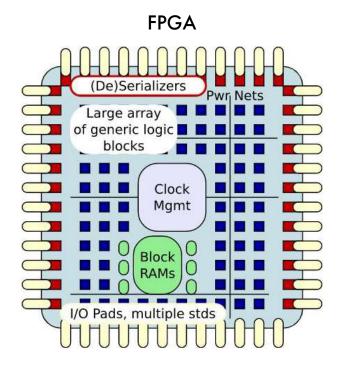

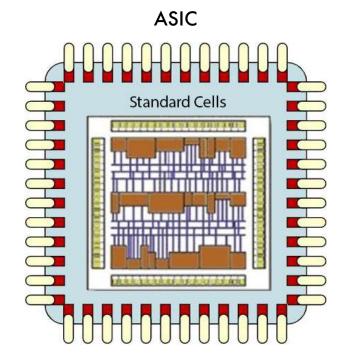

### Разница в архитектуре FPGA и ASIC

#### Основные отличия

- Standard Cells

- Clocks

- Resets

- On-chip RAM

- I/O peripherals

- Power

- Process variations

- Tools

Milestones

Разница в архитектуре FPGA и ASIC

### FPGA vs ASIC: достоинства и недостатки

Маршрут проектирования FPGA vs ASIC

Поговорим о нашем курсе

Что нужно чтобы попасть на наш курс

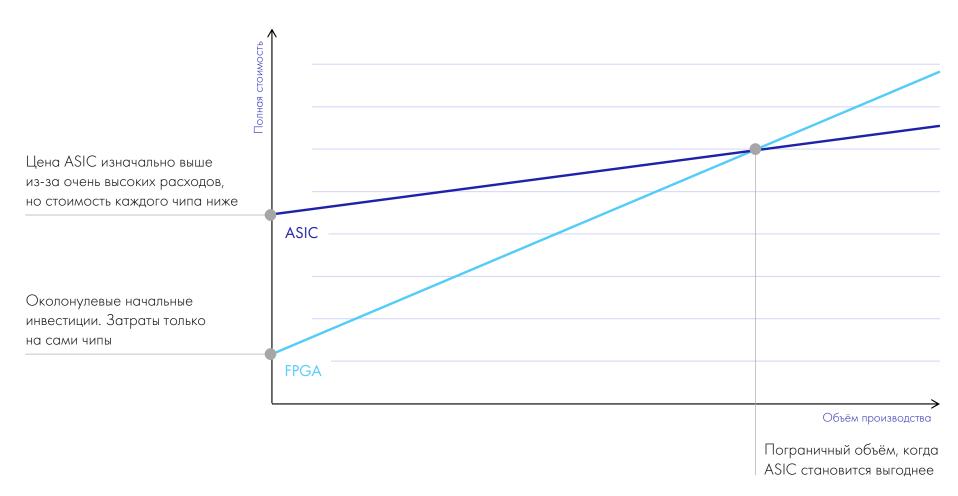

### FPGA vs ASIC: достоинства и недостатки

| Property                     | FPGA    | ASIC    |

|------------------------------|---------|---------|

| Маршрут разработки           | Простой | Сложный |

| Время выхода на рынок        | Малое   | Большое |

| Единовременные расходы       | Низкие  | Высокие |

| Производительность (частота) | Низкая  | Высокая |

| Мощность                     | Высокая | Низкая  |

| Специальные IPs (analog)     | Нет     | Есть    |

| Отладка (RAS)                | Есть    | Нет     |

#### YA Dro

### FPGA vs ASIC: достоинства и недостатки

Milestones

Разница в архитектуре FPGA и ASIC

FPGA vs ASIC: достоинства и недостатки

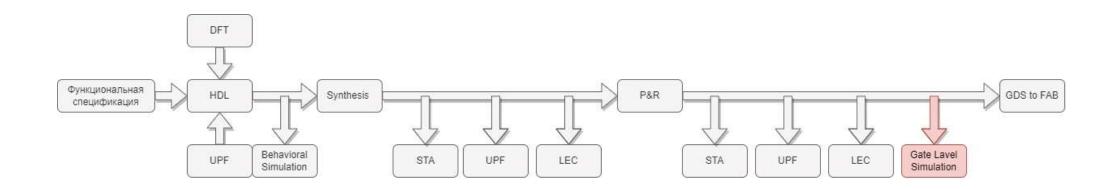

### Маршрут проектирования FPGA vs ASIC

Поговорим о нашем курсе

Что нужно чтобы попасть на наш курс

#### YA DRO

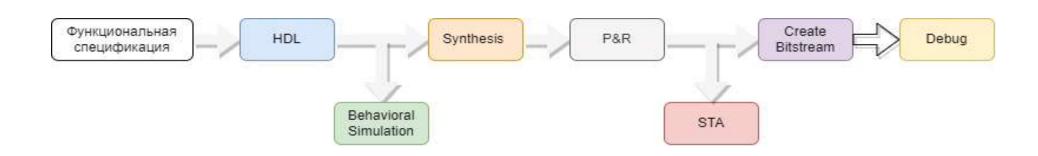

### Упрощенный маршрут проектирования для FPGA

#### YA Dro

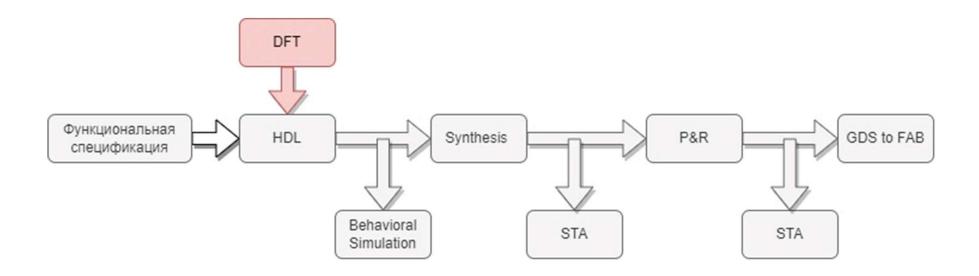

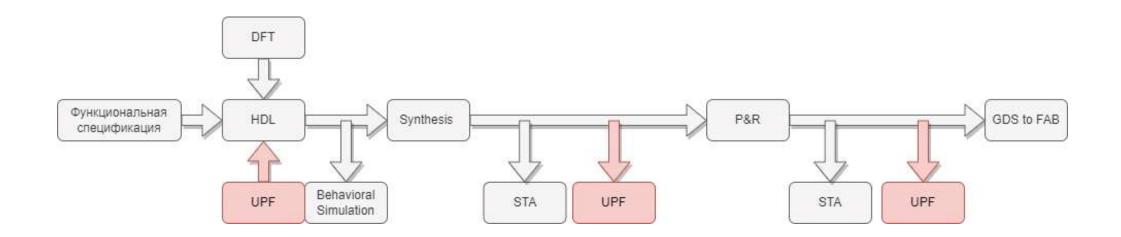

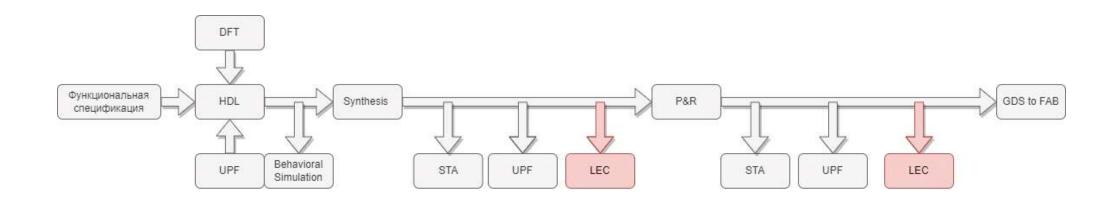

### Упрощенный маршрут проектирования для ASIC

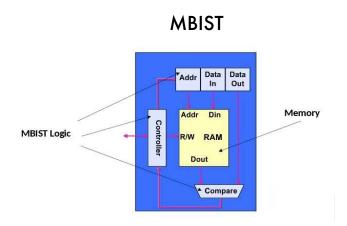

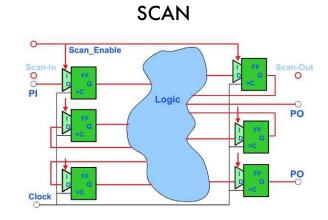

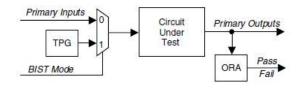

### DFT-design for test

### Упрощенный маршрут проектирования для ASIC

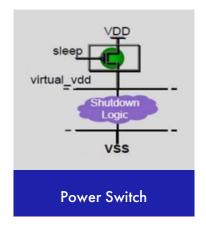

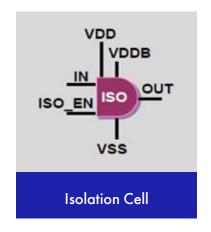

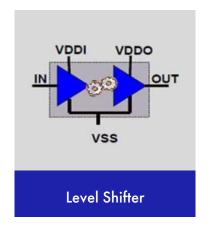

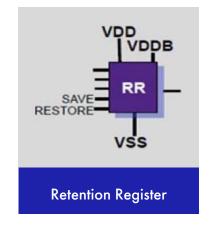

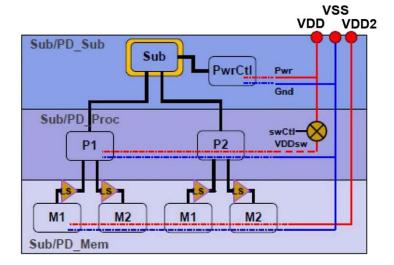

### **UPF** — Universal Power Format

#### create\_supply\_port

create\_supply\_port VDD -direction in create\_supply\_port VSS -direction in

#### create\_supply\_net

create\_supply\_net Pwr -domain PD\_Sub

create\_supply\_net Gnd -domain PD\_Sub

#### connect\_supply\_net

connect\_supply\_net Pwr -ports {VDD}

connect\_supply\_net Gnd -ports {VSS}

### Упрощенный маршрут проектирования для ASIC

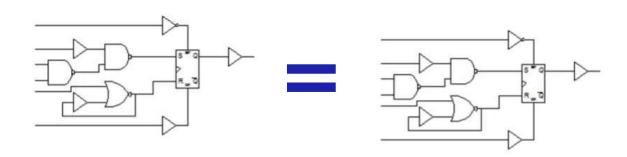

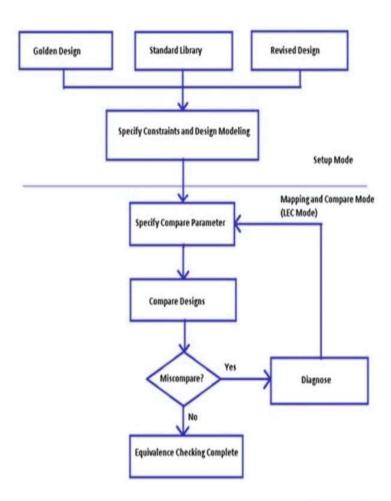

### LEC — Logic Equivalence Checking

- Deductive verification

- Model checking

- Equivalence checking

- Simulation performed on the model

- Emulation, prototyping product + **enviroment**

- Testing performed on the actual product (manufacturing test)

Formal verification

### Упрощенный маршрут проектирования для ASIC

### ASIC разработка

#### ASIC разработка

#### Фронтенд (FE):

- Микроархитектура и разработка

- Написание RTL

- Отладка на симуляции

- Отладка синтеза

- Отладка тайминга

- Отладка изделия

#### FPGA prototyping и валидация:

- Прототип ASIC на FPGA

- Проверка пользовательских сценариев и работы с различными оконечными устройствами

- Загрузка Linux, отладка драйверов и софта

- BenchMarking

#### Верификация

- Создание тестбенча

- Создание плана тестирования (HVP)

- Написание воздействий на отлаживаемое устройство (DUT)

- Анализ покрытия

#### Бэкенд (ВЕ):

- Синтез

- Проверка логической эквивалентности (LEC)

- Размещение и разводка (PnR)

- Формирование GDS

Milestones

Разница в архитектуре FPGA и ASIC

FPGA vs ASIC: достоинства и недостатки

Маршрут проектирования FPGA vs ASIC

### Поговорим о нашем курсе

Что нужно чтобы попасть на наш курс

### Внутренний курс FPGA to ASIC

- Общий маршрут проектирования ASIC

- Процесс интеграции IP

- Построение деревьев синхронизации и сброса

- Статические проверки качества кода (Lint, CDC, RDC)

- Статический временной анализ (STA)

- Формирование констрейнов (.sdc)

- Проведение LEC-анализа

- Проектирование схем с низким энергопотреблением (Power-Aware Design)

- Методика совместной разработки на основе системы контроля версий GitLab+Git

- Вставка тестовых структур (DFT)

#### Чему вы научитесь?

На курсе вы познакомитесь с теоретическими и практическими аспектами ASIC-проектирования систем на кристалле, ведь маршрут их проектирования требует детального понимания как физически устроена микросхема и каким образом цифровая логика должна быть адаптирована под ограничения техпроцесса и параметров производства.

Программа курса составлена на основе опыта и практики наших коллег, которые уже прошли путь от FPGA к ASIC дизайну. Изучение следующих тем даст вам фундаментальный набор практических навыков, необходимых специалисту по разработке систем на кристалле.

20

Milestones

Разница в архитектуре FPGA и ASIC

FPGA vs ASIC: достоинства и недостатки

Маршрут проектирования FPGA vs ASIC

Поговорим о нашем курсе

Что нужно чтобы попасть на наш курс

### Внутренний курс FPGA to ASIC

#### Что вам надо знать?

#### Мы рассчитываем, что вы:

- Понимаете синхронную передачу и дерево клоков

- Отлично знаете Verilog HDL

- Уверенно работаете с форматом .sdc

- Понимаете техники CDC

- Владеете навыками отладки схем на симуляторе и FPGA

- Уверенно используете системы контроля версий

- Владеете Linux

- Знакомы со скриптовыми языками (Tcl, Bash, Make, Python)

- Пишете понятный код, доступный для наследования

- Имеете опыт написания документации на разрабатываемый блок

#### Отлично, если вы:

- Знакомы с SystemVerilog и синтезируемым подмножеством SystemVerilog. Применяете конструкции языка для сокращения времени разработки и минимизации количества ошибок

- Имеете опыт работы с современными FPGA, Xilinx предпочтителен, хорошо знаете EDA (Vivado)

- Обладаете компетенциями в области статического анализа кода с использованием соответствующих тулов (JG, Spyglass и др.)

- Имеете навыки валидации CDC, RDC

- Используете Git для контроля версий

- Программировали на С (ANSI)

- Знаете английский на уровне, достаточном для переписки с техподдержкой

### Другие возможности для обучения

### SOC DESIGN CHALLENGE

#### 21-23 апреля 2023 года

YADRO проводит инженерный хакатон SoC Design Challenge

Вы сможете прокачать навыки проектирования современных микропроцессоров на базе архитектуры RISC-V и попробовать свои силы в решении практических задач маршрута проектирования системы на кристалле (CнК) по четырем направлениям. За отведённое время вам предлагается решить один из предложенных кейсов. Работы будут оценивать экспертыразработчики YADRO Microprocessors, аспиранты и преподаватели МИЭТ.

#### Регистрация открыта до 7 апреля!

**S**yntacore

### Другие возможности для обучения

### Стажировка

#### Стажировка в YADRO

Мы всегда рады видеть в команде талантливых молодых студентов, которые хотят построить карьеру инженера. Приглашаем тебя на долгосрочную и оплачиваемую стажировку, где ты станешь частью группы технологических компаний YADRO. Это возможность получить опыт работы в инженерной компании, проявить себя и войти в профессиональное сообщество.

#### Кого мы ждем в нашу команду?

Студентов очной формы обучения

Бакалавриат / Специалитет — 3 курс и старше

Магистратура — 1 и 2 курс

### Истовый инженер

engineer.yadro.com

#### Лекториум

Записи лекций от признанных спикеров: ведущих практикующих инженеров и учёных

#### Статьи

Научно-познавательные, инженернокругозорные темы

#### Читателям

Образовательный и познавательный контент, позволяющий погрузиться в инженерную культуру

#### Авторам

Поддерживаем создание материалов, популяризующих инженерные профессии. Пишите на experts@yadro.com

Генеральный партнёр конференции FPGA-Systems 2023.1

## **Delta**Design

Первая современная отечественная САПР, реализующая сквозной цикл проектирования печатных плат

# tech@exponenta.ru exponenta.ru

Генеральный партнёр конференции FPGA-Systems 2023.1

- Технические консультации

- Подбор инструментов

- Обучение специалистов

- Работа на заказ

yadro.com

Генеральный партнер конференции FPGA-Systems 2023.1

## Информационные партнёры

# Где найти FPGA комьюнити?

fpga-systems.ru

t.me/fpgasystems <=> @fpgasystems

admin@fpga-systems.ru