Вебинар: Vitis – новейшая среда высокоуровневой разработки от Xilinx и аппаратные платформы Versal и Alveo.

На вебинаре вы познакомитесь с новой средой разработки Vitis, в которой реализована парадигма высокоуровневого проектирования, и с двумя новыми аппаратными платформами от Xilinx – Versal и Alveo, для которых разработка в среде Vitis наиболее эффективна.

Платформа Versal является системой на кристалле, выполненной по 7 нм технологическому процессу и обладающей рядом аппаратных решений, примененных впервые. Это делает её идеальной платформой для проектирования оконечных и автономных устройств.

Ускорительные платы Xilinx Alveo – мощное средство повышения эффективности рабочих станций и серверных/облачных решений, обеспечивающее существенные преимущества при решении вычислительных задач при одновременном уменьшении энергопотребления. В качестве практического примера будет продемонстрирована биномиальная модель ценообразования опционов в среде Vitis с оптимизацией кода под ускорители Alveo.

Вебинар предназначен как для разработчиков для ПЛИС и СнК, желающих повысить свою продуктивность с помощью средств высокоуровневого проектирования, так и для программистов, ищущих возможности повышения производительности своих компьютерных систем с помощью адаптируемых аппаратных ускорителей Xilinx Alveo.

Программа вебинара:

- технология высокоуровневого проектирования (HLS) – что это такое

- сравнение с традиционными средствами разработки для ПЛИС, преимущества, особенности и недостатки HLS

- Xilinx Vitis – единая среда высокоуровневого проектирования для ПЛИС и СнК Xilinx

- целевые платформы Vitis (Vitis Target platforms)

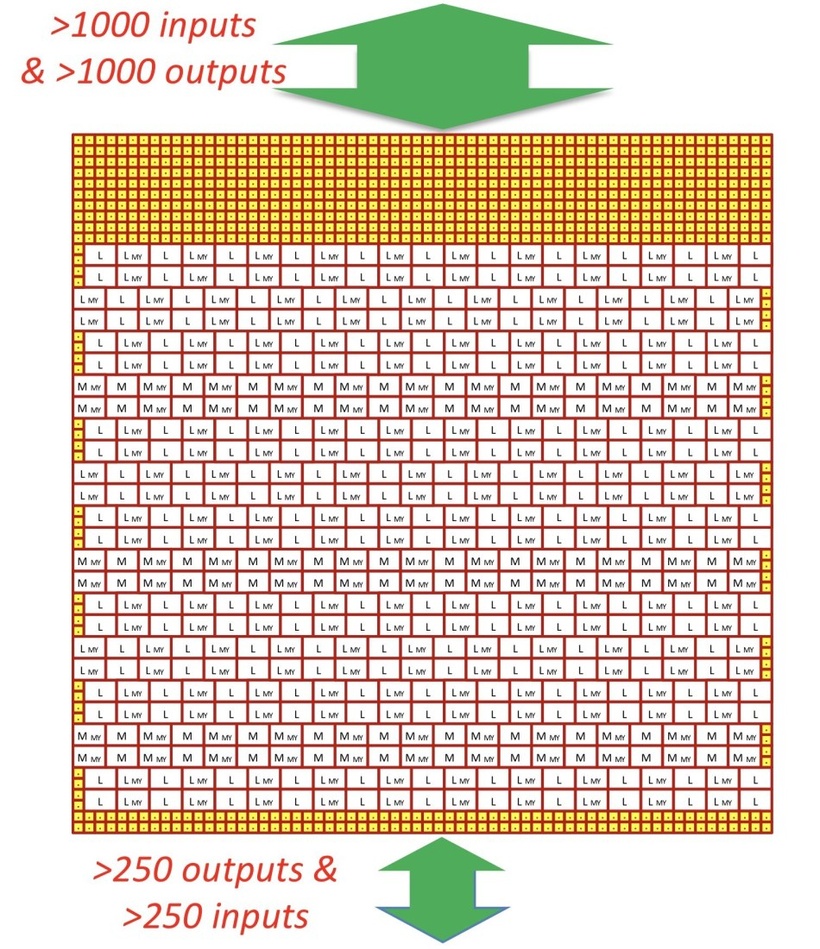

- системы на кристалле Versal – назначение, номенклатура, архитектурные особенности

- обзор серии ускорителей Xilinx Alveo и области их применения

- вертикальная интеграция в Vitis: реализация нейронных сетей на платформах Versal и Alveo

- демонстрация Vitis: реализации биномиальной модели ценообразования опционов с оптимизацией кода под ускорители Alveo.

Ведущие вебинара:

Владимир Викулин, инженер по применению Xilinx (FAE)

Виталий Хасанов, программист

Вебинар состоится 31 марта в 14:00 (мск).

Участие в вебинаре бесплатное, после предварительной регистрации.

Любые вопросы по теме вебинара или любые другие вопросы по продукции Xilinx задайте Владимиру Викулину по адресу fpga@macrogroup.ru или по телефону 8 (800) 333-06-05 доб. 278.