Статьи участников нашего сообщества

Модуль: Каталог статей

Основы статического временного анализа. Часть 3: Source Synchronous Input Delay Constraint.

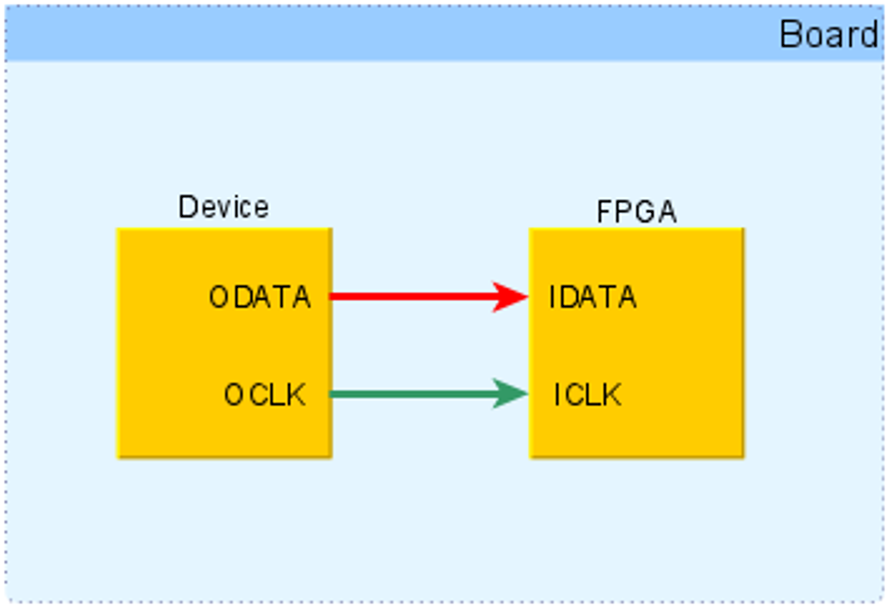

В статье представлен временной анализ передачи сигналов в FPGA из внешнего устройства. Рассмотрены теоретические основы анализа для трех различных вариантов выравнивания данных относительно тактового сигнала. Также разобраны два практических примера создания временных ограничений.

4058

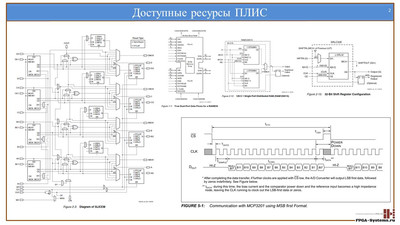

Что внутри ПЛИС или то, о чем не говорят в обучающих видео

LUT-Привет!

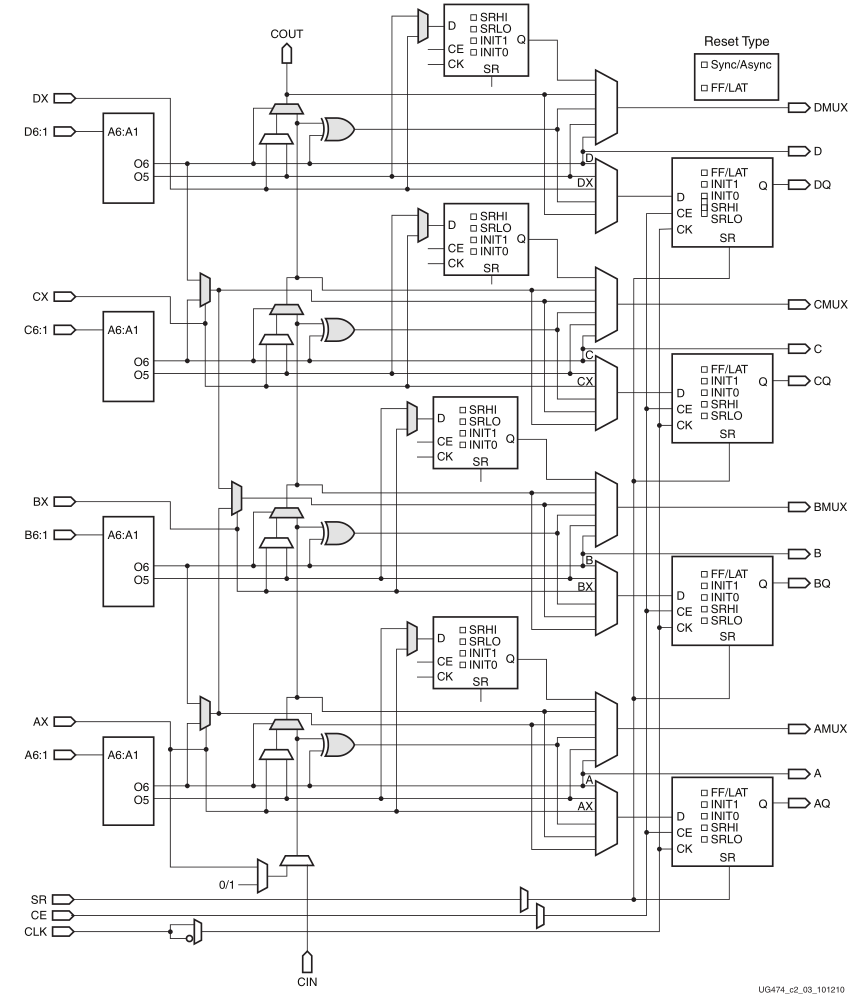

Часто в роликах на ютубе или в различных статьях о том «Что же такое ПЛИС?» приводят одну и ту же концепцию ее построения, то есть ПЛИС изображают как набор конфигурируемых логических блоков, соединенных между собой матрицей соединений или интерконнектами.

С одной стороны, это верно, именно так и устроены самые простые представители программируемых логических микросхем, но сегодня ПЛИС – это нечто более сложное и в рамках этой статьи мы разберемся из чего же на самом деле состоят современные FPGA.

7213

0

Основы статического временного анализа. Часть 2.2: System Synchronous Output Delay Constraint.

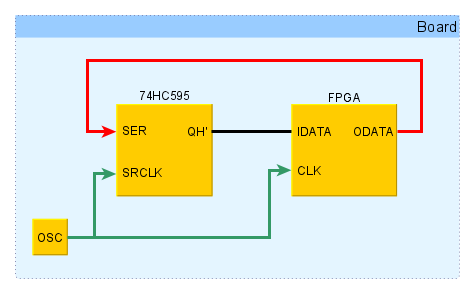

Статья является продолжением серии статей по временным ограничениям в FPGA. Главная цель – познакомить начинающих разработчиков с основами статического временного анализа. Далее будет рассмотрен анализ передачи данных из FPGA во внешнее устройство и показано два способа создания ограничений для выходных сигналов.

4475

6

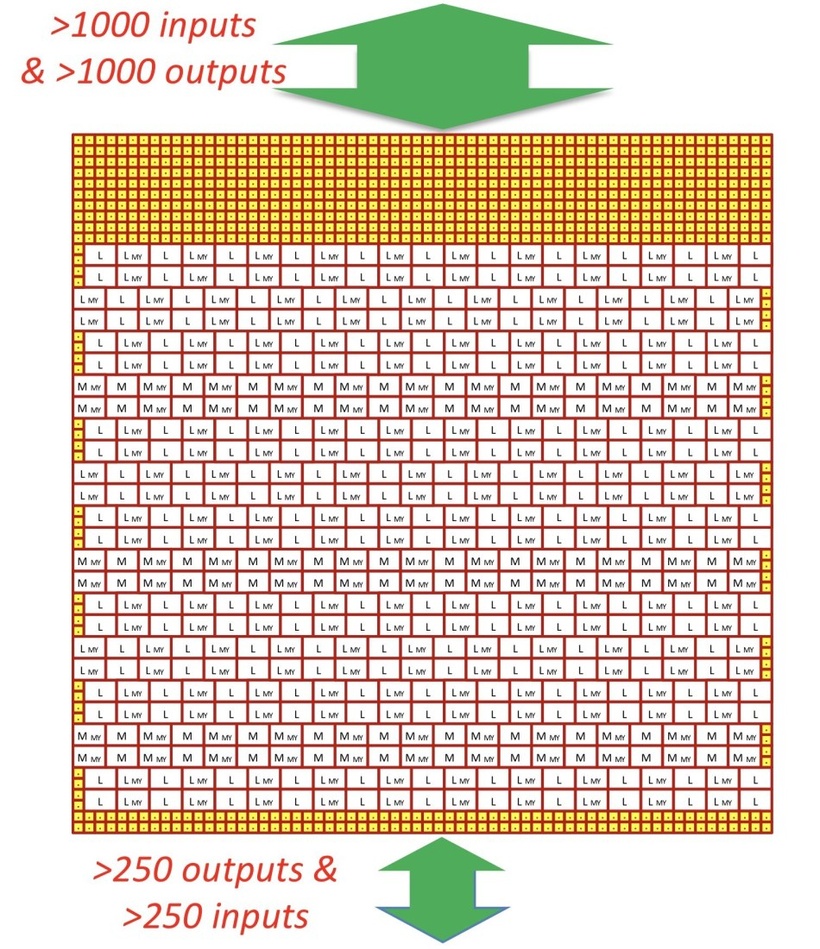

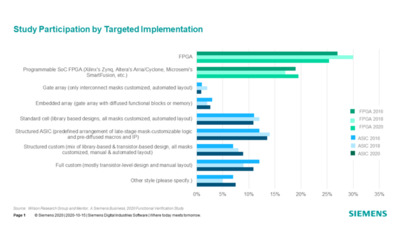

Технология встроенных FPGA (eFPGA): прошлое настоящее и будущее

Наконец-то пришло время для встроенных ПЛИС (eFPGA), и это видно по тому, как они используются в разработках, обслуживающих беспроводную инфраструктуру, системы искусственного интеллекта (ИИ), умные хранилища данных и даже приложения, где ключевую роль играет стоимость конечного изделия. Точно так же, как процессор или DSP, eFPGA могут быть частью системы на кристалле (SoC), которая динамически реконфигурируется, имея для этого аппаратную логику размером от 1000 до 500 000 таблиц истинности (LUT - look-up table).

3163

2

Реализация базовых компонентов ЦОС: КИХ фильтр

В данной статье рассматриваются особенности реализации одного из базовых компонентов цифровой обработки сигналов – фильтра с конечной импульсной характеристикой

4708

2

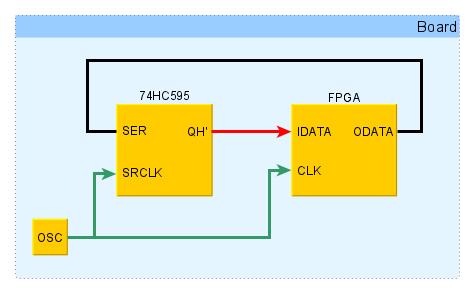

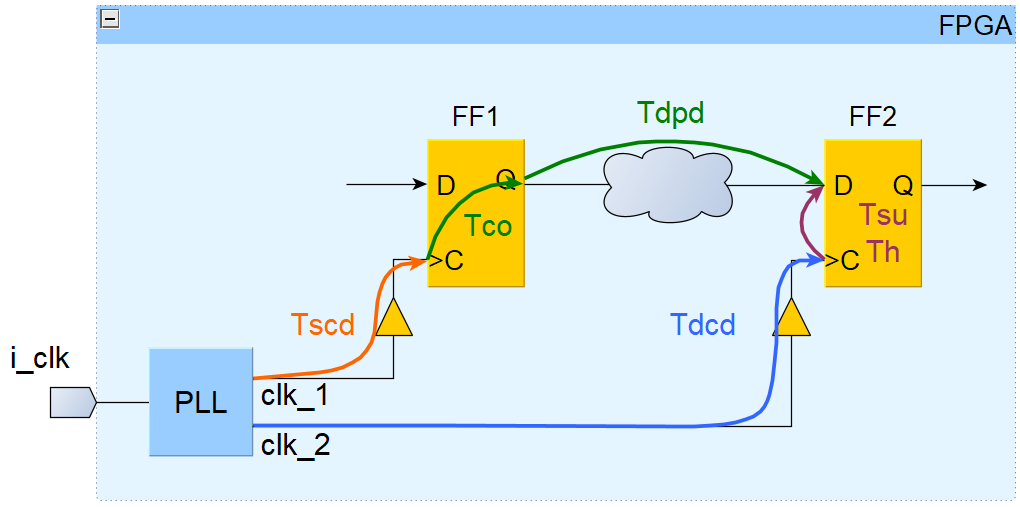

Основы статического временного анализа. Часть 2.1: System Synchronous Input Delay Constraint.

Статья является продолжением серии статей по временным ограничениям в FPGA. Главная цель – познакомить начинающих разработчиков с основами статического временного анализа. Далее будет рассмотрен анализ передачи данных в FPGA из внешнего устройства и показаны два способа создания ограничений для входных сигналов.

5779

12

1