Статьи участников нашего сообщества

Модуль: Каталог статей

Поточное вычисление двоичного логарифма

В статье рассматриваются варианты реализации поточного вычисления двоичного логарифма, приводятся результаты измерения точности и ресурсоёмкости для ПЛИС Artix-7 и синтезатора Vivado 2020.2. Было протестировано 3 алгоритма вычисления log2(x) с некоторыми вариациями.

3909

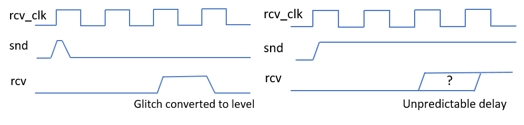

Верификация проблем с пересечением тактовых сигналов в ПЛИС с помощью ALINT-PRO

Предположим, у вас есть одна или несколько ПЛИС, на которые подаются разные тактовые сигналы для отправляемых и принимаемых данных (назовем их «клоки», пусть будет snd_clk для отправки данных и rcv_clk для приема этих данных). Что будет, если эти сигналы не синхронизованы, то есть «плавают» друг относительно друга?

3374

6

Статическое в SystemVerilog

В данной статье мы рассмотрим отличия статических и автоматических переменных и функций. Мы увидим, что понятие “статический” имеет различные значения для модулей и классов, разберёмся, почему это так, и научимся выбирать нужный нам вариант.

Говорить будем преимущественно о симуляции, а также рассмотрим один пример синтеза.

6688

8

Стратегии оптимизации HDL-кода и синтезатора нетлиста для FPGA

В статье будет рассмотрена работа синтезатора нетлиста, его возможности по оптимизации кода и трудности, с которыми он может столкнуться. Показаны две техники написания кода логических схем на Verilog в зависимости от преследуемых целей оптимизации проекта на этапе синтеза. А также разбор некоторых настроек синтезатора Xilinx Vivado, которые призваны пытаться оптимизировать логическую схему за разработчика. В конце мы возьмём модуль, который попробуем привести к рабочему состоянию исключительно за счёт возможностей синтезатора.

5150

1

Правила для первого журнала, полностью посвященного проектированию на FPGA

Стань актором для FSM :: FPGA-Systems Magazine

2203

0

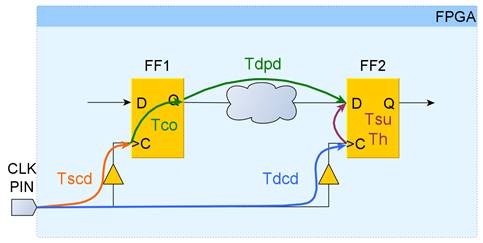

Основы статического временного анализа. Часть 1: Period Constraint.

Статья является первой из планируемой серии статей по временным ограничениям в FPGA. Основная цель – познакомить начинающих разработчиков с основами статического временного анализа. В этой статье будет рассмотрен анализ самого простого случая – передача данных между двумя последовательными элементами внутри FPGA с общим тактовым сигналом. Показан вывод уравнений временного анализа и продемонстрировано их применение анализатором Vivado.

12757

8

Вычисление двоичного логарифма итерационным методом на ПЛИС

Вниманию читателя предлагается алгоритм вычисления логарифма по основанию 2, предоставляется исходный код RTL-блока, анализируется вычислительная точность и ресурсоемкость реализации

6507

0

2