Использование Catapult HLS для SW/HW разработки микросхемы ИИ ускорителя в Harvard University

Аннотация

Замедление закона Мура в сочетании с растущей популярностью машинного обучения привело к появлению чипов с ориентированной на приложения архитектурой, поскольку простого масштабирования кремния уже недостаточно для достижения желаемых показателей производительности и мощности. Чтобы продолжать повышать энергоэффективность, разработка системы-на-кристалле претерпевает стремительный рост сложности проектирования.

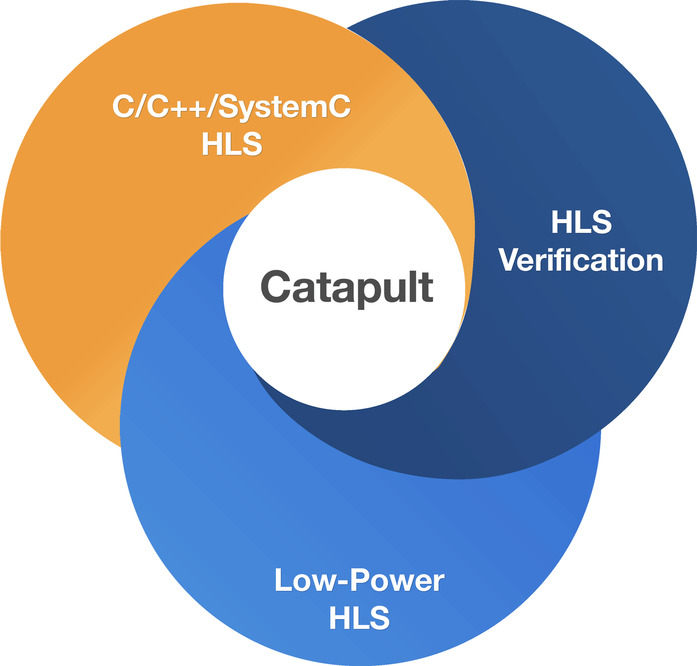

На этом вебинаре мы прольем свет на гибкую методологию совместного проектирования алгоритмов, аппаратного обеспечения и верификации, основанную на высокоуровневом синтезе (HLS - High-Level Synthesis ), которая позволила нам на порядки сократить усилия по разработке СБИС трех поколений со множеством ИИ ускорителей.

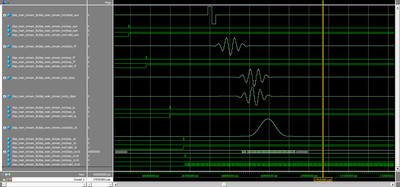

Мы поделимся опытом, полученным в результате разработки высокопроизводительной цифровой СБИС (ускорителя для обработки естественного языка (NLP)), спроектированной с помощью Catapult HLS. Его использование позволило нам эффективно замкнуть цикл проектирования между программным моделированием приложения и аппаратной реализацией.

Наконец, мы упомянем некоторые проблемы HLS, с которыми мы столкнулись, предложим рекомендации по их устранению, и расскажем о дальнейшем улучшении пользовательского опыта использования HLS и производительности проектирования ASIC.

В рамках вебинара мы рассмотрим:

- проверенные методологии, позволяющие быстро и правильно спроектировать ИИ ускоритель с помощью HLS;

- подходы к использованию HLS в верификации;

- проблемы HLS, с которыми мы столкнулись;

- преодоление существующих ограничений инструментов высокоуровнего синтеза.

Целевая аудитория:

- все кому интересна тема разработки ASIC с использованием HLS;

- RTL разработчики и верификаторы.

Вебинар состоится во вторник, 8-февраля-2022

Время проведения: 10:00 AM Pacific Standard Time (21:00 – 22:00 Мск)