Архив новостей из мира FPGA

Вышел новый набор статей по работе c Zynq для самых маленьких

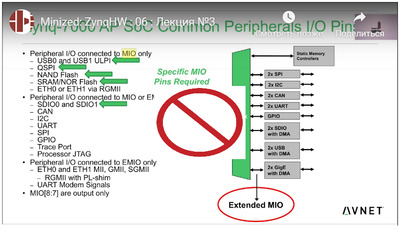

Статьи адресованы тем, кто не имеет опыта работы с Xilinx Zynq но хотел бы с чего-то начать. В этом цикле статей последовательно и подробно изложены ответы на вопросы:

7872

Тренинг по Chisel

Вы когда-нибудь слышали про chisel? Если вы читаете наш телеграм чат - то наверное да. А вот планировали ли вы развиваться в этом направлении и пытаться его изучать? ... Читать дальше »

6257

0

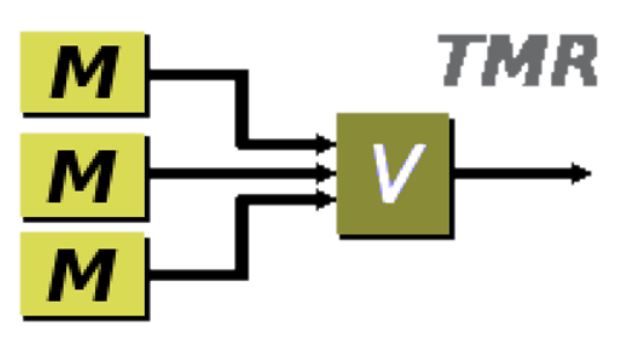

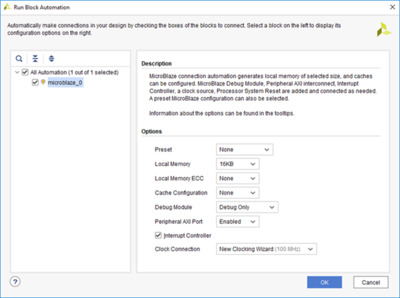

Реализация тройного модульного резервирования (TMR) на MicroBlaze

Небольшое руководство о том, как разместить 3 софт-процессора MicroBlaze на отладочной плате Nexys 4 DDR FPGA (Xilinx Artix 7 FPGA) и затем реализовать тройное модульное резервирование для управления GPIO, используя IP-блок Triple Modular Redundancy (TMR) ... Читать дальше »

6414

0

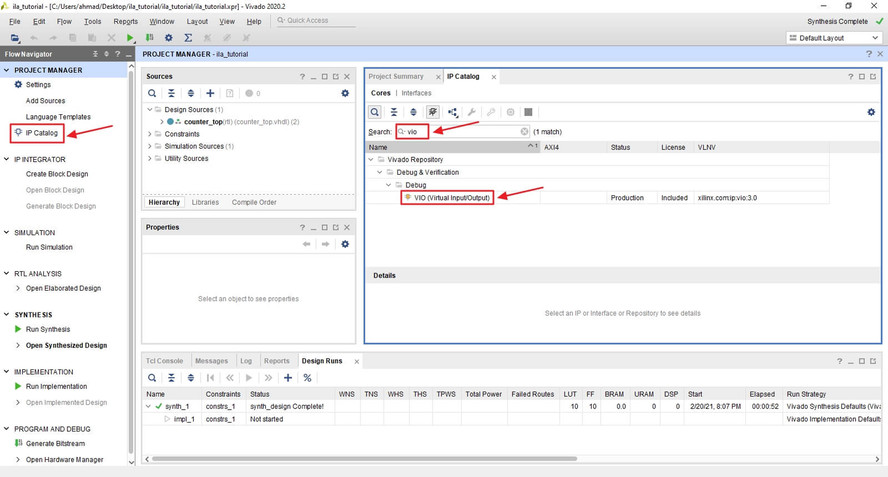

Использование интегрированного логического анализатора (ila) и виртуального ввода-вывода (vio)

На портале vhdlwhiz.com появилось новое большое руководство по работе с инструментами отладки Vivado: интегрированными логическими анализаторами (ILA) и блоком виртуальных портов ввода/вывода (VIO). ... Читать дальше »

7674

0

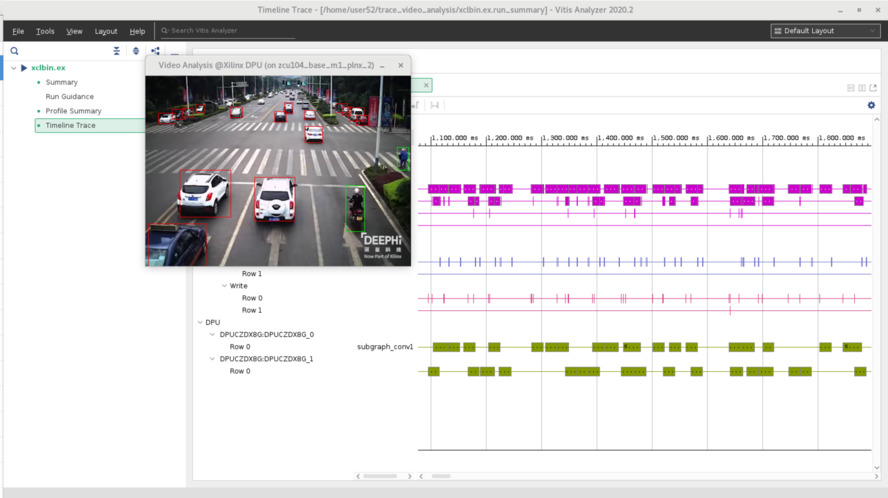

Профилирование примера выполнения нейросети из репозитория Vitis-AI на ZCU104

В состав Vitis-AI (#vitisai) входит программа для профилирования "vaitrace". В видео https://youtu.be/vGu4aaXh6KA показаны необходимые действия для запуска примера с профилированием. Используется Vitis 2020.2 и #ZCU104. ... Читать дальше »

6257

0

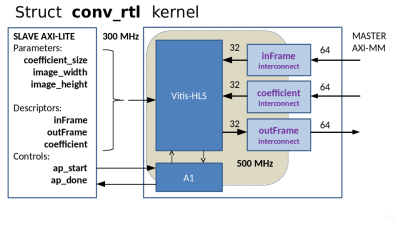

Руководство по преобразованию кернела HLS 300 MHz на RTL 500 MHz для Vivado 2020.2

На конференции FPGA-Systems 2020 был представлен доклад "Особенности реализации RTL и Vivado HLS kernel для ускорителей ALVEO" в котором был представлен учебный пример собранный с использованием Vitis 2 ... Читать дальше »

6418

0

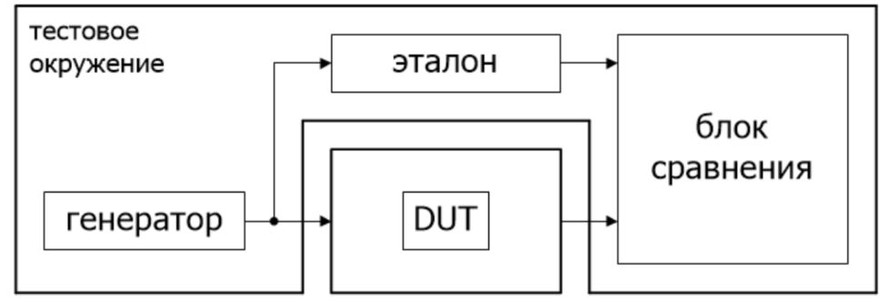

UVM тест таблицы sin/cos

Статья от участников нашего сообщества. В данном руководстве описывается пример построения тестового окружения с использованием UVM для проверки компонента, описанного при помощи HDL. ... Читать дальше »

7305

0

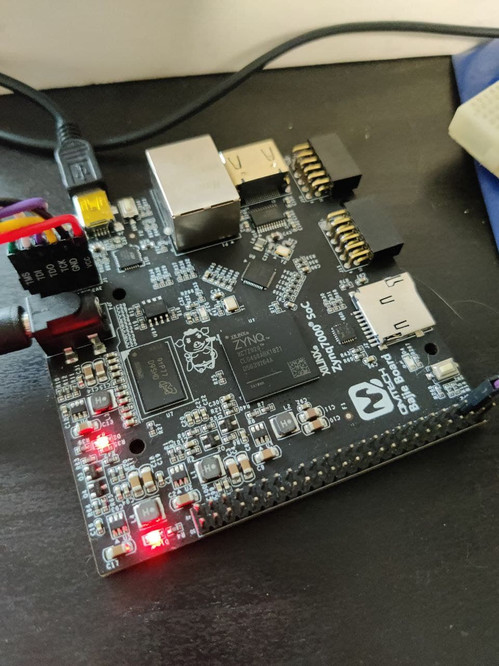

Компьютерное зрение на платфомре ZYNQ

Brian ChengHe Wu предоставил исходный код и видео-инструкцию к своему проекту по работе с Компьютерным Зрением на платформе ZYNQ. По завершению курса вы сможете разработать устройство похожее на Kinect от Microsoft или Intel RealSense. ... Читать дальше »

6504

0

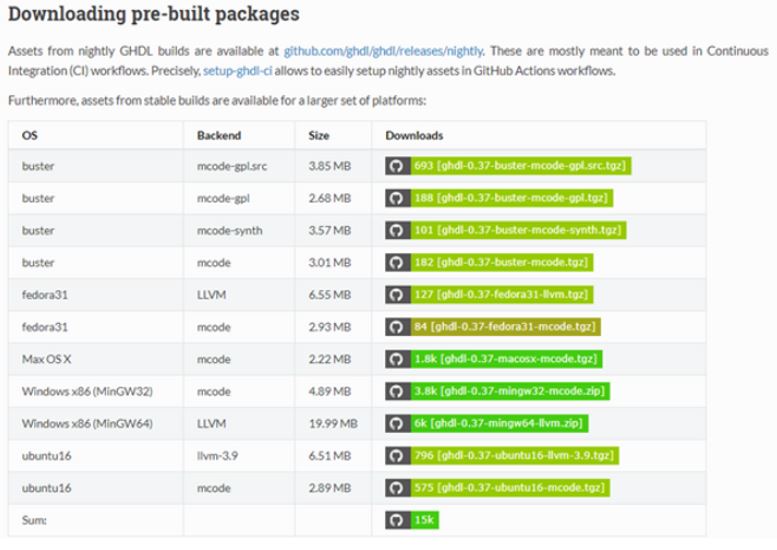

Установка и работа с GHDL для верификации

В блоге Адама тейлора появилось небольшое руководство по началу работы с симулятором с открытым исходным кодом GHDL. Этот симулятор предназначен для верификации проектов, написанных на VHDL. ... Читать дальше »

6279

0

Установка Cocotb на Windows 10 для повышения производительности проверки проектов ПЛИС

На сайте компании DornerWorks появилось руководство по установке и настройке тестового окружения Cocotb. Cocotb (Coroutine Cosimulation Testbench) представляет собой среду/испытательный стенд для проверки RTL кода, используя Python. Она обеспечивает ряд других преимуществ по сравнению с текущими, бол ... Читать дальше »

7053

0 |

0