Статическая и динамическая верификация CDC для IP-блоков на основе AXI4 Stream

Протокол AXI4 Stream используется как стандартный интерфейс для обмена данными между подключенными IP-блоками внутри проектов FPGA. Для пересечения тактовых доменов AXI4 Stream использует коммутаторы, способные передавать данные в другой асинхронный тактовый домен. Альтернативным решением является двухпортовый AXI4 Stream IP-блок, способный менять тактовые домены при маршрутизации пакетов данных.

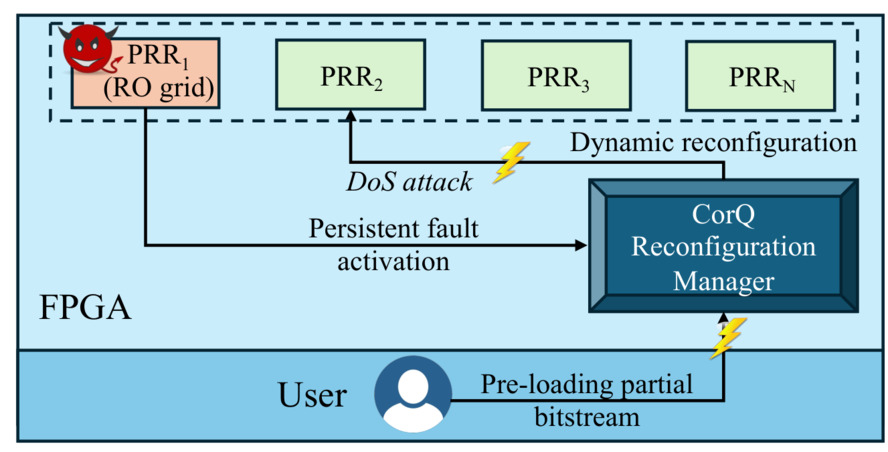

Методы статической и динамической верификации тактовых доменов (CDC) дополняют друг друга, чтобы обеспечить безупречную работу многотактных дизайнов. Плагин ALDEC_CDC содержит 58 правил для проверки качества дизайна, ограничений дизайна и деревьев тактов и сброса. Он также используется для валидации схем синхронизации. Однако методы статической верификации CDC сами по себе не гарантируют полноту задачи верификации CDC. Динамическая верификация CDC имеет решающее значение. Два основных метода динамической верификации CDC включают проверку с использованием утверждений CDC и моделирование случайного введения задержек на пересечении тактовых доменов.

В этом вебинаре мы представим оба метода статической и динамической верификации для верификации CDC AXI4 Stream-based IP. Мы обсудим утверждения CDC, которые автоматически генерируются ALINT-PRO, и продемонстрируем проектирование и использование моделей синхронизаторов с введением случайной задержки.

Программа вебинара:

- Процесс верификации CDC

- Статическая верификация CDC

- Использование утверждений в верификации CDC

- Концепция рандомизации задержек на пересечении CDC в функциональной симуляции

- Обзор протокола AXI Stream

- Проверка порта CDC AXI

- Запуск статических проверок CDC с помощью ALINT-PRO

- Генерация SV-утверждений с помощью ALINT-PRO

- Разработка тестовой оснастки для динамической верификации порта CDC AXI

- Симуляция дизайна с сгенерированными утверждениями CDC

- Симуляция дизайна со случайным введением задержек в моделях синхронизатора

- Выводы

- Вопросы и ответы

Продолжительность вебинара:

- 45 минут презентации/демонстрации в реальном времени

- 15 минут вопросов и ответов

Дата: 17 октября 2024

Время: 4:00 PM – 5:00 PM CEST, 11:00 AM – 12:00 PM PDT

Ссылки на регистрацию: EU, US