Статьи из категории: High Level Synthesis

Категория:High Level Synthesis

Основы AXI часть 7 - Подключение к PS с помощью AXI4-Lite и Vitis HLS

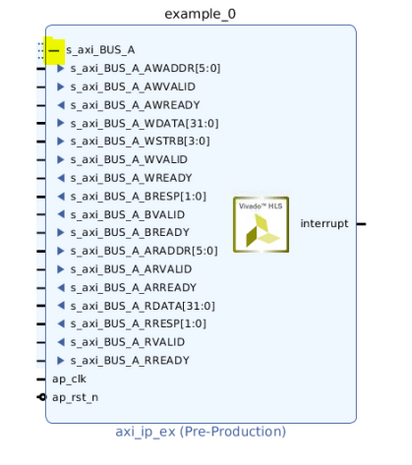

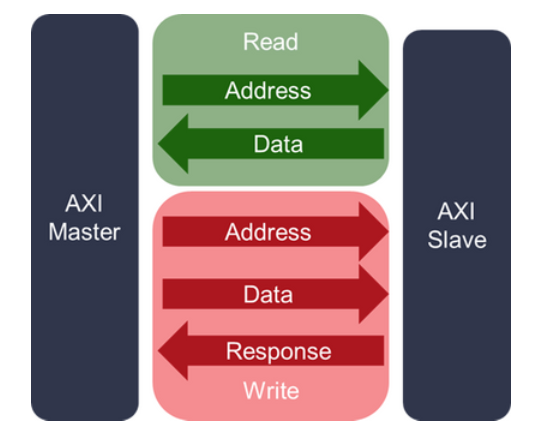

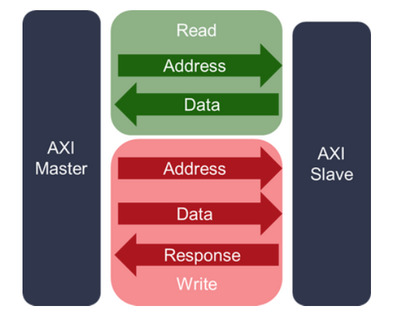

В "Основы AXI часть 6 – Введение в AXI4-Lite в Vitis HLS" мы узнали, как создать IP в HLS с интерфейсом AXI4-Lite с использованием кода на C.

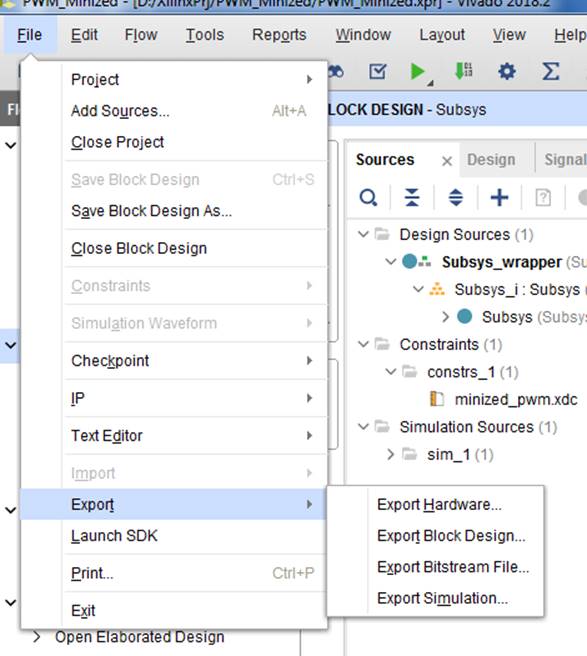

В этом блоге мы узнаем, как экспортировать наше IP, чтобы использовать его в Vivado Design Suite, как подключить его к другим IP ядрам и процессору и как запустить наш проект на плате.

6477

Основы AXI часть 6 – Введение в AXI4-Lite в Vitis HLS (часть 1)

В этом уроке мы будем изучать основы того как создавать пользовательские IP блоки с AXI4-Lite интерфейсом в Vitis HLS.

14327

0

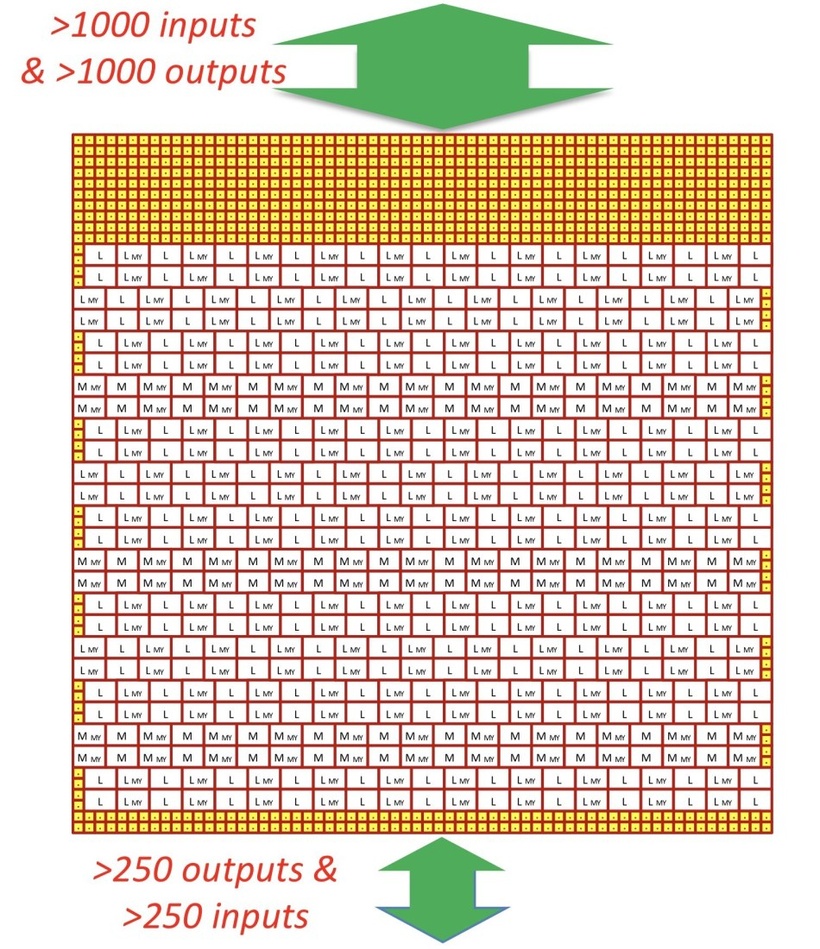

Сможет ли HLS код побить HDL по производительности?

В этой статье мы задействовали инструменты Silexica SLX для FPGA, чтобы оптимизировать промышленное приложение для обнаружения и отслеживания объектов.

В этой статье мы задействовали инструменты Silexica SLX для FPGA, чтобы оптимизировать промышленное приложение для обнаружения и отслеживания объектов.

5233

0

Разработка IP-блока с помощью инструментов высокоуровнего синтеза: HLS Часть 3

В этой части будут показаны основные шаги необходимые для запуска и работы разработанной в прошлых частях системы [1, 2]. Будет показано, как можно использовать API, которое автоматически генерируется для IP-блоков с интерфейсом AXI4-Lite.

5802

0

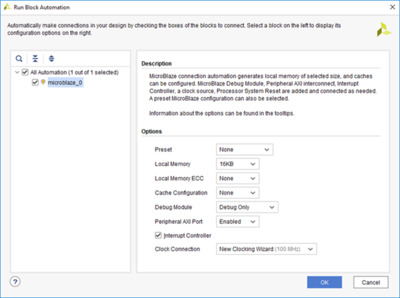

Разработка IP-блока с помощью инструментов высокоуровнего синтеза: HLS Часть 2

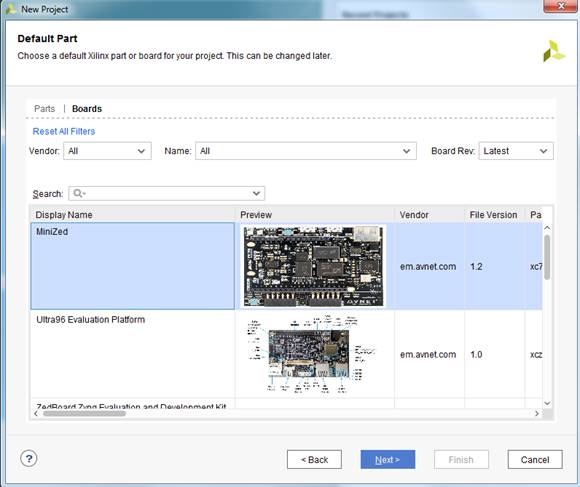

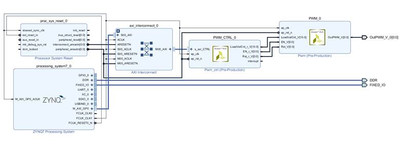

В этой части будут описаны основные шаги для создания блок дизайна (работа в IP Integrator) для разработанных ранее IP-блоков в среде Vivado HLS [1]. Интеграция будет производится для системы-на-кристалле ZYNQ-7000, а конкретно для Zynq установленного на плате MiniZed [2, 3].

9105

0

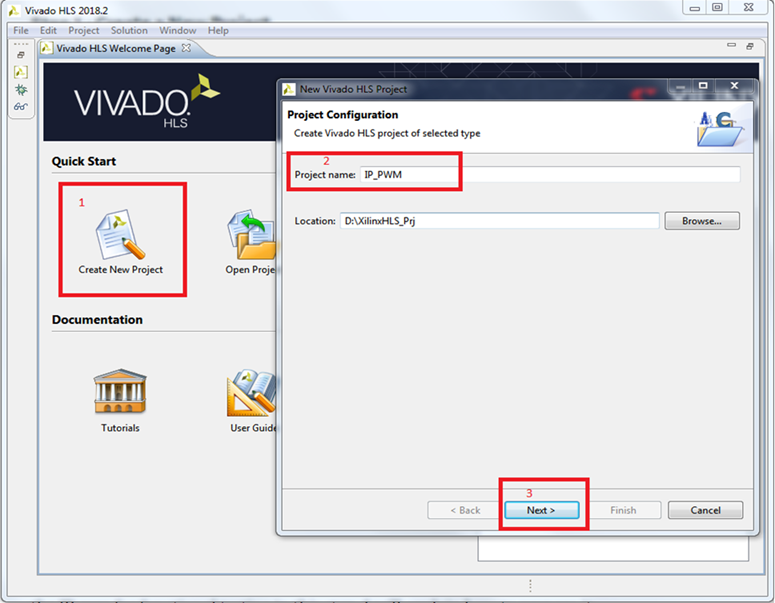

Разработка IP-блока с помощью инструментов высокоуровнего синтеза: HLS. Часть 1

Аннотация

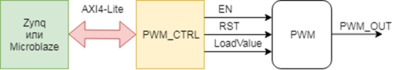

Представляем Вам серию небольших руководств для тех, кто хочет сделать собственный IP-блок для FPGA (фирмы Xilinx) с помощью инструментов выскоуровнего синтеза HLS (High Level Synthesis). Ниже по порядку будут описаны основные шаги такой разработки. В качестве примера будет разработан простейший ШИМ с управлением по шине AXI4-Lite, который будет изменять яркость светодиода на отладочной плате MiniZed.

12688

1

0