Статьи из категории: Познавательное

Категория:Познавательное

FSC - FPGA-Systems Challenge

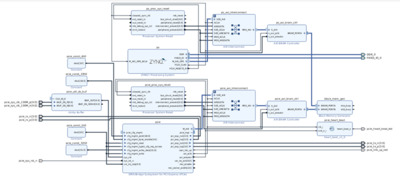

Это небольшой сборник с задачками по работе в Vivado, и больше ориентирован на повышение навыков оптимизации и анализа проектов.

Забудьте про ненавистные VHDL/Verilog/SV!!! В этом челендже они максимально бесполезны.

1547

Найдено 9-ое число Дедекинда и, как вы наверное догадываетесь, не без помощи FPGA

42 цифры создающие историю. Ученые из Университета Paderborn и KU Leuven раскрыли тайну математики десятилетней давности, относящуюся к так называемым числам Дедекинда.

Эксперты по всему миру занимаются поиском 9-го числа Дедекинда с 1991 года. Ученые из университета Paderborn получили точную последовательность чисел с помощью расположенного там суперкомпьютера Noctua. Результаты будут представлены в сентябре на Международном семинаре по булевым функциям и их приложениям (BFA) в Норвегии.

2761

0

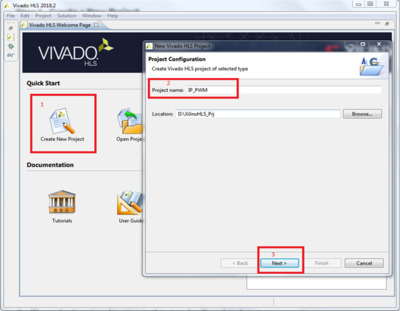

QuickSilicon: платформа с задачами на разработку RTL

Платформа QuickSilicon с задачами на разработку RTL.

1856

0

Долой RTL описание регистров! (перевод)

После почти трех десятилетий, проведенных в EDA бизнесе я до сих пор не могу понять причину, почему многие разработчики микросхем до сих пор продолжают описывать сложные регистровые карты (микросхемы, содержащие сотни регистров и тысячи полей регистров) вручную при помощи RTL. Если вы задаетесь этим же вопросом, то добро пожаловать под кат.

5747

1

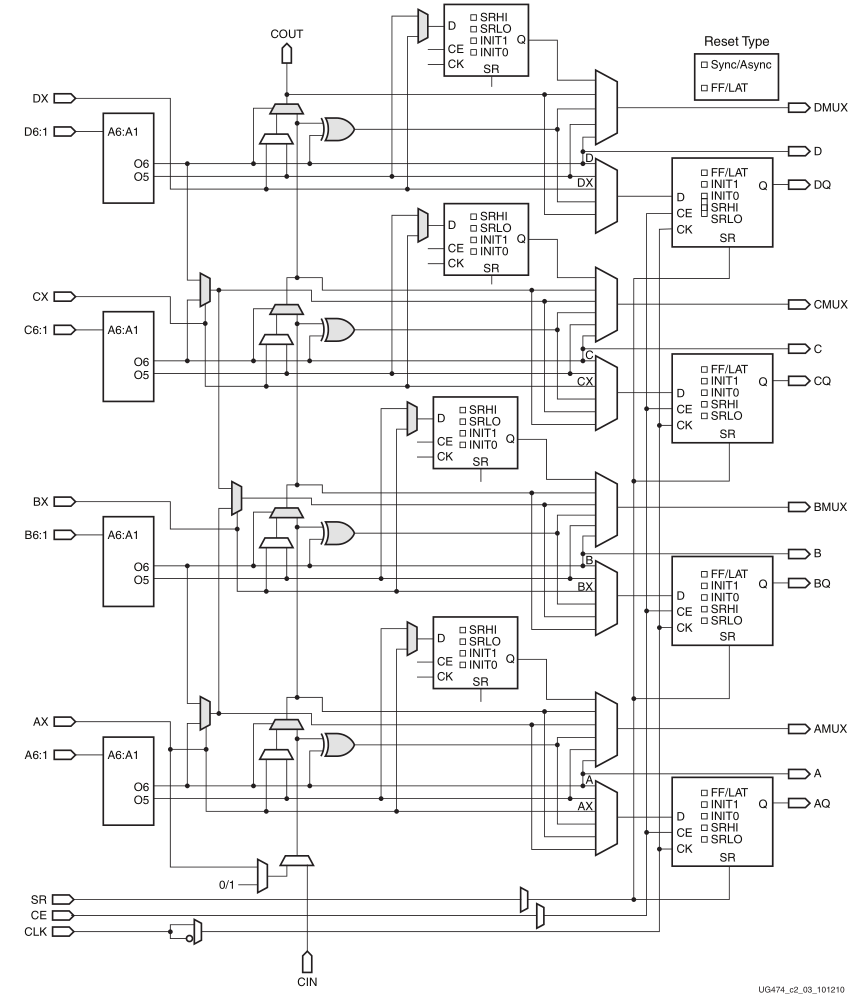

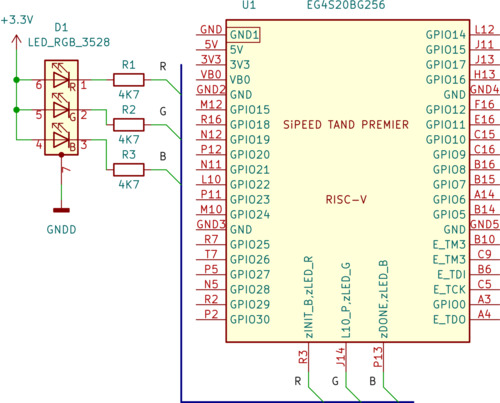

Что внутри ПЛИС или то, о чем не говорят в обучающих видео

LUT-Привет!

Часто в роликах на ютубе или в различных статьях о том «Что же такое ПЛИС?» приводят одну и ту же концепцию ее построения, то есть ПЛИС изображают как набор конфигурируемых логических блоков, соединенных между собой матрицей соединений или интерконнектами.

С одной стороны, это верно, именно так и устроены самые простые представители программируемых логических микросхем, но сегодня ПЛИС – это нечто более сложное и в рамках этой статьи мы разберемся из чего же на самом деле состоят современные FPGA.

10899

0

0