Статьи из категории: Xilinx Vivado

Категория:Xilinx Vivado

FSC - FPGA-Systems Challenge

Это небольшой сборник с задачками по работе в Vivado, и больше ориентирован на повышение навыков оптимизации и анализа проектов.

Забудьте про ненавистные VHDL/Verilog/SV!!! В этом челендже они максимально бесполезны.

1542

ZYNQ SW: EBAZ4205: часть 4 (Vivado 2023)

Продолжение руководства по запуску платы EBAZ4205 на Vivado 2023.2

Начало в 3-й части

10624

7

ZYNQ HW: EBAZ4205: часть 3 (Vivado 2023)

Повторение туториала из Части №1, но и использованием версии Vivado 2023.2.

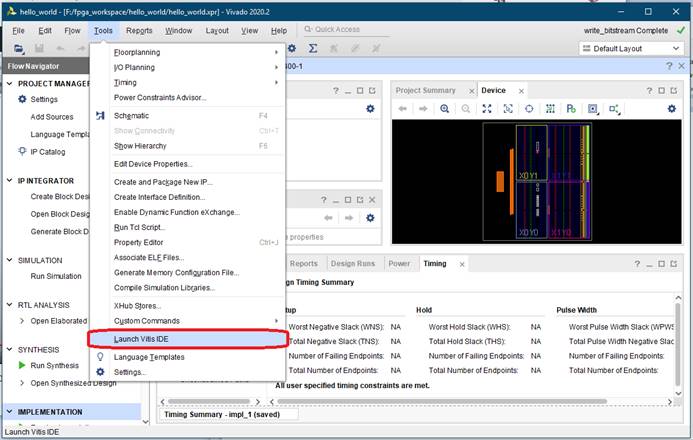

Повторение создание проекта Hello World с выводом текстовой строки в последовательный интерфейс UART, но на плате EBAZ4205. Для этого нужно будет учесть аппаратные особенности этой платы. Так же, отличием этого туториала является использование Vitis вместо более раннего варианта SDK.

10166

5

Стратегии оптимизации HDL-кода и синтезатора нетлиста для FPGA

В статье будет рассмотрена работа синтезатора нетлиста, его возможности по оптимизации кода и трудности, с которыми он может столкнуться. Показаны две техники написания кода логических схем на Verilog в зависимости от преследуемых целей оптимизации проекта на этапе синтеза. А также разбор некоторых настроек синтезатора Xilinx Vivado, которые призваны пытаться оптимизировать логическую схему за разработчика. В конце мы возьмём модуль, который попробуем привести к рабочему состоянию исключительно за счёт возможностей синтезатора.

7726

1

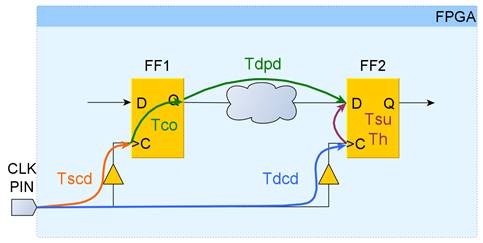

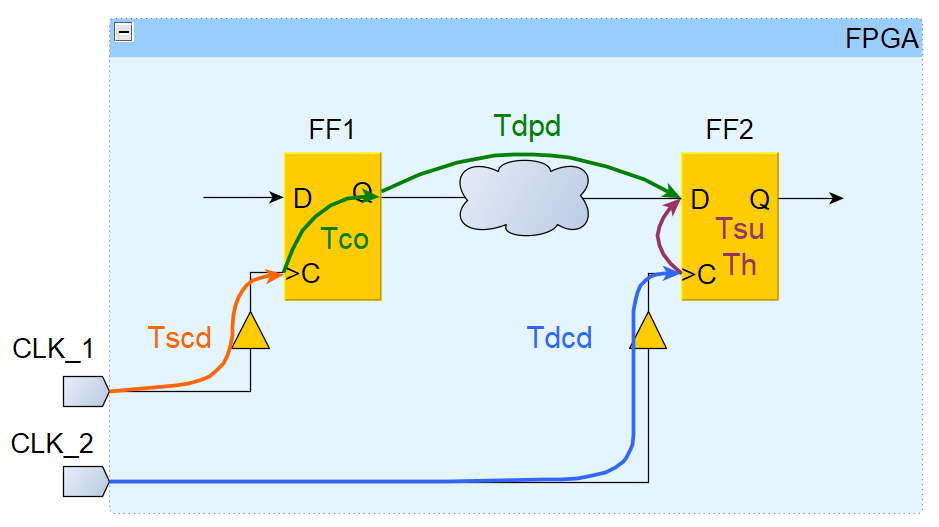

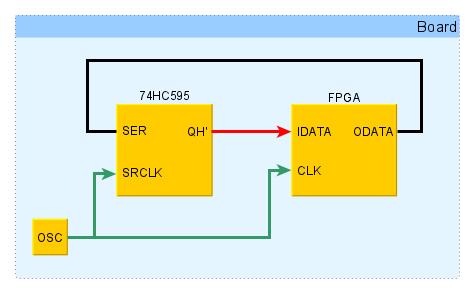

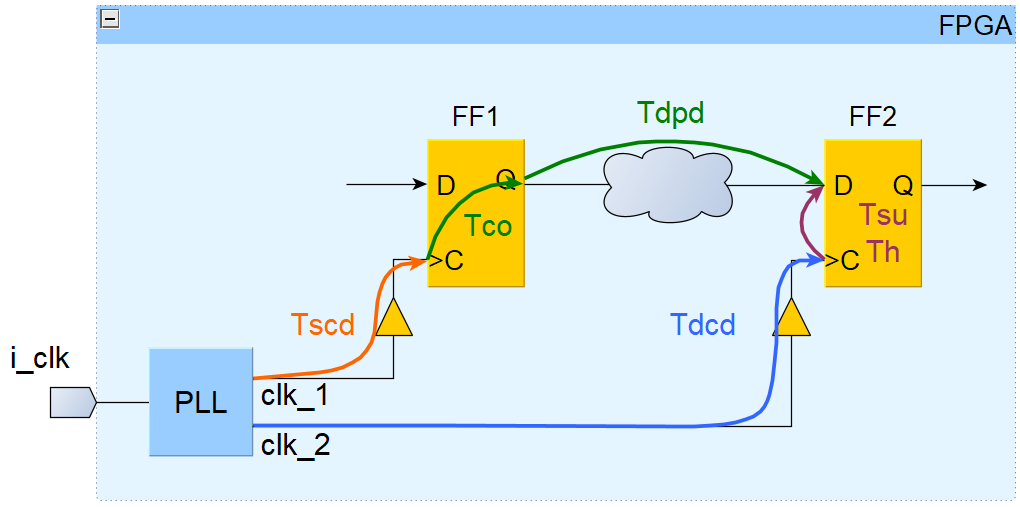

Основы статического временного анализа. Часть 1: Period Constraint.

Статья является первой из планируемой серии статей по временным ограничениям в FPGA. Основная цель – познакомить начинающих разработчиков с основами статического временного анализа. В этой статье будет рассмотрен анализ самого простого случая – передача данных между двумя последовательными элементами внутри FPGA с общим тактовым сигналом. Показан вывод уравнений временного анализа и продемонстрировано их применение анализатором Vivado.

20056

8

ZYNQ SW: EBAZ4205: часть 2 (Vivado 2020)

Продолжение руководства по запуску платы EBAZ4205.

Начало в первой части

14452

1

ZYNQ HW: EBAZ4205: Часть 1 (Vivado 2020)

Цель данного туториала - повторить создание проекта Hello World с выводом текстовой строки в последовательный интерфейс UART, но на плате EBAZ4205. Для этого нужно будет учесть аппаратные особенности этой платы. Так же, отличием этого туториала является использование Vitis вместо более раннего варианта SDK.

26202

0

0