ZYNQ HW: EBAZ4205: часть 3 (Vivado 2023)

Оглавление

- Аннотация

- Приступаем к работе

- Сборка и настройка HW части

- SW часть проекта см часть 4

- Итоги см часть 4

- Ссылки см часть 4

Ссылка на PDF версию в конце статьи

Аннотация

Данный туториал - возвращение к напечатанному в 2021 году туториалу по сборке проекта на Vivado 2020+Vitis. Цель - повторить все инструкции, но с использованием текущей версии Vivado 2023.2.

Цель данного туториала - повторить создание проекта Hello World с выводом текстовой строки в последовательный интерфейс UART, но на плате EBAZ4205. Для этого нужно будет учесть аппаратные особенности этой платы. Так же, отличием этого туториала является использование Vitis вместо более раннего варианта SDK.

Для повторения туториала потребуется:

- Скачать Vivado+Vitis 2023.2 (размер примерно 107 Гб)

- Установить. Поддержка только ZYNQ занимает на диске около 64 Гб (Файлов: 581 815; папок: 73 310)

- Плата EBAZ4205

- Программатор Xilinx

- USB UART преобразователь на базе pl2303 или аналог

- туториал выполнялся на ОС Windows 11

Приступаем к работе

Еще одно отличие этой статьи от серии статей про Minized это использование Vivado 2020.2 и Xilinx Vitis 2020.2 (в отличие от SDK в более ранних версиях)

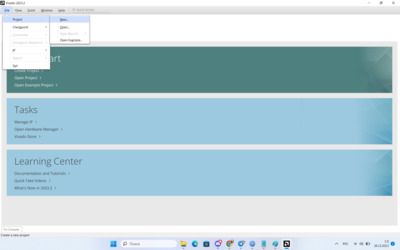

Сборка и настройка HW части

Создаем новый проект и попробуем повторить функционал, который выведет строчку "Hello world" чере UART порт (для того, чтобы это увидеть, нам потребуется переходник USB UART). В таком проекте потребуется настроить по-минимуму аппаратную часть ZYNQ: порт UART, DDR память; и написать прошивку для ядра.

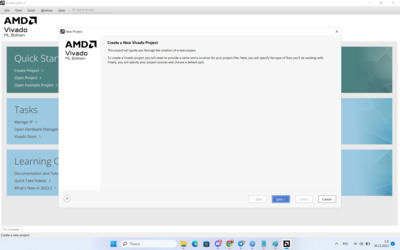

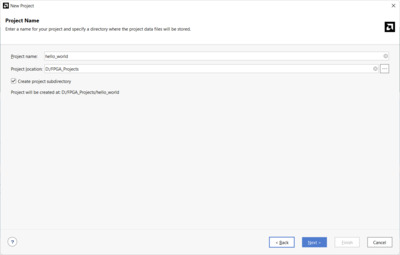

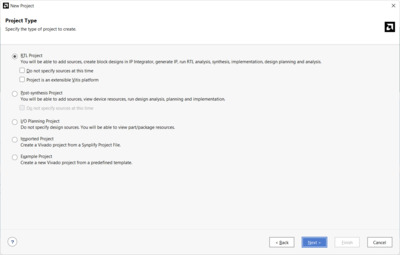

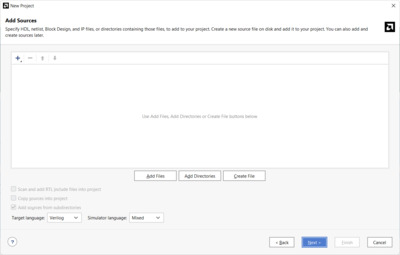

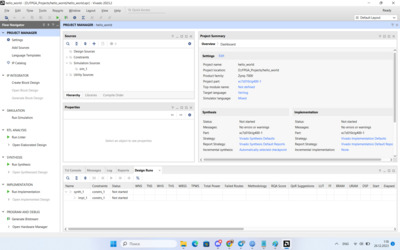

Задаем имя проекта

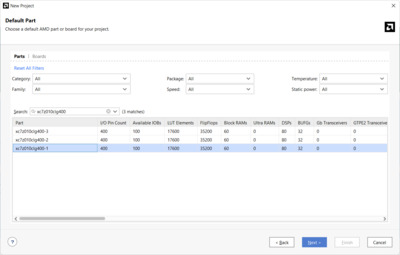

Выберем модель ПЛИС

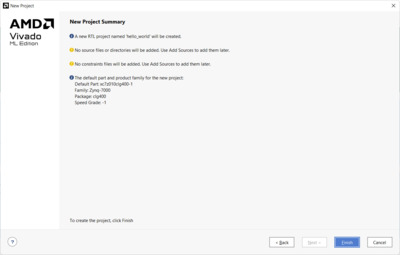

Нажмем Finish

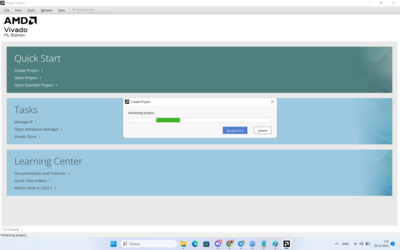

Дождемся инициализации проекта

Готово!

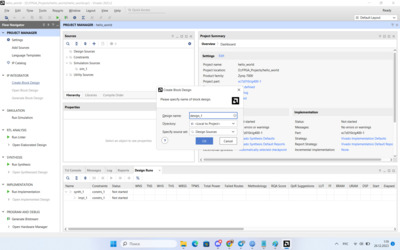

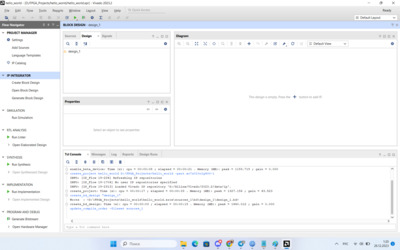

В IP INTEGRATOR создаем блок Create Block Design имя оставлю по умолчанию

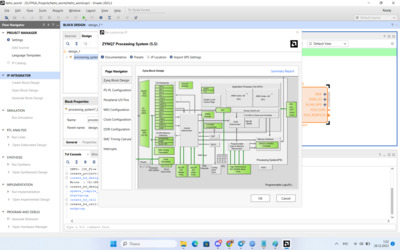

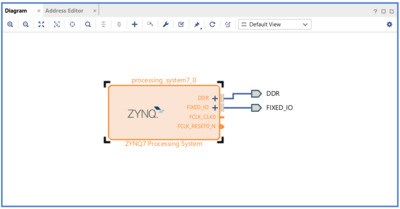

Добавлю систему ZYNQ7 на диаграмму

ZYNQ на диаграмме

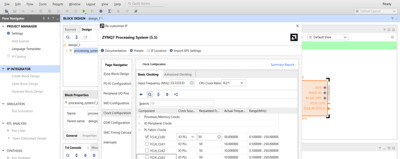

Дважды кликаем по блоку ZYNQ на диаграмме, чтобы перейти в настройки системы ZYNQ

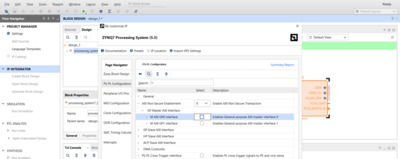

Переходим во вкладку PS-PL Configuration и на всякий случай снимаем галочку

Настроим аппаратные блоки, хотя некоторые могут и не потребоваться.

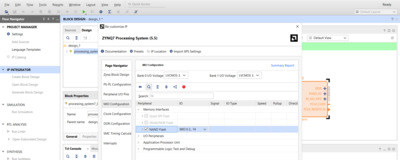

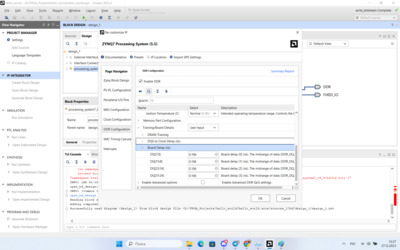

На вкладке MIO Configuration настроим SD и UART1

Если в будущих проектах планируется тактировать PL логику от системы ZYNQ в качестве источника, то это можно настроить во вкладке Clock Cinfiguration выход FCLK_CLK0

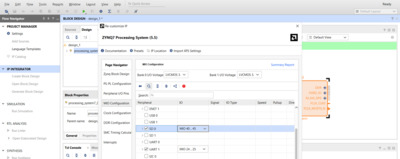

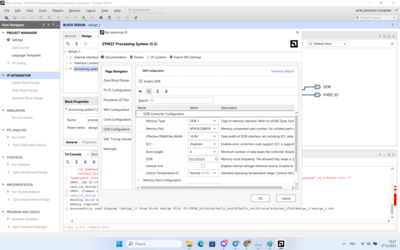

Далее, настроим параметры DDR

Там же параметры задержки

На этом все. Нажимаем "OK".

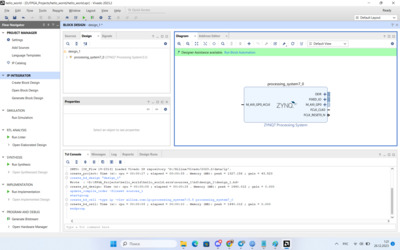

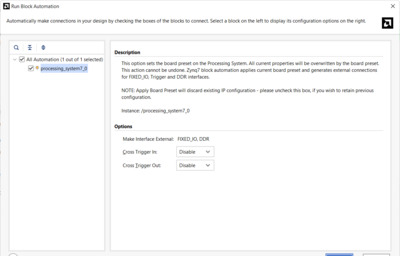

На диаграмме запускаем "Run Block Automation" оставляя параметры по умолчанию и тоже нажимаем "ОК"

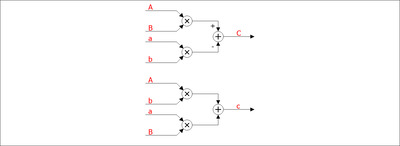

На диаграмме увидим следующее

Сохраняем диаграмму.

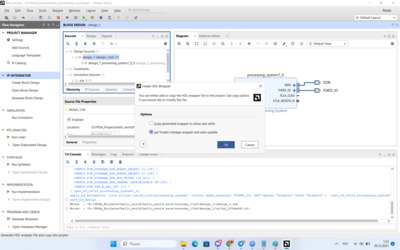

Переходим на вкладку Sources, выбираем диаграмму, создаем wrapper.

Create HDL Wrapper - cоглашаемся, пусть система обновляет файлы в случае изменения дизайна.

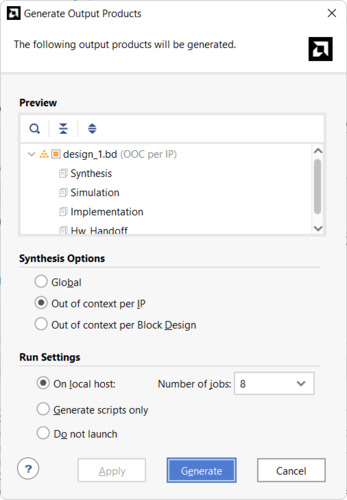

В Generate тоже оставляем все без изменений

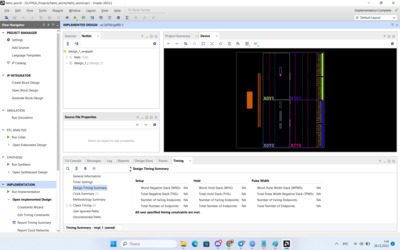

Далее запускаем Run Synthesis, Run Implementation, Generate Bitstream. В итоге можно открыть Implementation Design и посмотреть на него (как на новые ворота)

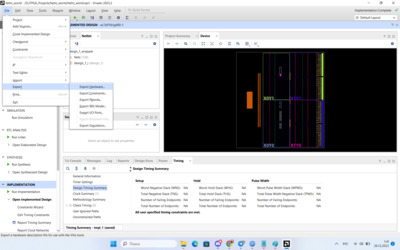

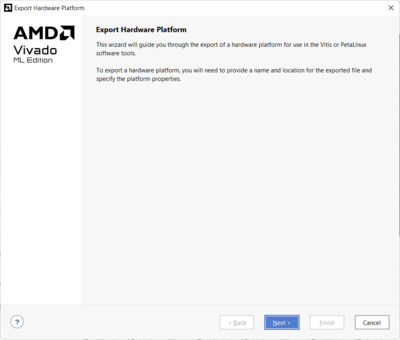

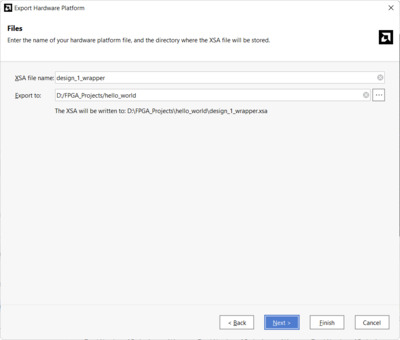

Далее экспортируем полученный результат

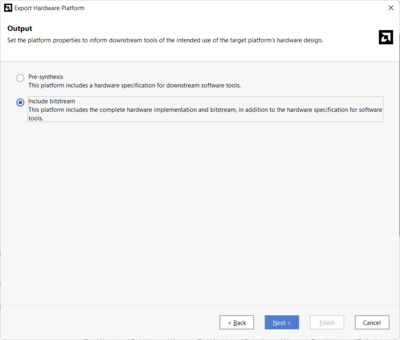

Включая bitstream

Пути и имя не меняем

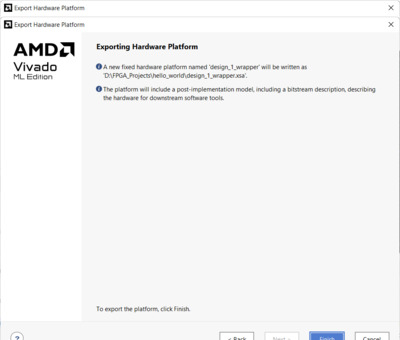

Готово

Мы настроили аппаратную часть, экспортировали ее и готовы к написанию прошивки.

В целом, работа с созданием HW в Vivado 2023.2 не сильно отличается от того, как это было в Vivado 2020.

В следующей части мы пойдем в Vitis IDE, где продолжим разрабатывать программную SW часть проекта.

Продолжение Часть 4