Компания: НИИМЭ

Место работы: г. Екатеринбург

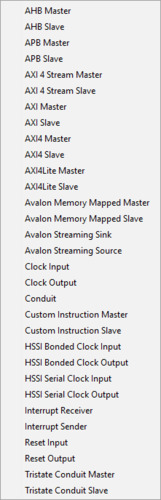

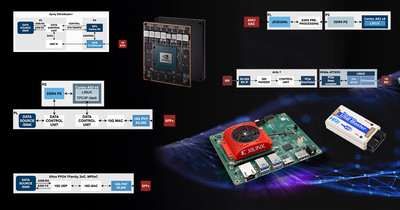

Компания ведёт разработку сложно-функциональных (IP-) и верификационных (VIP-) ядер, а также полноценных систем-на-кристалле под ключ (от идеи до изготовления) по цифровому маршруту проектирования с применением формальных и симуляционных методов функциональной верификации, с предоставлением пользователю портированных операционных систем, средств разработки (toolchain), программных платформ (frameworks).

Чем предстоит заниматься:

- Анализ архитектурных спецификаций и требований к ASIC.

- Разработка RTL-кода на языках Verilog/SystemVerilog.

- Проведение статических проверок (Lint, CDC/RDC анализ).

- Совместная скоординированная работа с командой функциональной верификации.

- Поддержка процессов синтеза, расчёта таймингов (STA) и отладки.

- Оптимизация RTL-кода по площади, производительности и энергопотреблению.

Требования к кандидату:

- Опыт работы в разработке цифровых ASIC/FPGA от 3х лет.

- Уверенное владение языками Verilog и SystemVerilog.

- Глубокое понимание полного цикла проектирования ASIC (Front-End Design Flow).

- Опыт работы с EDA-инструментами (любой вендор).

- Знание методологий и инструментов для Lint, CDC/RDC анализа.

- Навыки работы со скриптовыми языками (Tcl, Python).

Будет плюсом:

- Знание основ DFT.

- Опыт применения формальной верификации в разработке RTL.

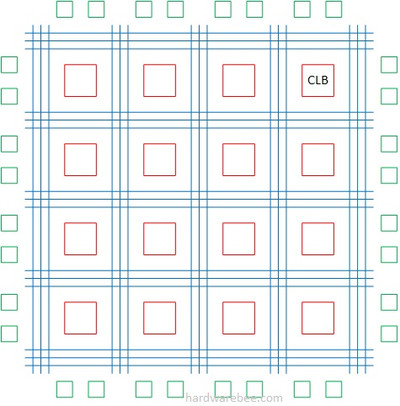

- Опыт разработки устройств на ПЛИС.

- Опыт прототипирования IP-блоков на основе ПЛИС.

Что мы предлагаем:

- Работу со сложными и интересными проектами.

- Дружелюбную и поддерживающую рабочую атмосферу.

- Бронирование сотрудников.

- Конкурентную ЗП дважды в месяц.

Возможность удаленной работы обсуждается индивидуально с каждым кандидатом

Контактная информация:

- Пентин Александр Сергеевич

- +7 (982) 615-06-62

- pentin-as@mail.ru

- @pentin_as

| Всего комментариев : 0 | |

0