FSC - FPGA-Systems Challenge

О чем это всё?

Это небольшой сборник с задачками по работе в Vivado, и больше ориентирован на повышение навыков оптимизации и анализа проектов.

Забудьте про ненавистные VHDL/Verilog/SV!!! В этом челендже они максимально бесполезны.

Но при этом, нужно хорошо знать архитектурные особенности ПЛИС AMD/Xilinx, команды Vivado и просто тонны прочитанной документации.

Добро пожаловать в самое пекло проектирования на ПЛИС!!!

Не зассал? Тогда попробуй сделать первое задание! Удачи!

Таблица рейтинга

Подготовка

- Склонируйте репозиторий fpga-systems-challenge

- Откройте Vivado (GUI или Tcl Shell)

- Сделайте source файла setup.tcl :

source {путь к fpga-systems-challenge/setup.tcl} - Дождитесь окончания работы скрипта

- Можно приступать к заданиям. Необходимые файлы dcp будут в папке fpga-systems-challenge/dcps

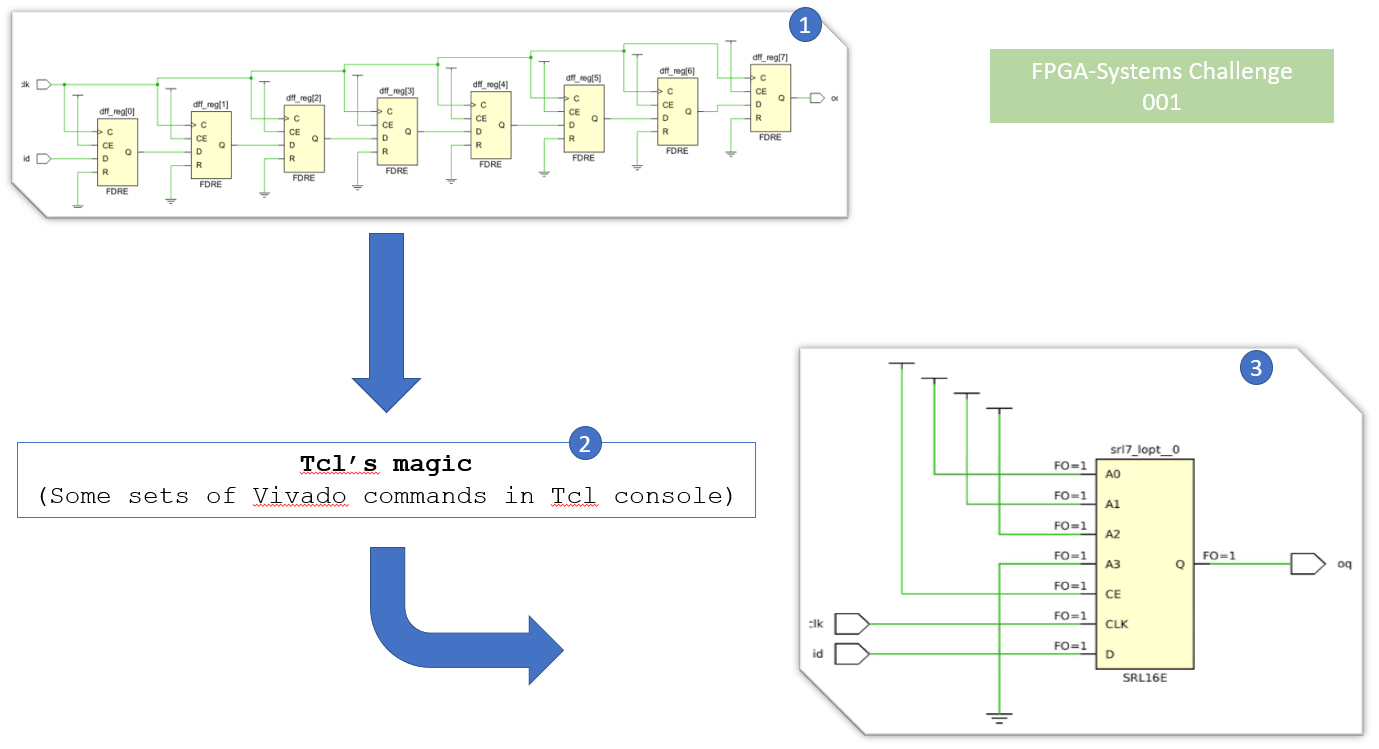

Задание 001

--> Открыть <--

- Откройте design checkpoint fsc_001.dcp

- Используя только Tcl команды Vivado необходимо преобразовать цепочку из 8-ми триггеров в один аппаратный сдвиговый регистр.

ЗАПРЕЩЕНО: создавать компоненты самостоятельно через ECO, это задание на post_synth optimisation

Получившиеся варианты команд оставляем в комментариях.

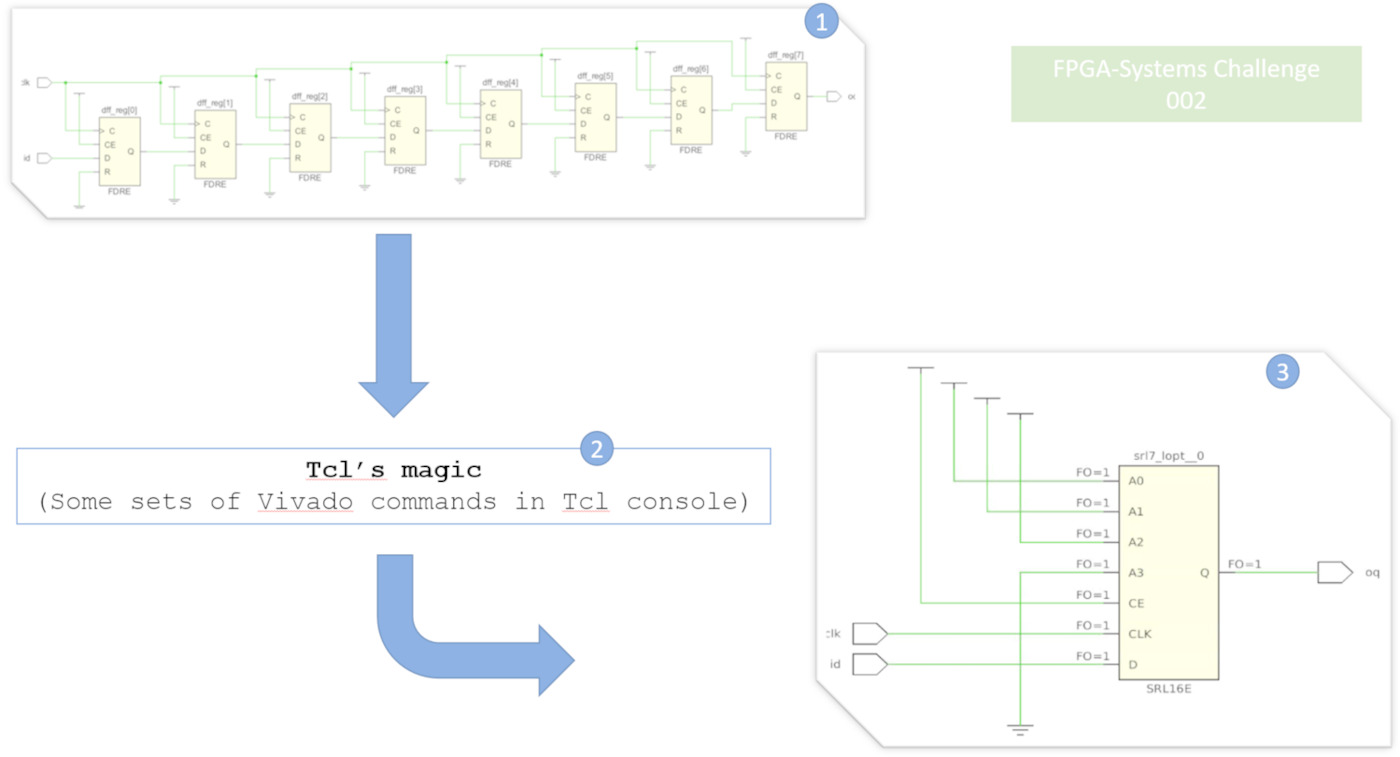

Задание 002

--> Открыть <--

- Откройте design checkpoint fsc_002.dcp

- Задание такое же как и для 001. Но команды, которые вы вводили в первом задании не будут работать, без дополнительного исследования схемы и ее объектов.

- Результат должен получиться такой же, 8 регистров, преобразованных в один аппаратный srl.

ЗАПРЕЩЕНО: создавать компоненты самостоятельно через ECO, это задание на post_synth optimisation

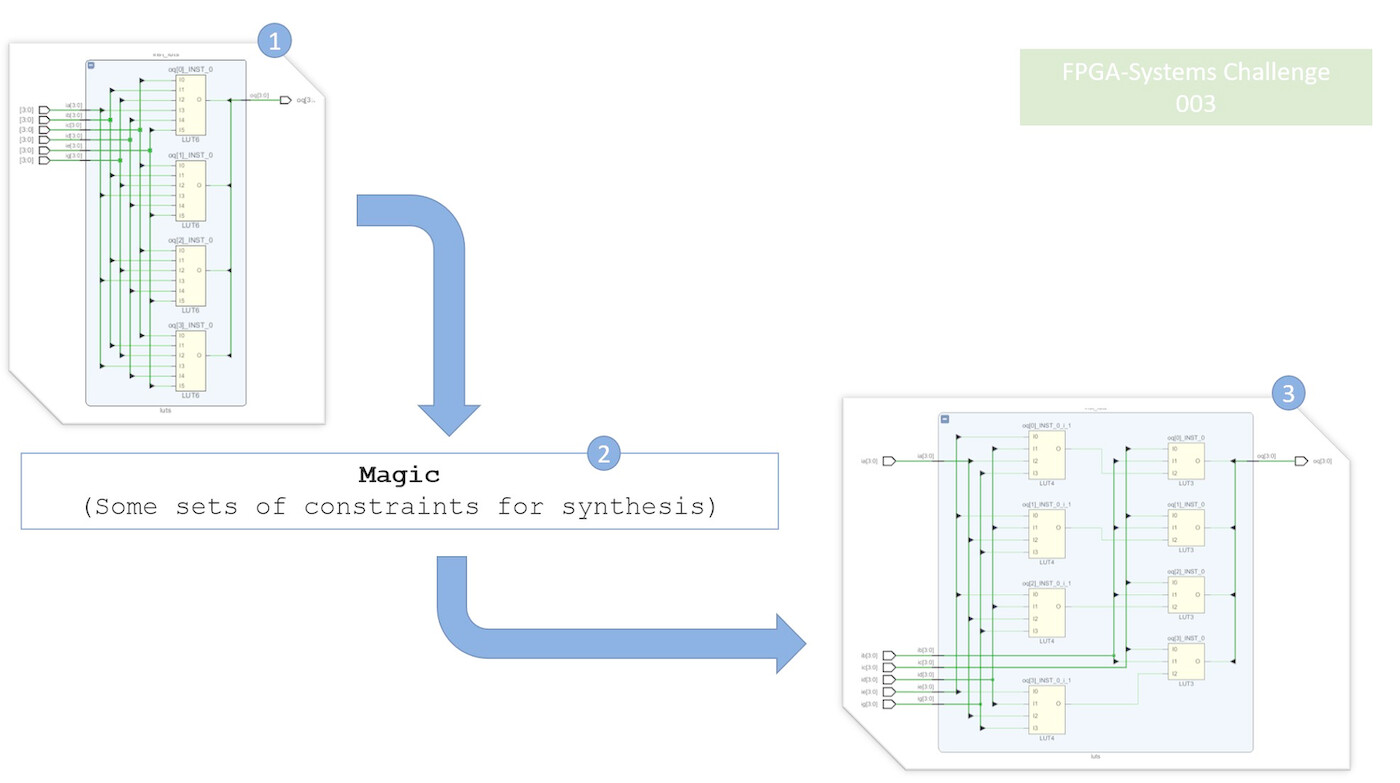

Задание 003

--> Открыть <--

- Откройте проект projects/fsc_003

- Ваша задача используя только проектные ограничения (xdc) синтезировать проект c размером лутов не больше чем LUT4

- Соответствующее проектное ограничение прописать в contr_synth.xdc

ЗАПРЕЩЕНО:

- Изменять исходники на верилог

- Изменять настройки синтеза через графический интерфейс

- Удалять и создавать элементы через ECO

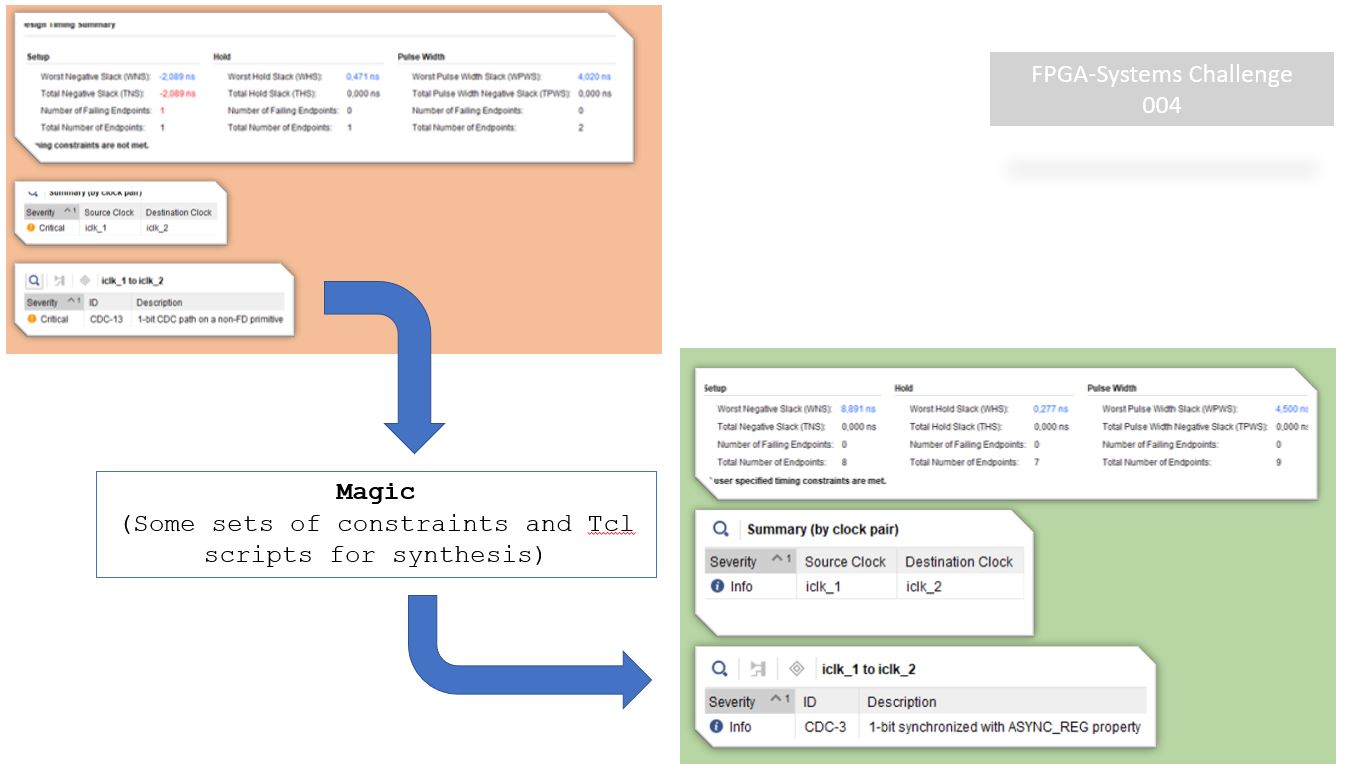

Задание 004

--> Открыть <--

- Откройте проект projects/fsc_004.xpr

- Ваши задачи:

- свести тайминг для схемы, содержащей два тактовых домена (CDC - Clock Domain Crossing) - setup slack на post-synthesis должен быть неотрицательным

- Достичь отсутствия каких-либо ошибок в Report CDC - не должно быть Warnings, Critical Warnings, Errors. Разрешается только уровень сообщений Info

- Добиться повторяемости проекта! Это означает, что вы должны организовать проект так, что бы вышеперечисленные условия выполнялись при повторном запуске синтеза без дополнительных манипуляций после открытия его результатов. Разрешено только формирование отчетов "Report что-то там"

РАЗРЕШЕНО:

- Использовать дополнительные файлы скриптов и проектных ограничений и выполнять с ними любые действия, в том числе назначать им определенные свойства.

- Изменять настройки синтеза касающиеся только подключения дополнительных файлов.

- Добавлять дополнительные файлы проектных ограничений в проект

ЗАПРЕЩЕНО:

- Изменять исходный код Verilog

- Изменять любые настройки синтеза, не относящиеся к подключению файлов

- Изменять заданные значения периода тактовых сигналов

- Применять констрейн set_clock_groups с любыми опциями! <-- Категорически запрещено!!!

- Применять констрейн set_false_path! <-- Категорически запрещено!!!

- Для п.3 - повторяемость результатов синтеза - после Open Synthesized Design запрещены любые дополнительные манипуляции с нетлистом, объектами и свойствами, кроме создания отчетов