Статьи участников нашего сообщества

Модуль: Каталог статей

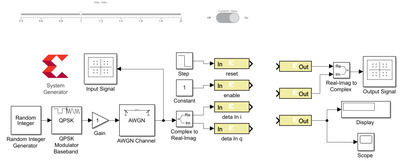

Xilinx AXI Stream DMA

Проблема: при поступлени stream данных от устройства они не передаются через DMA.

2087

ZYNQ SW: EBAZ4205: часть 4 (Vivado 2023)

Продолжение руководства по запуску платы EBAZ4205 на Vivado 2023.2

Начало в 3-й части

8738

7

ZYNQ HW: EBAZ4205: часть 3 (Vivado 2023)

Повторение туториала из Части №1, но и использованием версии Vivado 2023.2.

Повторение создание проекта Hello World с выводом текстовой строки в последовательный интерфейс UART, но на плате EBAZ4205. Для этого нужно будет учесть аппаратные особенности этой платы. Так же, отличием этого туториала является использование Vitis вместо более раннего варианта SDK.

8598

5

Найдено 9-ое число Дедекинда и, как вы наверное догадываетесь, не без помощи FPGA

42 цифры создающие историю. Ученые из Университета Paderborn и KU Leuven раскрыли тайну математики десятилетней давности, относящуюся к так называемым числам Дедекинда.

Эксперты по всему миру занимаются поиском 9-го числа Дедекинда с 1991 года. Ученые из университета Paderborn получили точную последовательность чисел с помощью расположенного там суперкомпьютера Noctua. Результаты будут представлены в сентябре на Международном семинаре по булевым функциям и их приложениям (BFA) в Норвегии.

2341

0

Формальная верификация с SymbiYosys

В статье кратко рассказано, что такое формальная верификация и для чего она нужна, а так же приведен простой пример верификации маленько

4342

0

Сага о светодиодах. Часть 4.

В интернете можно найти множество описаний устройств реализующих протокол i2c. В основном в этих описаниях рассматривается реализация и работа самого протокола i2c и довольно мало уделяется внимания разработке интерфейсов для управления такими устройствами. В этой работе я буду уделять основное внимание интерфейсам управления для устройств, реализующих протокол i2c.

1688

0

0