Статьи из категории: Верификация

Категория:Верификация

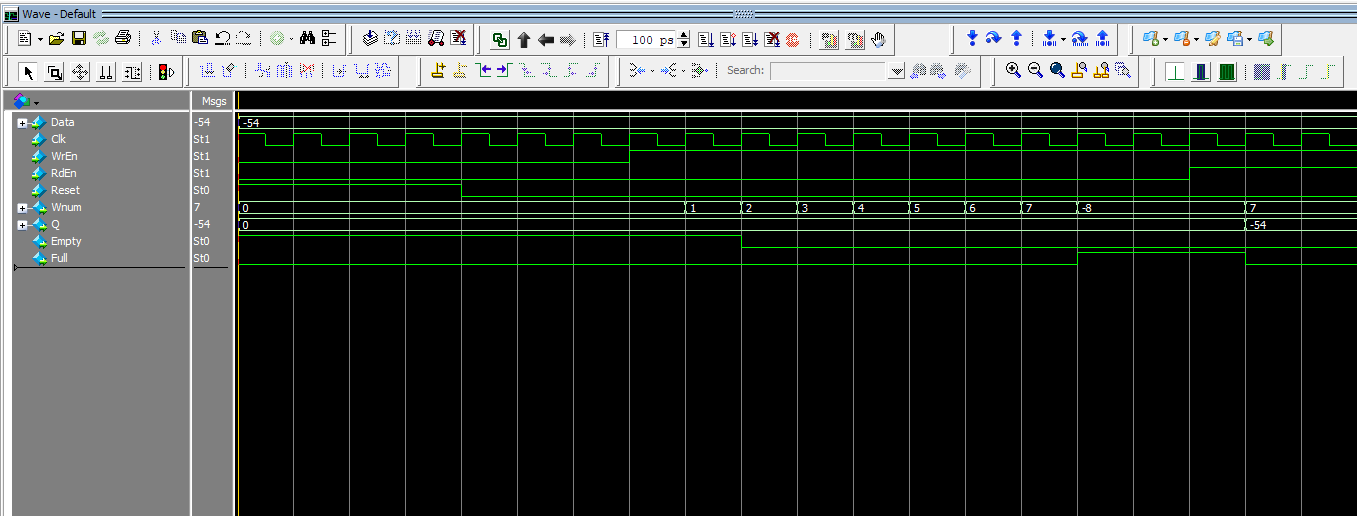

Формальная верификация с SymbiYosys

В статье кратко рассказано, что такое формальная верификация и для чего она нужна, а так же приведен простой пример верификации маленько

5101

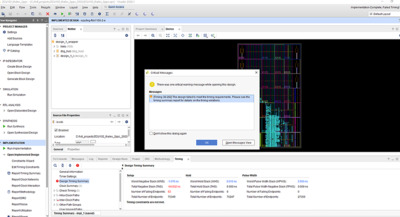

Запуск симуляции IP-ядер фирмы GoWiN

При разработке под GOWIN нередко возникает необходимость произвести моделирование блока, в состав которого входит набор IP ядер. Поскольку собственного инструмента моделирования на момент версии 1.9.8.10 нет, а решение DS Cloud может быть недоступно, необходимо самостоятельно решить этот вопрос.

10906

0

Отслеживаем успехи верификации в Obsidian

В статье показан пример построения системы контроля за ходом верификации с использованием бесплатного приложения Obsidian.

3185

1

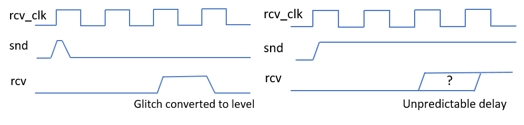

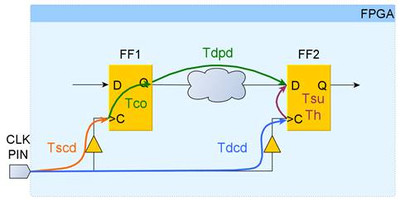

Верификация проблем с пересечением тактовых сигналов в ПЛИС с помощью ALINT-PRO

Предположим, у вас есть одна или несколько ПЛИС, на которые подаются разные тактовые сигналы для отправляемых и принимаемых данных (назовем их «клоки», пусть будет snd_clk для отправки данных и rcv_clk для приема этих данных). Что будет, если эти сигналы не синхронизованы, то есть «плавают» друг относительно друга?

6919

6

Статическое в SystemVerilog

В данной статье мы рассмотрим отличия статических и автоматических переменных и функций. Мы увидим, что понятие “статический” имеет различные значения для модулей и классов, разберёмся, почему это так, и научимся выбирать нужный нам вариант.

Говорить будем преимущественно о симуляции, а также рассмотрим один пример синтеза.

11946

8

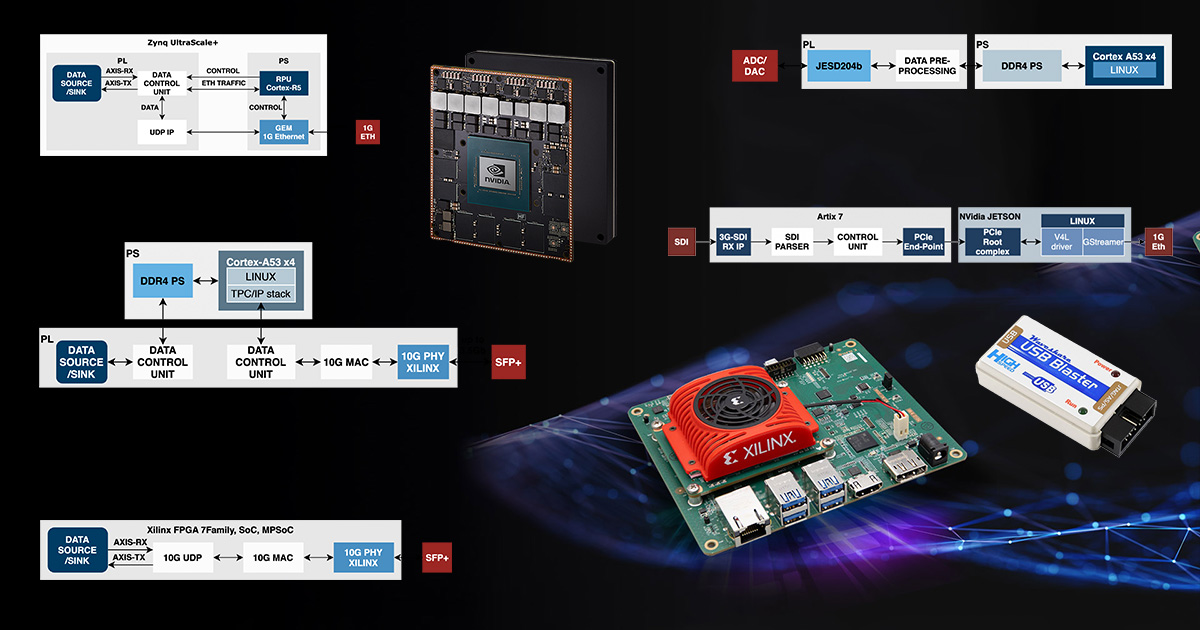

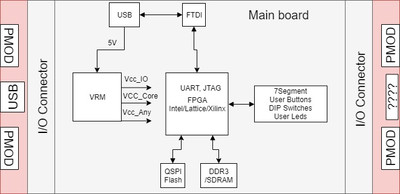

Искусство отладки FPGA: как сократить срок тестирования за счет грамотной разработки

Статья о полезных инструментах и типичных ошибках при отладке прошивки для FPGA. Основана на реальных событиях, а точнее — на опыте разработок для FPGA Xilinx, Lattice и Microchip. Внутри вас ждет принцип 20/80 для планирования времени, правило жизни У. Черчилля и полезные практические советы.

4591

0

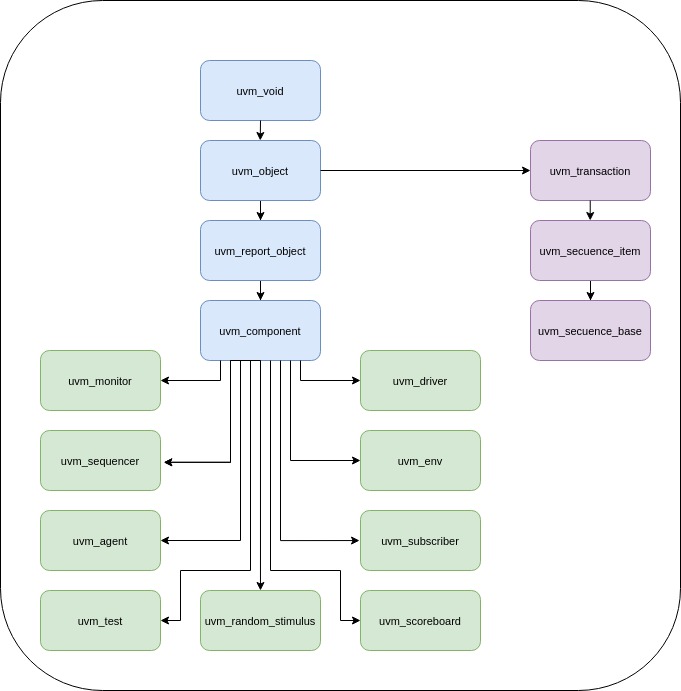

UVM общие сведения и организация методологии

В статье рассмотрены теоретические аспекты UVM методологии. По большей части, статья состоит из перевода англоязычных статей и книг. В статье описываются преимущества использования UVM при верификации аппаратных модулей и основные понятия, без которых не обойтись при разработке тестов по UVM методологии.

21163

2

0