Разработка IP-блока с помощью инструментов высокоуровнего синтеза: HLS Часть 2

Интегрирование IP-блоков в проект Vivado

Шаг 1: Создание нового проекта

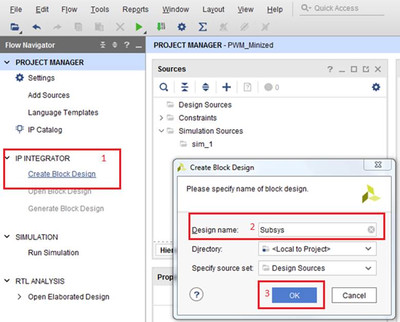

Шаг 2: Создаем блок дизайн

Шаг 3: Синтез и имплементация проекта

Список литературы

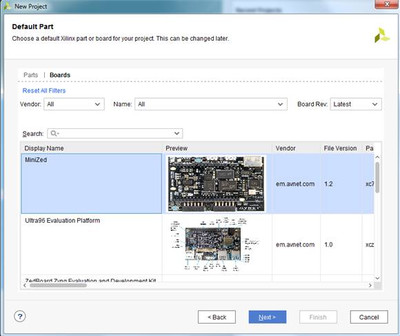

В этой части будут описаны основные шаги для создания блок дизайна (работа в IP Integrator) для разработанных ранее IP-блоков в среде Vivado HLS [1]. Интеграция будет производится для системы-на-кристалле ZYNQ-7000, а конкретно для Zynq установленного на плате MiniZed [2, 3]. Предполагается, что читатель уже умеет работать в Vivado, поэтому подробностей про создание проекта и т.п. не будет. Если Вы не знакомы с разработкой на Zynq-7000, то рекомендуем обратить внимание на соответствующую серию видеоуроков на русском [4]

О том, как добавить параметры MiniZed в Vivado написано в [5] (по ссылке архив с файлами и инструкцией).

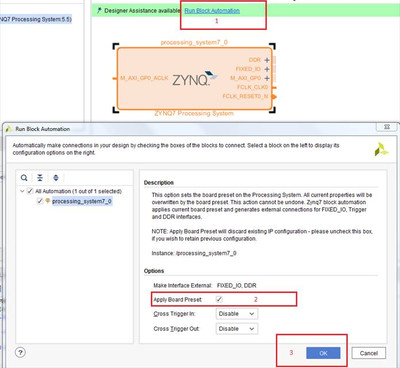

Нажимаем на плюс на рабочей панели в открывшемся окне и выбираем “ZYNQ7 Processing System”. После того как IP добавится в блок дизайн появится помощник. Нажимаем на “Run Block Automation”. Проверяем, чтобы стояла галочка напротив пункта с применением параметров предустановки (Рисунок 3) – это необходимо для того, чтобы все интерфейсы, которые есть на плате и используются цинком, были настроены корректно.

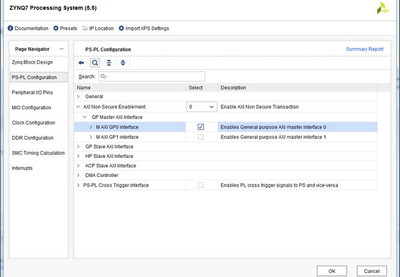

По факту нам нужен только UART, чтобы мы могли принимать и отправлять сообщения. Так же нам нужен AXI GP порт для связи с нашими IP-блоками. Для этого жмем два раза на IP ZYNQ в блок дизайне. В открывшемся окне переходим во вкладку PS-PL Configuration и находим M AXI GP0, отмечаем галочкой (Рисунок 4).

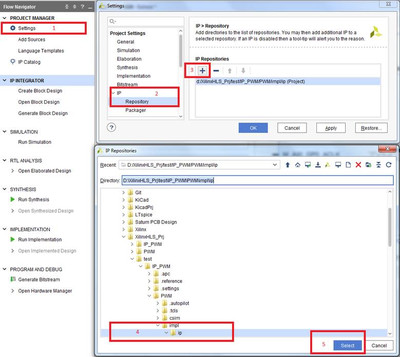

Теперь добавим наши IP-блоки. Для этого в менеджере проекта заходим в настройки, переходим во вкладку IP, выбираем вкладку Repository, нажимаем на плюс, указываем путь к IP блоку. IP-блоки можно найти в папке impl → ip каждого отдельного решения в Vivado HLS (Рисунок 5).

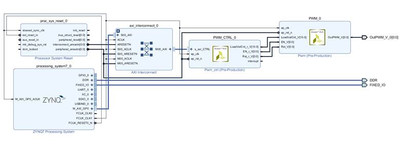

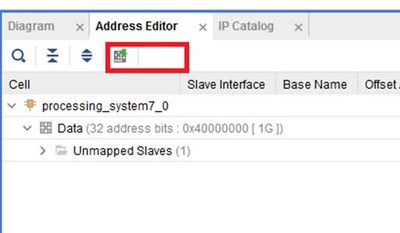

Добавляем наши IP-блоки на схему в блок дизайне. Еще нам понадобятся стандартные блоки, которые называются “Processor System Reset” и “AXI Interconnect” (нужен для подключения M AXI GP к AXI4-Lite). Интерконнект по умолчанию с двумя мастерами, нам же нужен только один, поэтому открываем его двойным кликом и выбираем нужное количество мастеров. Соединяем все блоки между собой как показано на рисунке (Рисунок 6). Выход OutPWM_V сделаем внешним для блок дизайна (просто щелкаем по сигналу и выбираем “Make External”). Во вкладке “Window” жмем “Address Editor” в открывшейся вкладке нажимаем на кнопку автоматического назначения адресов (Рисунок 7).

На этом разработка блок дизайна окончена.

Шаг 3: Синтез и имплементация проекта

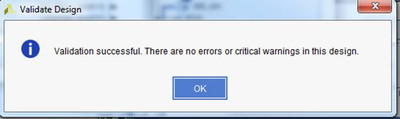

Возвращаемся в наш блок дизайн и нажимаем F6 (выполнится проверка собранного проекта в IP-Integrator). Если ничего не напутали, то Vivado напишет, что все хорошо (Рисунок 8).

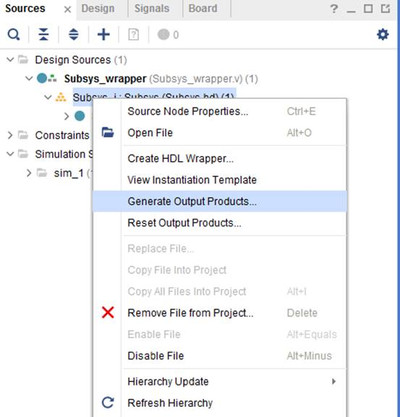

Далее нажимаем во вкладке “Source” проекта по блок дизайну правой кнопкой мыши и выбираем “Generate Output Products”. В открывшемся окне выбираем “Global”. После этого снова жмем по блок дизайну правой кнопкой мыши и жмем “Create HDL Wrapper” (Рисунок 9). В открывшемся окне оставляем все как есть.

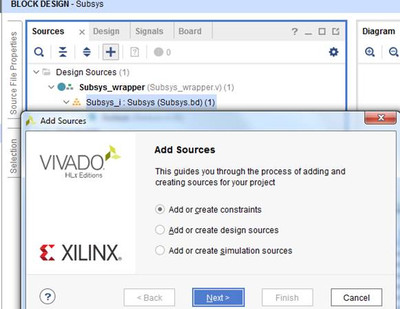

Дальше необходимо добавить файл, в котором будет указана информация о том, к какому выводу нашей микросхемы будет подключен сигнал OutPWM_V_0 и какой у него стандарт напряжения. Для этого нажимаем на плюс во вкладке “Source” и выбираем “Add or create constraints” (Рисунок 10). Называем файл как угодно. Пишем в нем следующее:

# Set the bank voltage for IO Bank 35 to 3.3V

set_property IOSTANDARD LVCMOS33 [get_ports -of_objects [get_iobanks 35]];

OutPWM_V_0 будет выведен на пин E13.

Теперь необходимо сгенерировать файл для прошивки нашей СнК. Чтобы сгенерировать битстрим можно пошагово запускать каждый этап в Vivado, а можно просто выбрать генерацию битстрима (кнопка “Generate Bitstream”), тогда Vivado скажет, что нет результатов синтеза и имплементации и предложит их получить. Т.к. все делается в бесплатной версии Vivado, то необходимо чтобы выбранная модель СнК была доступна в этой версии. Перечень поддерживаемых СнК для бесплатной версии Vivado следует уточнить в [6] или [7] (обязательно убедитесь, что версия документа соответствует версии Vivado). На этом этап интеграции IP блоков, разработанных на HLS в систему на базе ZYNQ окончена.

2. MiniZed™: a single-core Zynq 7Z007S development board

3. Осваиваем Zynq-7000S с бесплатной отладкой: видео

4. Осваиваем Zynq-7000: видеоуроки (доп. ссылка)

5. Добавление MiniZed в Vivado: архив с инструкцией

6. Vivado Design Suite Evaluation and WebPACK // Ссылка

7. UG973. Release Notes, Installation, and Licensing

Скачать статью в формате PDF. Зарегистрируйтесь, это не займет много времени. Статья в формате PDF