Что внутри ПЛИС или то, о чем не говорят в обучающих видео

Оглавление

*О найденных опечатках и замечаниях просим сообщить admin@fpga-systems.ru

Статья доступна в формате PDF

Введение

ПЛИС – программируемые логические интегральные схемы.

Часто в роликах на ютубе или в различных статьях о том «Что же такое ПЛИС?» приводят одну и ту же концепцию ее построения, то есть ПЛИС изображают как набор конфигурируемых логических блоков, соединенных между собой матрицей соединений или интерконнектами.

С одной стороны это верно, именно так и устроены самые простые представители программируемых логических микросхем, но сегодня ПЛИС – это нечто более сложное и в рамках этой статьи мы разберемся из чего же на самом деле состоят современные FPGA.

1. Типичное представление FPGA

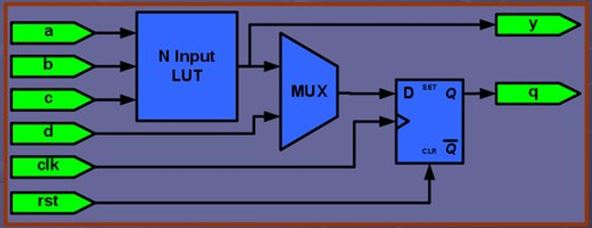

Что возникает в Вашей голове, когда вам говорят про ПЛИС? Наиболее вероятно, что на ум приходит примерно вот такая картинка (рисунок 1), где схематично изображено упрощенное представление конфигурируемого логического блока: его комбинационной части, состоящей из N-входного Look Up Table или таблиц истинности и мультиплексора и синхронной части, в качестве которой обычно выступает D-триггер.

Рисунок 1. Типичное представление структуры логических блоков ПЛИС

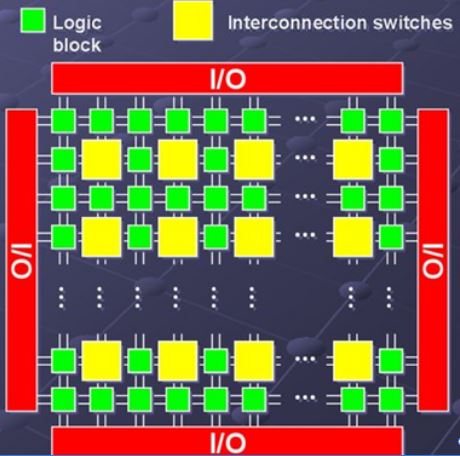

Не исключено, что возникает и вот такое укрупненное представление (рисунок 2), на котором конфигурируемые логические блоки соединяются между собой с помощью интерконнектов и по краям находятся порты ввода-вывода нашей микросхемы.

Рисунок 2. Типичное представление архитектуры ПЛИС

Небольшое лирическое отступление: конфигурируемый логический блок – это основной логический ресурс, предназначенный для реализации последовательных (синхронных), а также комбинаторных схем. Каждый конфигурируемый логический блок соединен с матрицей коммутаторов для доступа к общей матрице маршрутизации. Но об этом чуть позже.

Но на самом деле это лишь верхушка айсберга. Да, современные ПЛИС состоят из тысяч, сотен тысяч или даже миллионов конфигурируемых логических блоков, вот только выглядят они несколько сложнее, чем просто два квадратика одна трапеция.

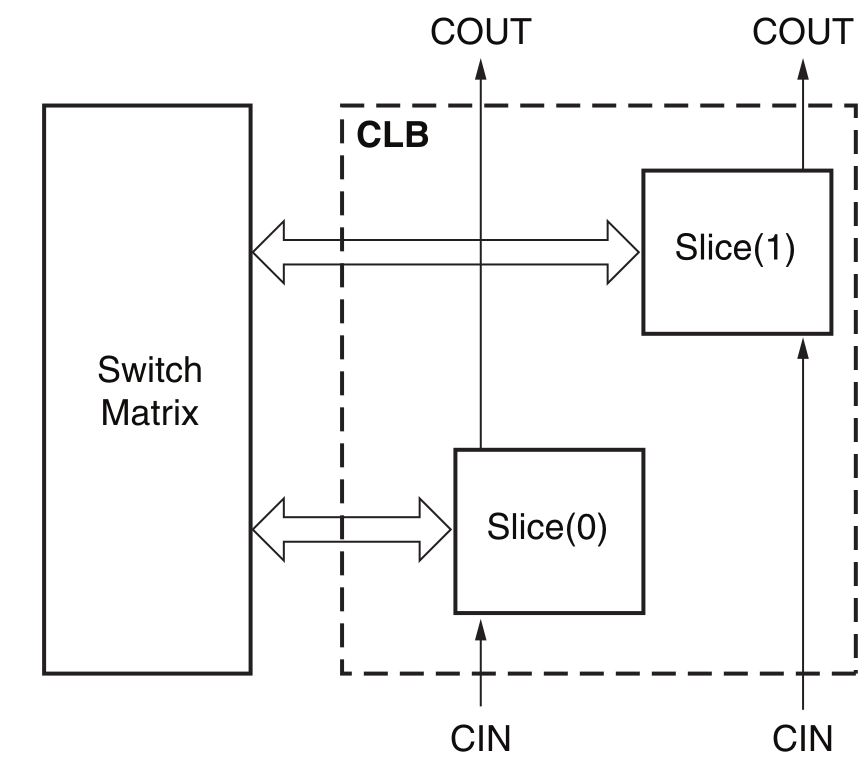

Для примера построения современного конфигурируемого логического блока давайте обратимся к документации [1]. Например, для 7-го семейства ПЛИС компании Xilinx он состоит из двух секций, или slice и цепей переноса (рисунок 3). Пока как-то не впечатляет, да?

Рисунок 3. Укрупнённое представление конфигурируемого логического блока ПЛИС 7-го семейства компании Xilinx

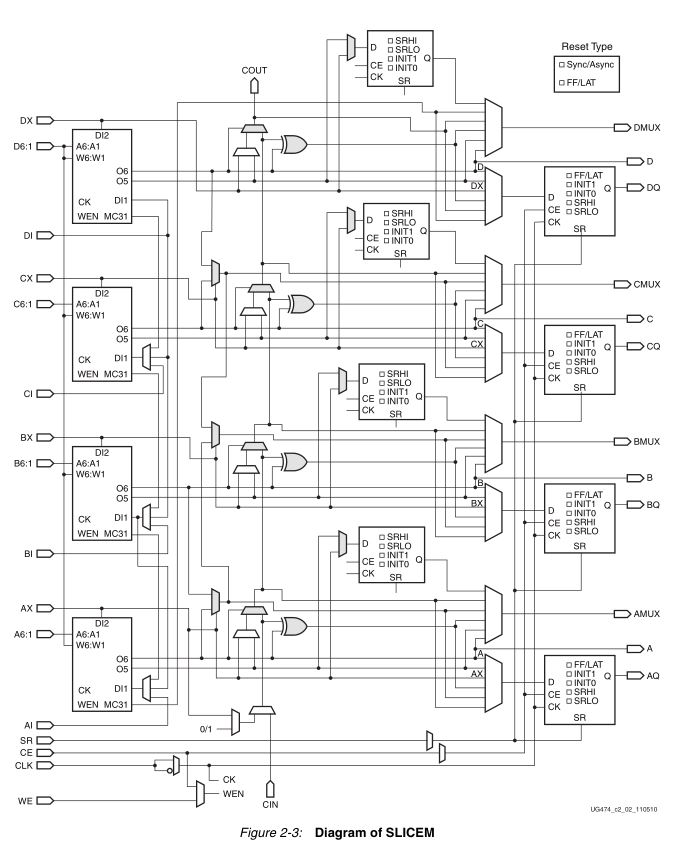

Не спешите с выводами. Каждая из секций может быть одного из двух типов: либо SliceL либо SliceM и вот именно их архитектура для нас уже более интересна.

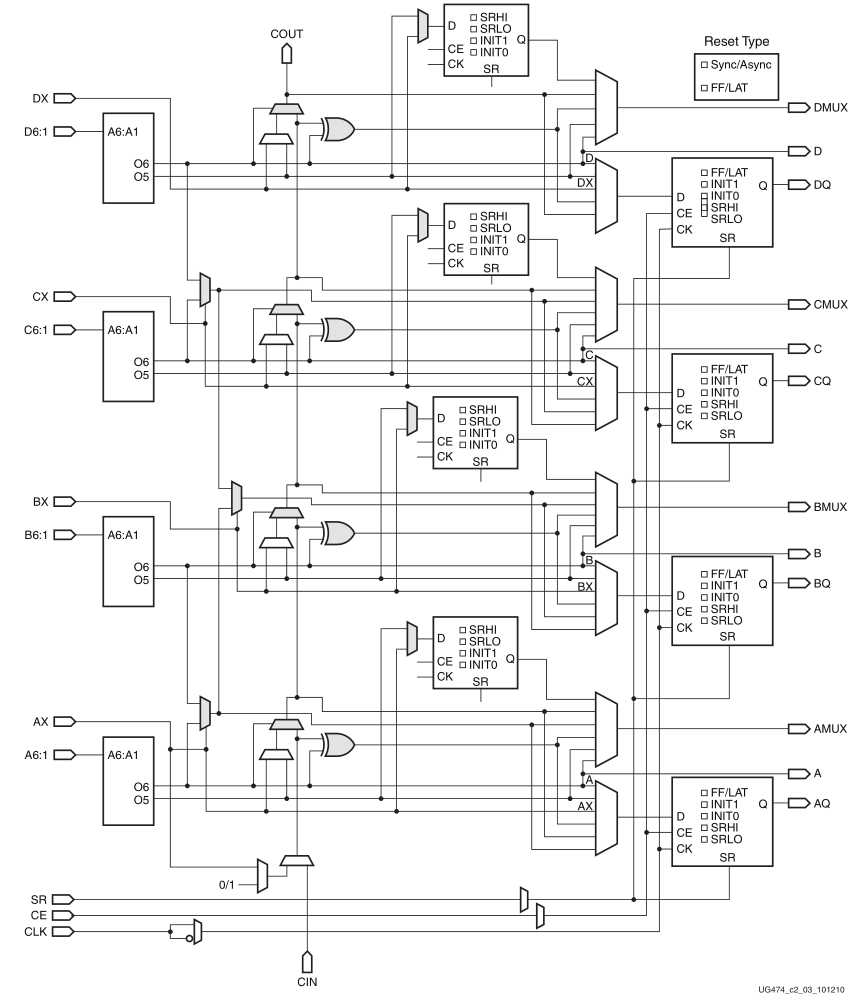

2.1. SliceL

Это наиболее «простая» из имеющихся в 7-ой серии ПЛИС Xilinx секций (рисунок 4). При этом она в своем составе содержит:

- • Таблицы истинности, которые могут быть как 5-ти, так и 6-ти входовыми и иметь 2 или 1 выход соответственно

- • Цепи переноса – используемые при реализации математических операций, имплементируемых в логике

- • Синхронные элементы – D-триггеры, которые можно сконфигурировать как обычные синхронные триггеры либо как защелки

- • Мультиплексоры, расширяющие функционал всего конфигурируемого логического блока

Рисунок 4. Структура SliceL

2.2. SliceM

Второй, более функциональный вид секций SliceM (рисунок 5). Он очень похож на SliceL, но при этом его таблицы истинности могут иметь несколько воплощений в проектах. Они могут выступать:

- • В качестве обычных таблиц истинности

- • В качестве элемента распределённой памяти, для хранения небольшого объема информации

- • В качестве аппаратных сдвиговых регистров, позволяя заменить одним элементов цепочку из 32 триггеров

Рисунок 5. Структура SliceM

Думаю, вам было бы интересно узнать, как нужно писать код на VHDL или Verilog, чтобы задействовать все эти ресурсы, казалось бы, обычного CLB - но об этом в другой раз.

Как мы только что увидели, даже такая простая структура из таблицы истинности, мультиплексора и триггера, на практике может оказаться мощным и многофункциональным блоком. И это мы лишь рассмотрели всего один ресурс ПЛИС. Движемся далее

2.3. Ячейки памяти

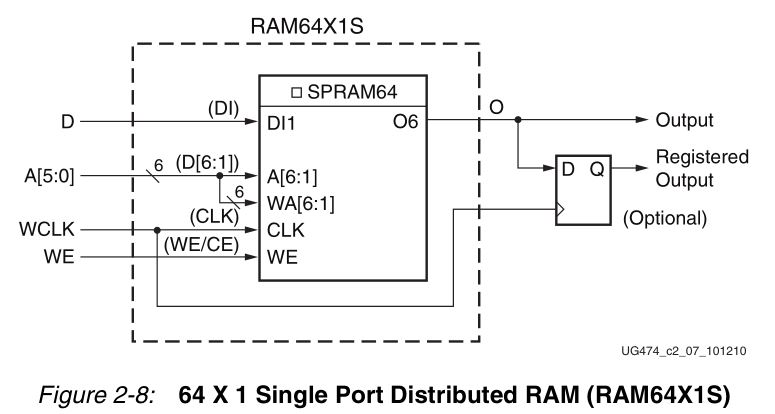

Мы уже упоминали, что часть секций могут быть использованы для хранения информации и могут выступать в качестве распределенной памяти. Почему распределенной? Такая память привязана к расположению конфигурируемых логических блоков и как бы равномерно распределена по всему кристаллу (рисунок 6).

Рисунок 6. Ячейка распределенной памяти

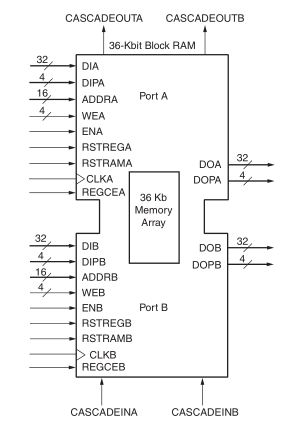

К сожалению, хранить большой объем информации в такой памяти не представляется возможным. Для решения этой проблемы в ПЛИС имеется специальный ресурс – блочная память – которая представляет собой аппаратный блок [2], в котором можно хранить значительно больше информации, нежели в распределенной памяти.

Рисунок 7. Ячейка блочной памяти

Объем блочной памяти, ее функциональность и количество доступных компонентов зависит как от производителя ПЛИС, так и от семейства ПЛИС. Блочная память может быть размером 9кб, 18кб, 36кб или даже 288кб.

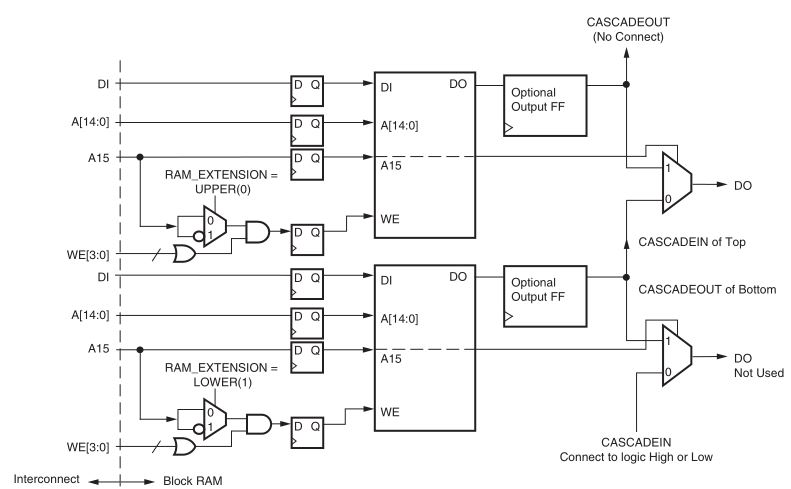

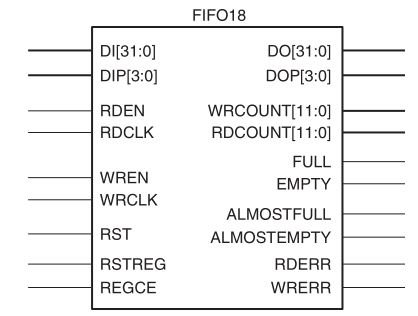

Она может быть сконфигурирована различными способами, может быть каскадирована (рисунок 8, а), иметь различную разрядность для записи и чтения, иметь разные управляющие сигналы. Память может иметь один или два порта для выполнения независимых операций записи/чтения по обоим портам, т. н. true-dual port ram, использоваться в качестве FIFO (рисунок 8, б) - специального элемента для синхронизации тактовых доменов и многое другое.

|

|

| а) | б) |

Рисунок 8. Использование блочной памяти: а – каскадирование, б - FIFO

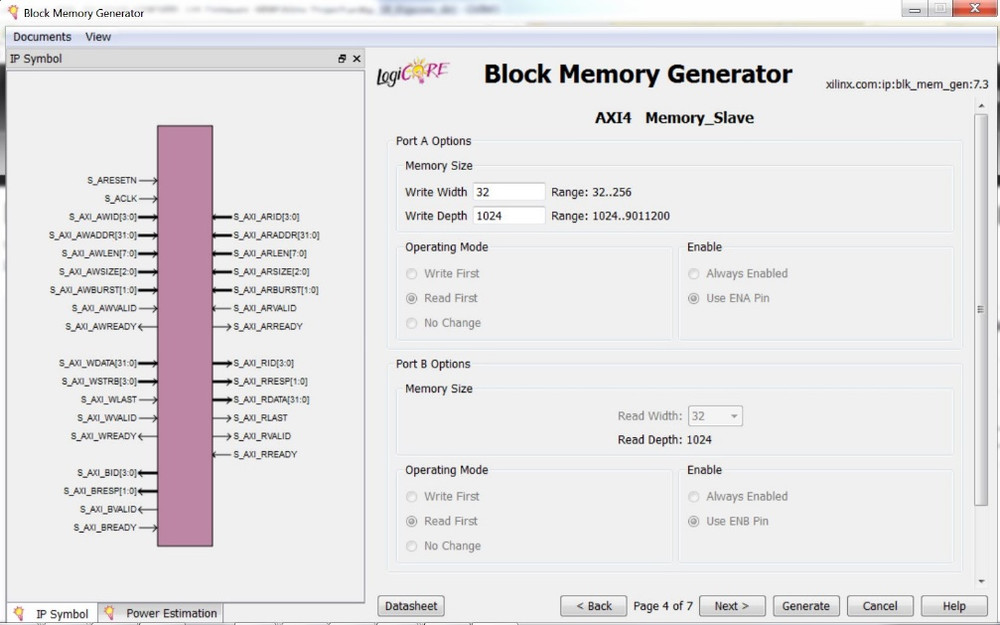

Часто для настройки и управления режимами работы используются специальный мастер настроек или wizard (рисунок 9)– где с помощью графического интерфейса пользователь задает все необходимые параметр памяти.

Рисунок 9. Пример мастера настройки (wizard) блочной памяти

Движемся далее.

2.4. Математические и логические векторные операции

Вы наверняка слышали, что ПЛИС часто применяются в решении задач цифровой обработки сигналов.

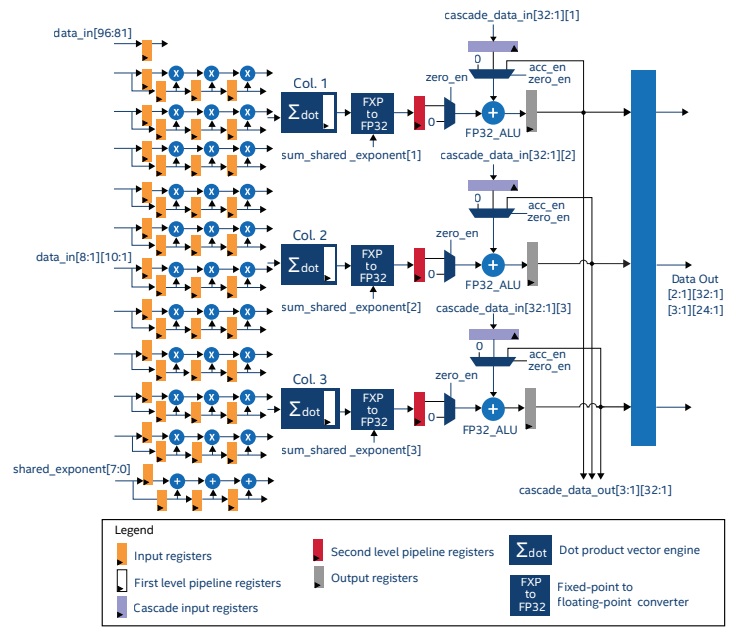

Это стало возможным благодаря DSP ячейкам или DSP секциям – специализированным умножителям внутри ПЛИС [3]. Современные ПЛИС могут насчитывать несколько тысяч таких секций, которые могут выполнять операции как с фиксированной точкой, с плавающей точкой, операции с комплексными числами, логические операции с векторами данных и много многое другое: опять же, это зависит от производителя и семейства плис. Давайте посмотрим, как они устроены DSP секции на примере DSP48E1

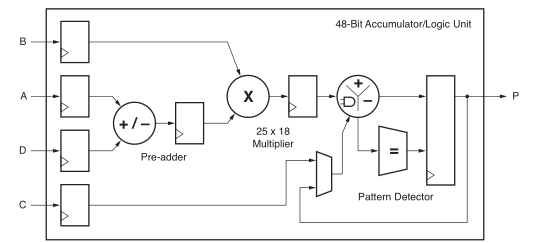

Перед вами базовая функциональная диаграмма DSP секции (рисунок 10). Она включает в себя триггеры по входу, промежуточные триггеры, триггеры по выходу, блоки арифметических и логических операций.

Рисунок 10. Базовая функциональная диаграмма DSP секции

Наверняка у вас сразу появился вопрос, а зачем нам нужны такие блоки внутри ПЛИС, мы же можем использовать обычные логические ресурсы ПЛИС для реализации того же самого сложения двух векторов или выполнения операций сравнения. Да, вы можете это сделать, но, так же, как и в случае с распределенной памятью вы потратите большое количество ресурсов для выполнения этих операций, особенно если работаете с широкими данными. Например, умножаете два 16-битных числа. Не говоря уже о максимальной частоте работы такой схемы.

Чтобы не тратить логические ресурсы ПЛИС и иметь хорошую производительность разрабатываемой системы и были интегрированы DSP секции.

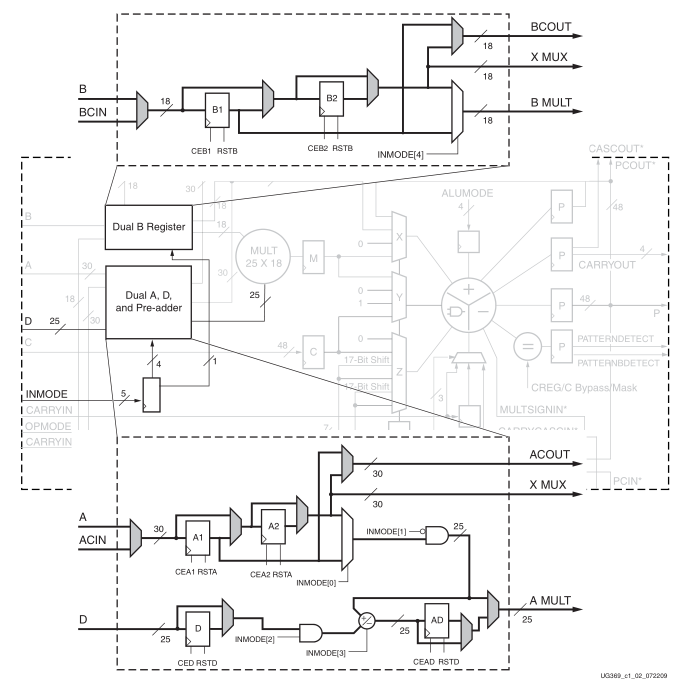

Если же мы проявим чуть большей интерес к секциям DSP, то мы увидим, что они также имеют сложную внутреннюю структуру, для настройки которой также зачастую используют специальные визарды.

Рисунок 11. Более детальное представление DSP секции

Комбинирование ячеек блочной памяти и DSP секций является большим преимуществом ПЛИС и такая конфигурация очень часто находит свое применение в решении задачи цифровой обработки сигналов, где сразу несколько тысяч брамок и dsp работают одновременно, например, выполняя фильтрацию сигнала, различные частотно-временные преобразования и анализ спектра.

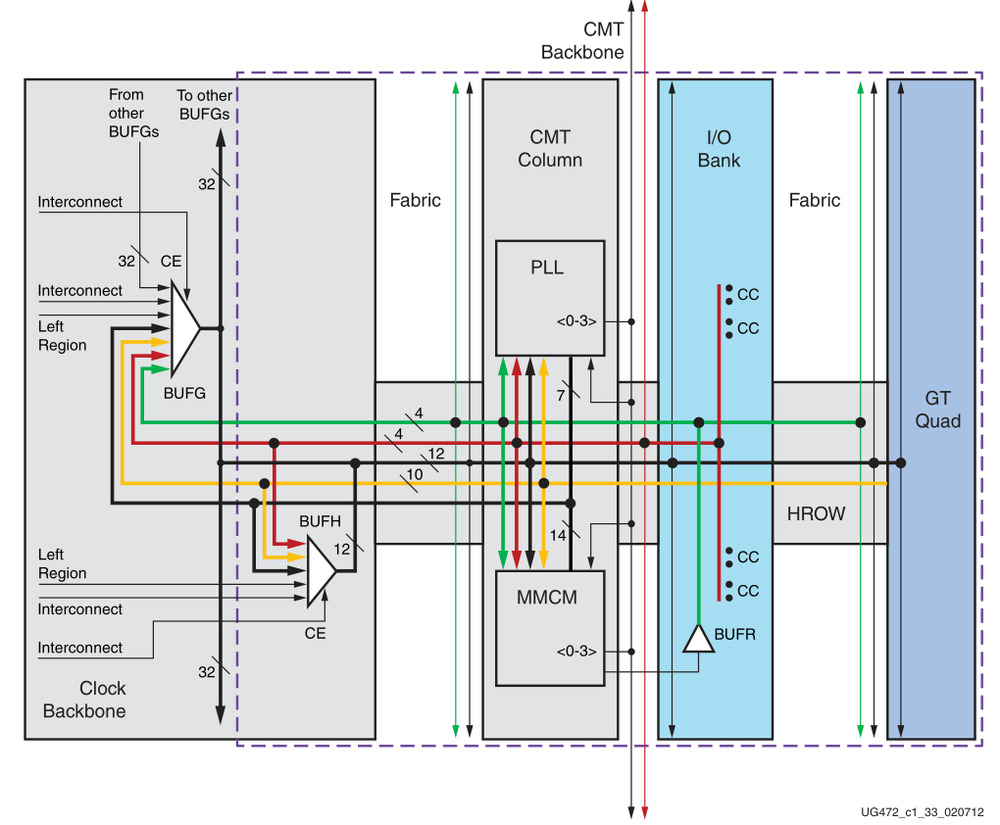

2.5. Сеть тактовой синхронизации

Зададимся вопросом: как нам синхронизировать ресурсы внутри ПЛИС? Для этого есть отдельный выделенный набор ресурсов (рисунок 12), которые включают в себя: ресурсы генерации сетки тактовых частот, построенные на базе фазовой или цифровой автоподстройки частоты – PLL / DLL, специализированных тактовых буферов и трассировочных ресурсов [4].

Рисунок 12. Пример ресурсов тактовой синхронизации в FPGA

Сведение таймингов внутри плис – это основная задача FPGA разработчика, помимо написания кода и его отладки. Понимание устройства тактовой сети и ресурсов, ее обеспечивающих очень важно, поскольку именно от этого зависит успех всего проекта.

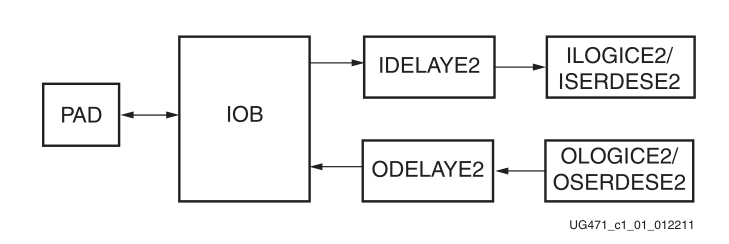

2.6. Порты ввода вывода

Связать ядро ПЛИС с внешним миром мы можем с помощью портов ввода вывода, которые так же не просты, как и сама ПЛИС [5].

Порты ввода вывода современных плис поддерживают просто огромное количество стандартов напряжения.

Но помимо простых выходных буферов, дифференциальных буферов и буферов с третьим состоянием, в портах ввода – вывода плис есть еще очень много разнообразных ресурсов, таких как:

- • Серилайзеры и десерилайзеры, преобразующие вектор данных в поток данных и наоборот

- • Блоки цифрового контроля импеданса DCI для достижения хорошей целостности сигнала

- • SDR и DDR триггеры для работы с различными типами памяти и интерфейсами

- • Различные типы задержек для компенсации неодинаковости линий на печатной плате

- • Свои собственные PLL для более точной подстройки блоков данных, относительно стробирующих или тактовых сигналов, например при работе с высокосортной памятью или АЦП/ЦАП

- • Собственные FIFO для компенсаций разности фаз между внешними сигналами и внутренней логикой ПЛИС

Рисунок 13. Укрупнённое представление структуры портов ввода/вывода

2.7. Что еще?

Помимо основных типов ресурсов: конфигурируемых логических блоков, блочной памяти, DSP секций, тактовой сети, портовой логики которые есть практически в любой ПЛИС в нее также могут быть интегрированы и специальные аппаратные блоки, например высокоскоростные трансиверы, PCIe блоки, контроллеры внешней памяти, аналогово-цифровые преобразователи и даже процессоры. Рекомендуем посмотреть заметку [6].

ПЛИС – это изначально универсальное устройство, на котором можно сделать абсолютно любые задачи: вы даже можете реализовать свой процессор на плис или развернуть готовый, запустить на нем линукс или другую ОС, обрабатывать 100/400/600Гбитные потоки данных, коммутировать десятки 10Гбитных каналов, выполнять обработку сигналов, видео, разворачивать нейронные сети, ускорять обработку баз данных, и многое многое другое, все что только можно себе вообразить.

Заключение

Мы рассмотрели лишь малую часть того, что есть в современных ПЛИС. Но даже после такого короткого обзора думаю вам стало интересно, что же еще есть внутри FPGA и как это применить в ваших проектах. Многое осталось за кадром, но если вам понравился такой формат, и вы хотите более детальные обзоры аппаратных ресурсов и может даже демонстрации примеров работы с ними, то оставляйте ваши пожелания в комментариях.

Список литературы

- https://www.xilinx.com/support/documentation/user_guides/ug474_7Series_CLB.pdf

- https://www.xilinx.com/support/documentation/user_guides/ug473_7Series_Memory_Resources.pdf

- https://www.xilinx.com/support/documentation/user_guides/ug479_7Series_DSP48E1.pdf

- https://www.xilinx.com/support/documentation/user_guides/ug472_7Series_Clocking.pdf

- https://www.xilinx.com/support/documentation/user_guides/ug471_7Series_SelectIO.pdf

- Тензорные секции в ПЛИС

Статья доступна в формате PDF