Архив новостей из мира FPGA

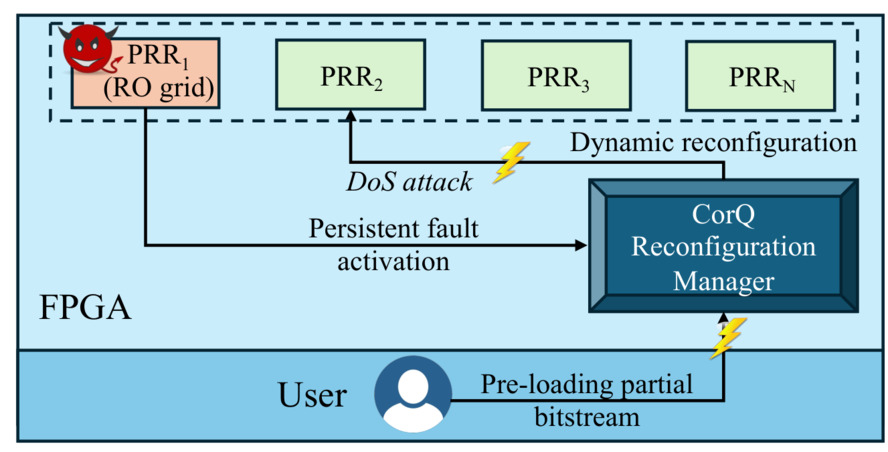

Вредоносные атаки с внедрением ошибок в FPGA

В статье обсуждается новая методика атак с использованием ошибок, направленных на программируемые логические интегральные схемы (ПЛИС), особенно в процессе частичной реконфигурации в облачных средах. По мере того как ПЛИС всё шире интегрируются в инфраструктуры облачных вычислений для задач вроде ускорения искусстве ... Читать дальше »

3436

Ссылки на материалы для начинающих и опытных

5717

0

Статья про UVVM от Клайва Максфилда

5728

0

интервью с Н.А.Шелепиным «О сегодняшнем развитии технологий и компонентов микро- и наноэлектроники»

О сегодняшнем развитии технологий и компонентов микро- и наноэлектроники мы поговорили с д.т.н., проф. Н.А. Шелепиным. Николай Алексеевич является модератором Секции №4 на российском форуме «Микроэлектроника 2021», и как никто другой знаком с научно-исследовательской работой по тематике микро- и наноэлектроники и положением дел в отрасли.

...

Читать дальше »

6160

0

PY-UVM

Ну что ж, медленно, но верно оно все-таки случилось. Python добрался и до UVM. Встречайте уже второй релиз PY-UVM 2.0 Информация по теме: ... Читать дальше »

6188

0

Интервью с генеральным директором АО «НИИМА «Прогресс»

В преддверии Форума «Микроэлектроника-2021» — главного события для отечественных разработчиков микроэлектронных компонентов, генеральный директор АО «НИИМА «Прогресс» Захар Константинович Кондрашов рассказал про ситуацию и последние тенденции в отрасли. ... Читать дальше »

6169

0

Идеи проектов для FPGA

Возможно, готовые списки проектов смогут помочь!

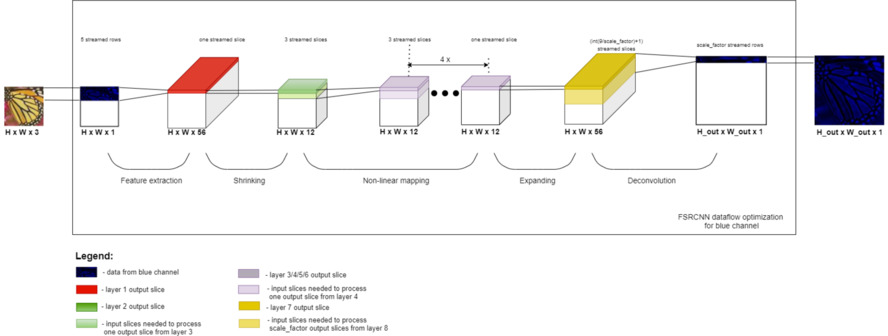

Ускорение масштабирования изображений с помощью CNN на FPGA

Процесс создания изображений с высоким разрешением из изображения с низким разрешением требует идентификации недостающих пикселей. Заполнение “пиксельных пустот” возможно устранить с помощью различных методов машинного обучения. Из всего многообразия методов сверточные нейронные сети выделяются свое ... Читать дальше »

5981

0

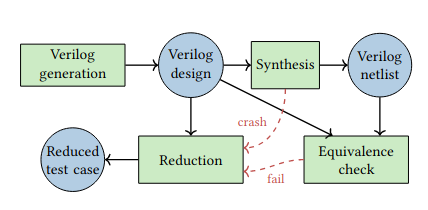

Verismith: поиск багов в синтезаторах для FPGA

Любопытная статья 2020 года о поиске багов в синтезаторах логики с помощью инструмента с открытым кодом. Инструмент, разработанный авторами (Yann Herklotz, John Wickerson), генерирует случайный модуль на Verilog. Результат синтеза случайного модуля сверяется с исходным RTL. Авторы использовали свою разработку, чтобы ... Читать дальше »

5779

0

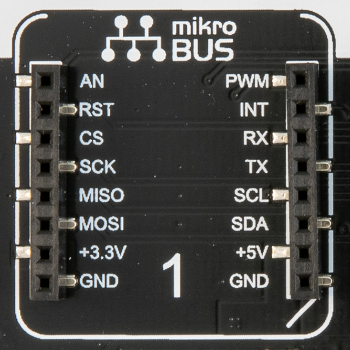

6 Способов расширения функциональности вашей отладочной платы с ПЛИС

Если вы когда-нибудь задумаете сделать свою отладочную плату бюджетного ценового диапазона, то вам наверняка будет полезно знать про общепринятые стандартные интерфейсы подключения внешней периферии: датчиков, камер, дисплеев и тд. В этой заметке вы ... Читать дальше »

5912

0 |

0