Ускорение масштабирования изображений с помощью CNN на FPGA

Процесс создания изображений с высоким разрешением из изображения с низким разрешением требует идентификации недостающих пикселей. Заполнение “пиксельных пустот” возможно устранить с помощью различных методов машинного обучения. Из всего многообразия методов сверточные нейронные сети выделяются своей возможностью многократного использования и небольшим количеством параметров. Используя преимущества иерархической структуры данных в изображениях, реализация CNN на уровне реконфигурируемого железа может обладать значительным преимуществами по сравнению с процессорами общего назначения.

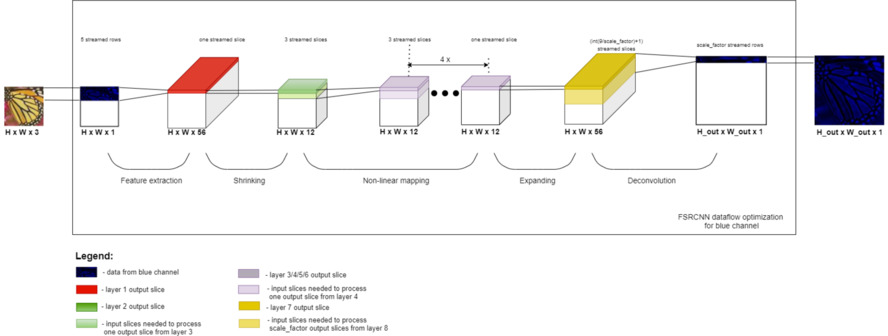

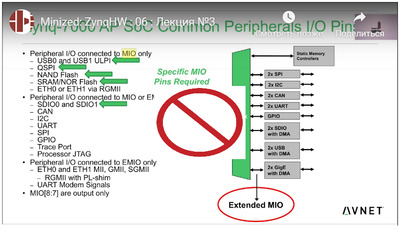

В этой статье описываются методы, используемые для ускорения масштабирования сверточной нейронной сети изображения на ПЛИС с использованием инструментов высокоуровнего синтеза (HLS). Ускорение было выполнено с использованием различных методов оптимизации, что незначительно повлияло на качество изображения при сверхразрешениях. Для сравнения результатов использовался алгоритм бикубической интерполяции в качестве эталонного алгоритма масштабирования. Приведены бенчмарки производительности реализованных ускорителей как на ПЛИС (Xilinx – Zynq-7000 SoC), так и на стандартном процессоре x64 (Intel Core i5-6200U).