Статьи из категории: Общее

Категория:Общее

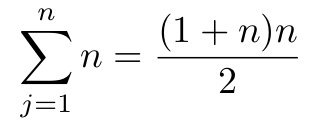

Основы статического временного анализа. Часть 6: Multicycle Path Constraint.

В статье продемонстрирована возможность изменения положения запускающих и защёлкивающих фронтов при передаче данных между тактовыми доменами. Показаны несколько практических примеров использования команды set_multicycle_path.

4526

0

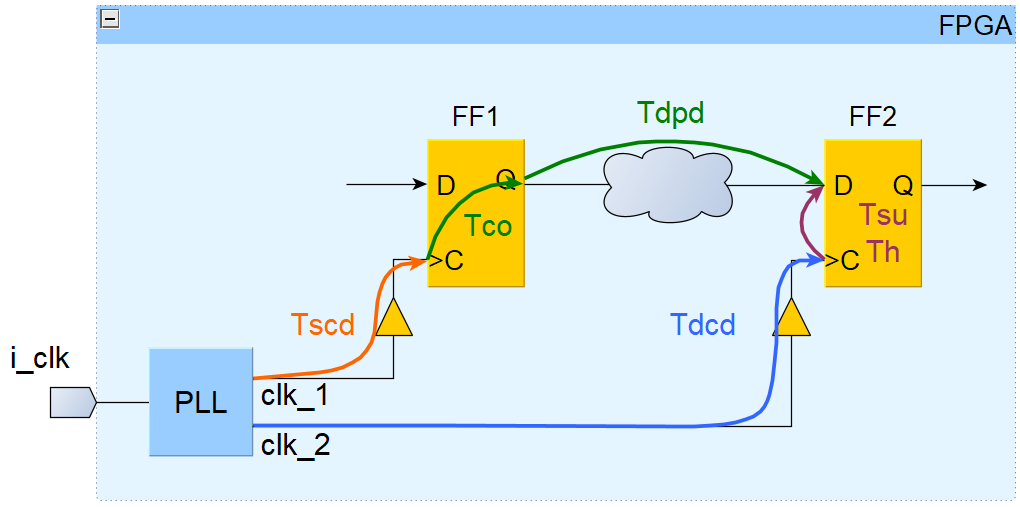

Демистификация сбросов: синхронные, асинхронные и другие соображения по проектированию... Часть 1

В статье рассматриваются некоторые аспекты важности правильного планирования и применения сброса

3251

0

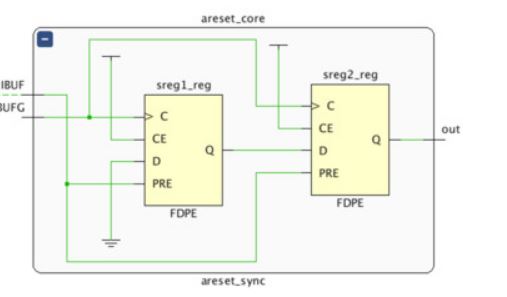

Основы статического временного анализа. Часть 5: False Path Constraint.

В статье представлен временной анализ передачи сигналов между двумя тактовыми доменами. Показано несколько способов исключения путей из временного анализа. Рассмотрены инструменты Vivado, предназначенные для проверки корректности передачи данных между тактовыми доменами.

5891

1

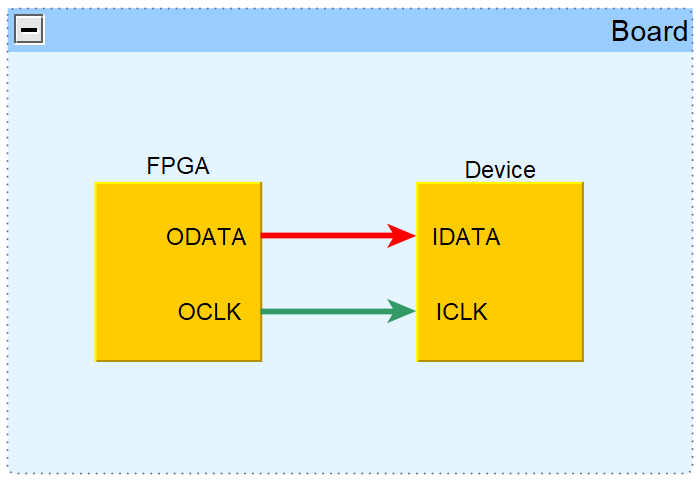

Основы статического временного анализа. Часть 4: Source Synchronous Output Delay Constraint.

В статье представлен временной анализ передачи сигналов из FPGA во внешнее устройство. Рассмотрены теоретические основы анализа для двух возможных случаев приема данных: по текущему и следующему фронту тактового сигнала. Разобраны практические примеры создания временных ограничений. Показан способ решения проблемы с временными ограничениями по Setup за счет инвертирования тактового сигнала и использования ODDR триггера.

5558

0

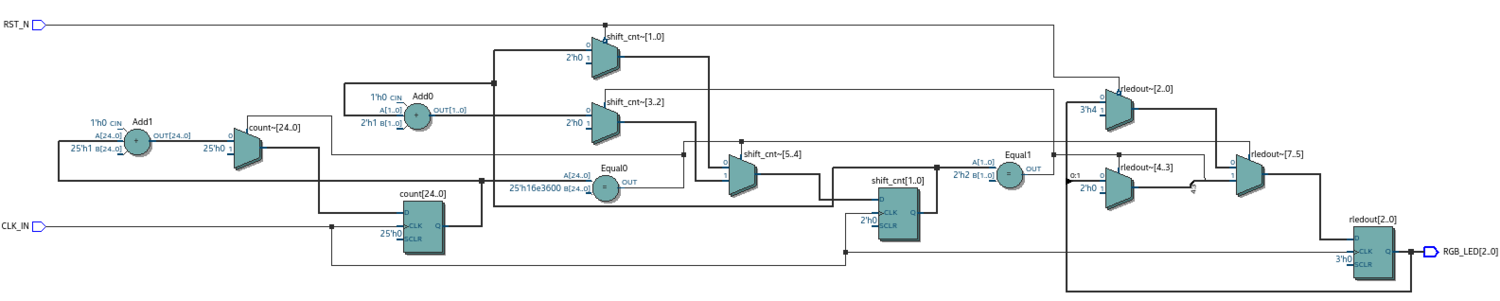

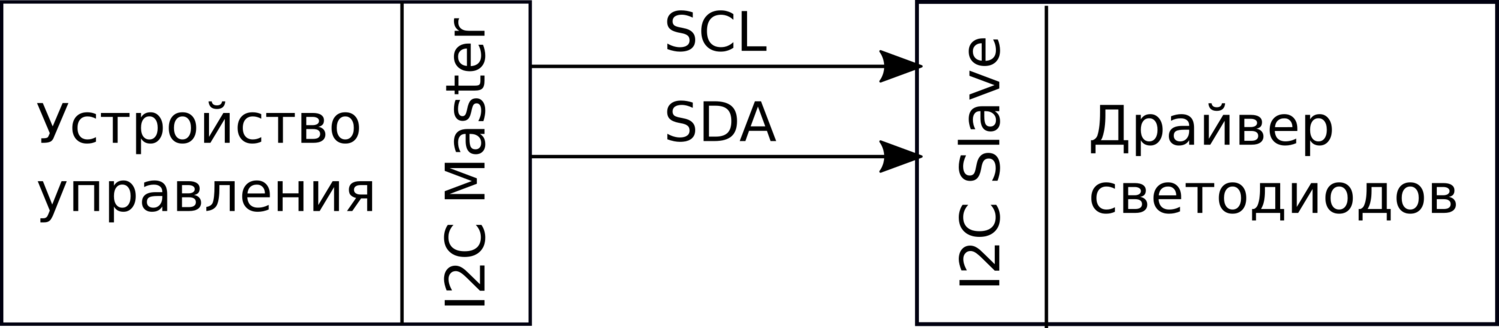

Сага о светодиодах. Часть 2. Разделяй и управляй

Это продолжение моего пути. Представлена часть 2 из раздела "Сага о светодиодах"

3050

0

0