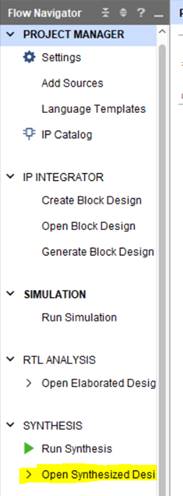

После окончания синтеза откройте синтезированный проект:

Рисунок 35 – Открытие результатов синтеза

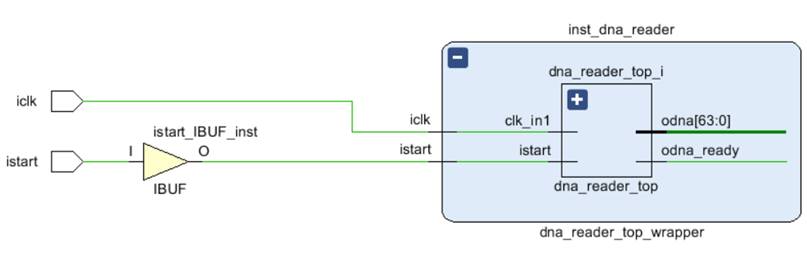

Обратите внимание: несмотря на то, что цепи от выводов odna[63:0] и odna_ready не подключены к внешним портам ввода/вывода, они не были исключены из проекта в ходе оптимизации, поскольку были отмечены для отладки в логическом анализаторе.

Рисунок 36 – Netlist проекта

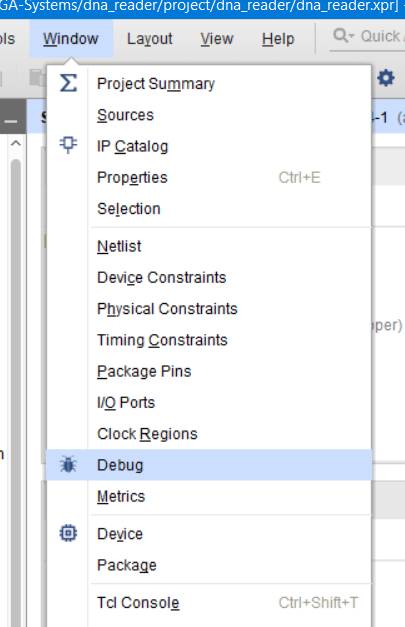

Теперь выполним настройку логического анализатора:

1. Откройте окно отмеченных для отладки цепей (Window → Debug):

Рисунок 37 – Открытие окна со списком цепей для отладки

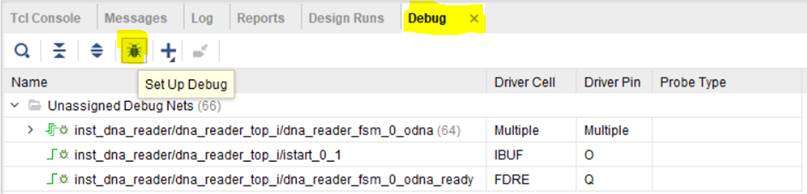

2. Запустите мастер настройки логического анализатора, нажав кнопку Setup Debug:

Рисунок 38 – Окно со списком цепей для отладки

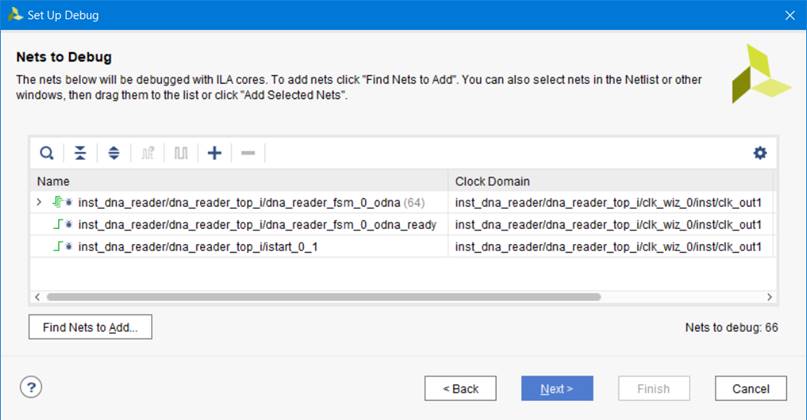

3. После появления мастера настройки нажмите Next. Перед вами появится окно настройки соответствия цепей и тактовых доменов, в котором Вы можете указать, по какому тактовому сигналу будет производиться выборка сигнала. Поскольку тактовый домен у нас один, оставляем всё без изменений. Нажимаем Next:

Рисунок 39 – Окно соответствия цепей и тактового домена

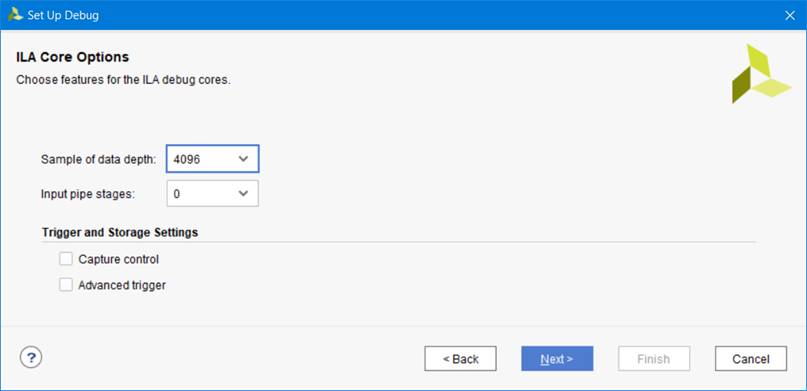

4. В этом окне указывается длина выборки – сколько отсчётов каждого сигнала нужно записать. Чем больше отсчётов, тем больше данных мы можем получить за один запуск логического анализатора, но и тем больше встроенной RAM ПЛИС логическому анализатору потребуется. Установите значение в «4096».

Рисунок 40 – Установка длины выборки

5. Нажмите Next и затем Finish.

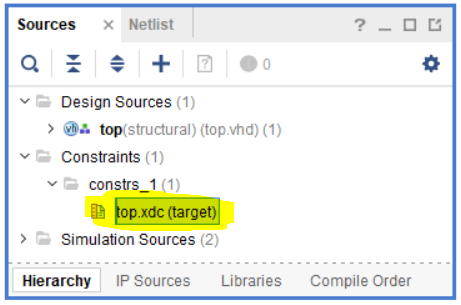

6. Сохраните сделанные изменения. Поскольку файл ограничений мы не создавали, Vivado предложит создать его и сохранить изменения в этот файл. Нажмите кнопку сохранения и затем OK.

Рисунок 41 – Созданный автоматически файл проектных ограничений

Настройка логического анализатора закончена. Теперь назначим ножки для iclk и istart.

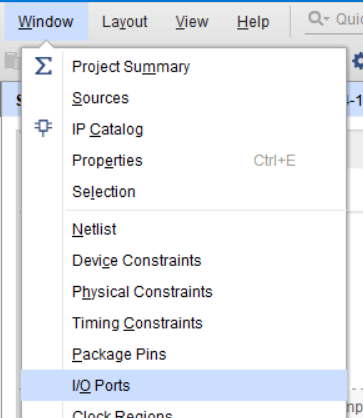

Для назначения ножек откройте окно I/O Ports (Window → I/O Ports)

Рисунок 42 – Вызов окна с настроек портов ввода/вывода

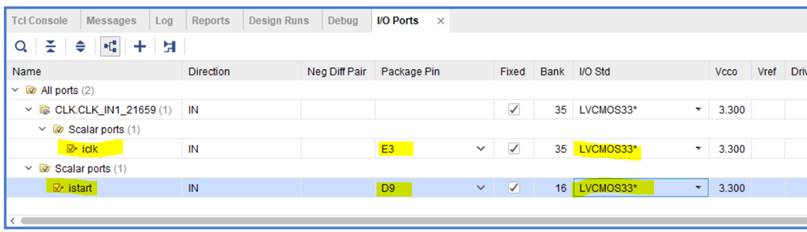

Установите значения для iclk и istart в соответствии с рисунком 43 и сохраните изменения.

Рисунок 43 – Настройки внешних портов для Arty Board

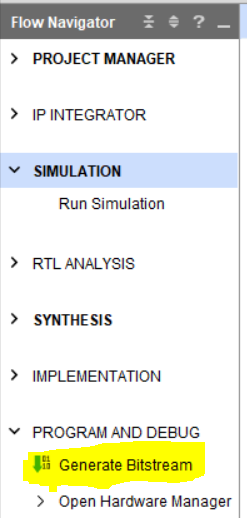

Теперь мы можем запустить имплементацию проекта и генерацию файла прошивки (bitstream). Нажимаем Generate Bitstream и ждём окончания выполнения операции.

Рисунок 44 –Запуск имплементации и генерации файла прошивки

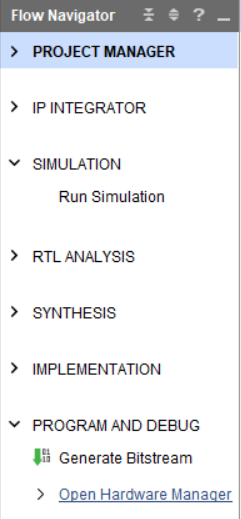

После окончания генерации файла прошивки FPGA открываем Hardware Manager:

Рисунок 45 – Открытие Hardware Manager

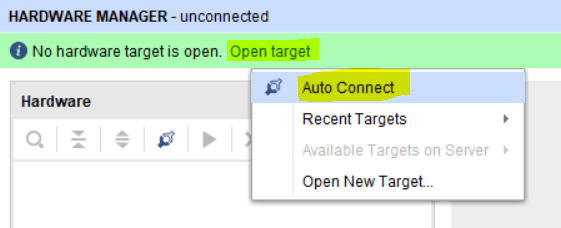

Подключите Arty Board к компьютеру.

Нажимаем Open target → Auto Connect:

Рисунок 46 –Обнаружение подключённых устройств

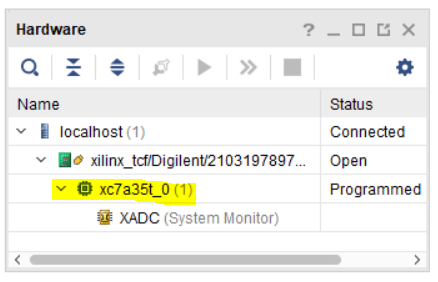

После сканирования кристалл, установленный на Arty, появится в списке подключённых устройств.

Рисунок 47 –Список обнаруженных устройств

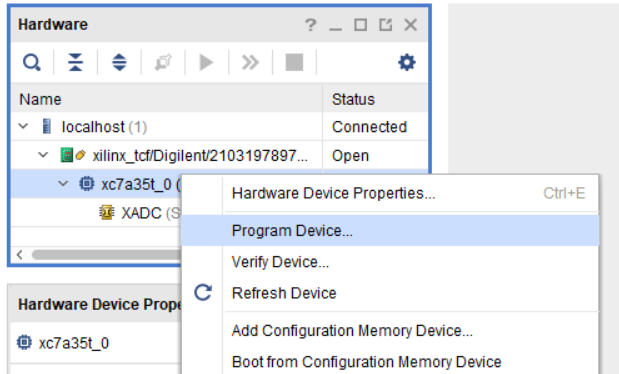

Для прошивки нашего кристалла нажимаем правой кнопкой мыши по обнаруженному устройству и выбираем Program Device:

Рисунок 48 – вызов окна программирования кристалла

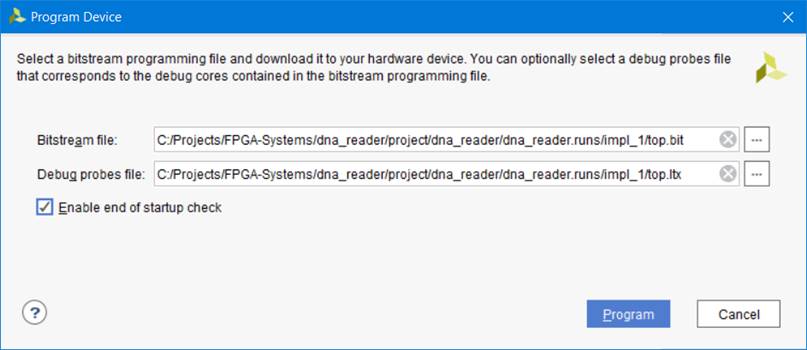

В появившемся окне необходимо указать bit-фал прошивки FPGA и список цепей, которые мы отметили для отладки. Как правило, эти поля заполняются автоматически, но на всякий случай проверьте, что подключаются именно нужные файлы.

Рисунок 49 – Окно выбора файла прошивки и файла со списком цепей для отладки

После окончания прошивки Vivado изменит представление на приспособленное для работы с логическим анализатором или отладки с помощью Logic Analyzer:

Рисунок 50 – Представление Vivado в режиме логического анализатора

Нам необходимо получить данные с цепей при определённом условии: когда сигнал запуска автомата istart станет равным «1». Это называется триггером, то есть условием, по которому будет начата запись. Пока условие не выполнено, запись не начнётся и логический анализатор будет находится в режиме ожидания выполнения соответствующего условия.

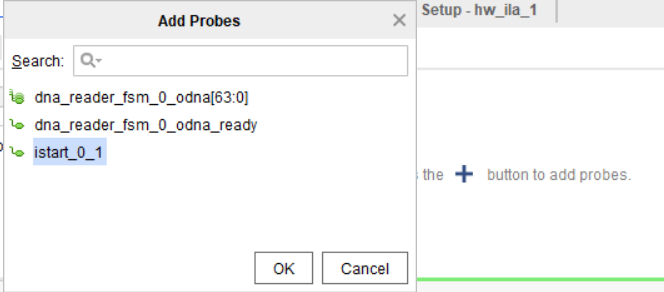

Для добавления условия срабатывания (т.е. триггера условия), нажмите на крестик в окне Trigger Setup, и выберите сигнал istart, затем нажмите ОК.

Рисунок 51 – Список доступных цепей, выбор триггера

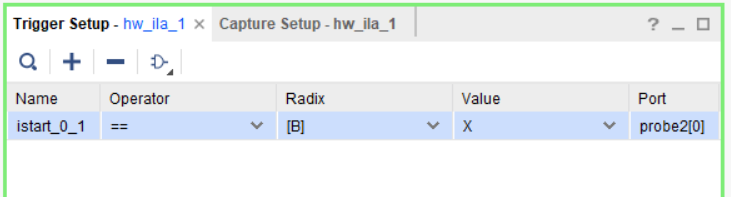

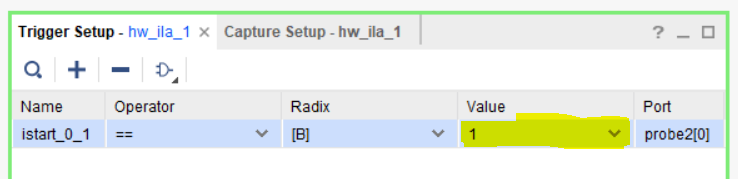

После этого istart появится в окне триггеров.

Рисунок 52 – Добавленная в определение триггера цепь

Теперь необходимо настроить условие для этого триггера. Сейчас поле Value имеет значение «х». Это означает, что запись состояний наблюдаемых цепей будет начинаться вне зависимости от состояния сигнала istart. Измените значение поля Value сигнала istart на «1».

Рисунок 53 – Настройка триггера (условия срабатывания)

У логического анализатора много настроек и много возможностей. В качестве триггеров можно использовать уровни сигналов и их фронты различной полярности, задавать срабатывание по цепочкам следующих друг за другом условий или логическим выражениям с ними. Есть даже возможность задания конечного автомата условий, имеющего свой собственный синтаксис и описание. Но это «задание со звёздочкой».

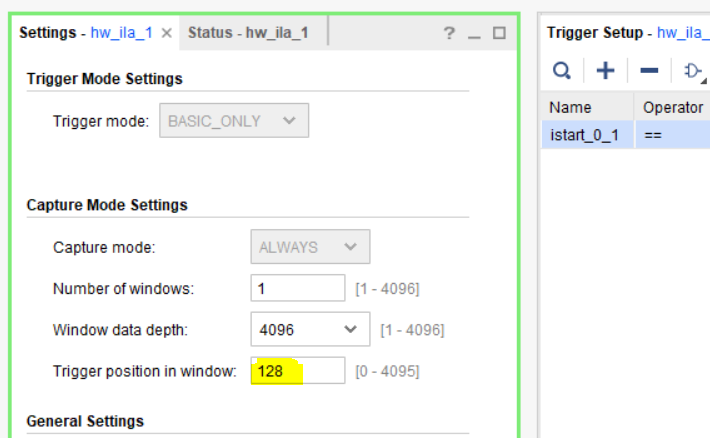

Здесь же мы рассмотрим ещё одну полезную функцию. Предположим, мы хотим посмотреть сигнал не только после срабатывания условия, но и за несколько отсчётов до этого момента – т. е. состояние линии до срабатывания условия. Сделать это можно, указав соответствующее количество отсчётов до момента срабатывания в поле Trigger positioning window. Сейчас это значение установлено в 128, что означает, что нам будет доступно состояние цепи за 128 отсчётов до срабатывания условия плюс оставшиеся отсчёты после срабатывания. Никакой магии «обращения времени назад» при этом нет: логический анализатор просто с самого момента запуска схемы постоянно пишет значения сигнала в кольцевой буфер, а по срабатыванию триггера – через фиксированное время останавливает запись и выдаёт пользователю результат.

Рисунок 54 – Окно настроек логического анализатора

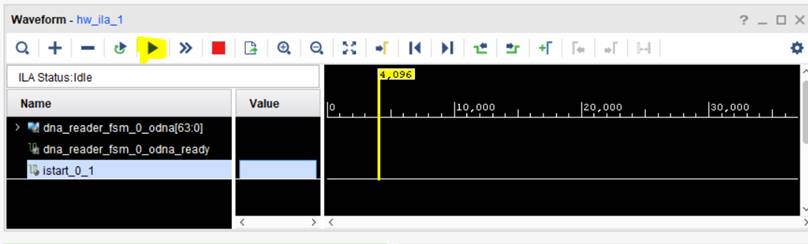

Для запуска логического анализатора нажмите на копку запуска, показанную на рисунке 55.

Рисунок 55 – Кнопка запуска логического анализатора

Логический анализатор окажется в режиме ожидания до тех пор, пока istart не перейдёт в «1».

Мы подключили istart к кнопке btn0, установленной на Arty. Нажмите её. Если всё до этого момента было выполнено корректно, на экране должна появится временнáя диаграмма.

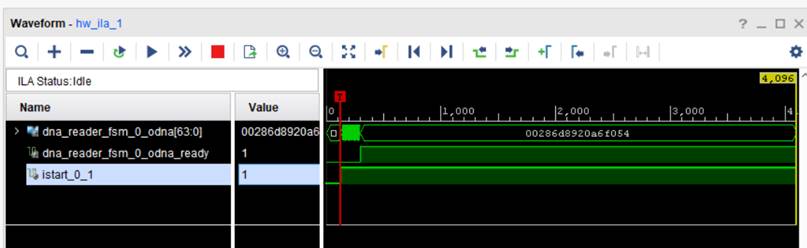

Рисунок 56 – Считанные значения цепей после срабатывания триггера

Значение odna[63:0] на этой временной диаграмме, естественно,у Вас будет другим, поскольку DNA уникальна для каждого кристалла (с учётом ограничений, о которых мы говорили).

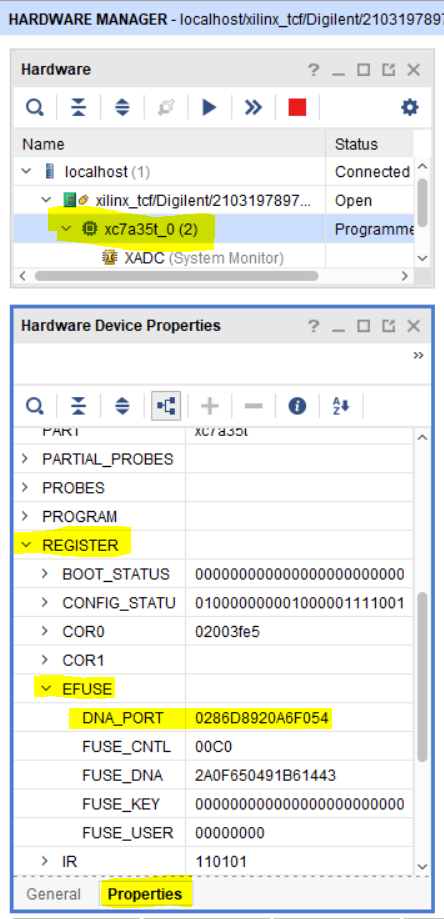

Как мы можем быть уверены, что это значение DNA является корректным, и мы считали его правильно? Если помните, DNA можно также прочитать, используя JTAG.

На самом деле все уже было прочитано Vivado в тот момент, когда мы выполняли поиск устройств по нажатию кнопки Autoconnect. Значение DNA может быть найдено следующим образом (см. рисунок):

1. Выберите подключённое устройство.

2. Перейдите во вкладку Properties.

3. Найдите поле Registers.

4. Затем EFUSE.

5. Потом DNA_PORT.

Рисунок 57 – Значение DNA, считанное через JTAG

А теперь сравните значение поля DNA_PORT с тем, что мы получили в логическом анализаторе. Если совпало, то ПОЗДРАВЛЯЮ ВАС! На этом можно закончить. Если же что-то не получилось – ещё раз внимательно всё проверьте или повторите. Если и это не помогает – оставьте комментарий или задайте вопрос на

www.fpga-systems.ru. Мы обязательно Вам поможем.

Каждая FPGA уникальна. Уникальны как её номер, так и её свойства. Нужно ли Вам использовать DNA в своих проектах, решать Вам. Но, не сомневайтесь, этой статьи не было бы, если бы DNA никто не использовал. Кто-то применяет её для защиты проектов, кто-то – для контроля версий… А для чего DNA FPGA может пригодиться Вам? Напишите об этом в комментариях к данной статье на

www.fpga-systems.ru. Не забудьте сделать и домашнее задание. Удачи!

1. Выполните реализацию других схем включения DNA_PORT.

2. Настройте триггер логического анализатора на сигнал odna_ready за 1234 отсчёта до его срабатывания. (Учтите, что для перезапуска потребуется заново прошить FPGA, поскольку автомат управления не имеет условия возврата к начальному состоянию, из которого происходит его запуск по istart).

3. * (повышенной сложности) Получить DNA можно и через JTAG. Попробуйте получить DNA c использованием Tcl-команд.

4. ** (высокой сложности) Считайте все значения EFUSE-регистров с помощью Tcl-скрипта и сформируйте результаты в удобочитаемый отчёт.

1.

UG470 7 Series FPGAs Configuration.

2.

UG953 Vivado Design Suite7 Series FPGA and Zynq-7000 All Programmable SoC Libraries Guide.3.

DS181 Artix-7 FPGAs Data Sheet: DC and AC Switching Characteristics.

4.

UG835 Vivado Design Suite Tcl Command Reference Guide.

5.

UG894 Using Tcl Scripting.

7.

Описание Arty Board на сайте Digilent.

8.

UG908 Programming and Debugging.

Список тренингов по проектированию на FPGA в сертифицированном тренинг центре компании Xilinx:

Скачать статью в формате pdf

Скачать файлы проекта