Архив новостей из мира FPGA

Tachyssema Developpement 201

691

0

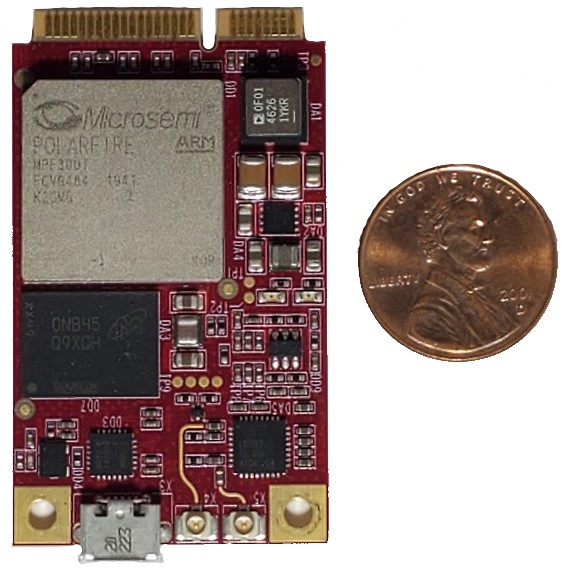

Модуль ввода-вывода и обработки Mini PCIe на базе FPGA Microsemi PolarFire MPF300T-1FCVG484

810

0

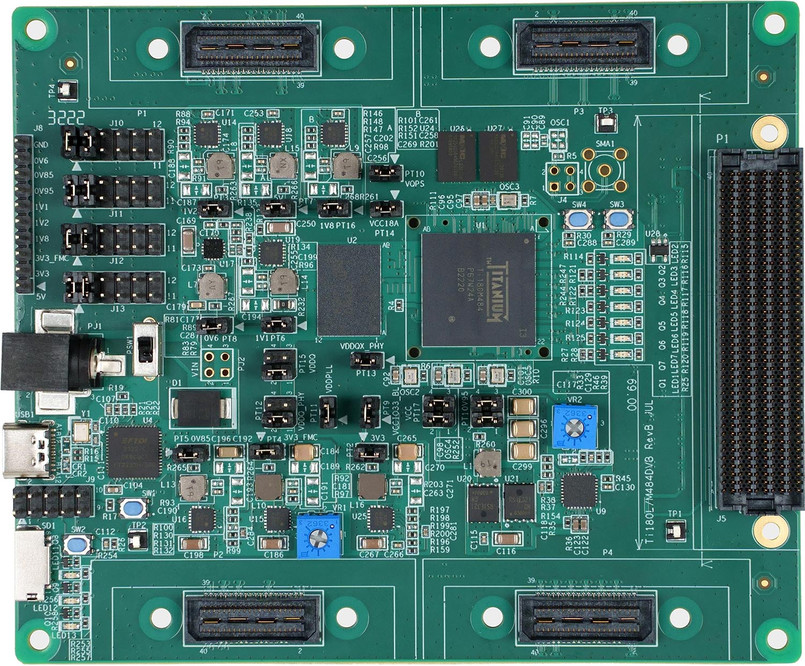

Девкит Titanium Ti180 M484 от Efinix

Набор для разработки Titanium Ti180 M484 содержит все необходимое для разработки и создания прототипов на ПЛИС Ti180. Этот комплект имеет MIPI D-PHY Ti180, поддерживающий скорость до 2,5 Гбит/с на полосу, и контроллеры LPDDR4x. У ... Читать дальше »

1029

0

Ускорение электронной торговли с помощью новой серии Alveo™ X3

Сегодняшние ведущие маркет-мейкеры, хедж-фонды и биржи требуют исполнения сделок с низкой задержкой и управления рисками для получения конкурентных преимуществ. Новая серия Alveo™ X3 — это первые сетевые карты AMD, разработанные с использованием screened FPGA (напишите в комментах что за screened FPGA) и оптимизированные специально для торговли с низкой задержкой. В настоящее время карты в производстве и отгружаются. ... Читать дальше »

855

0

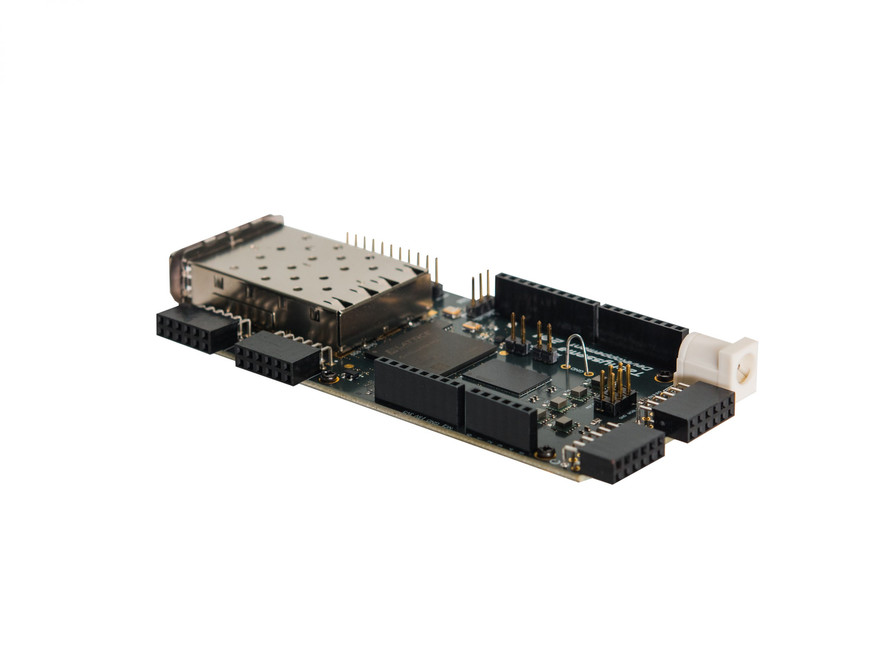

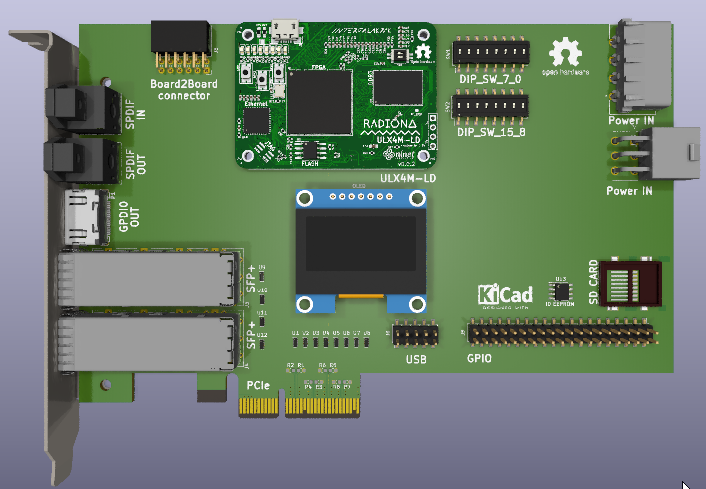

OpenSource отладка ULX4M-PCIe-IO

Компания NLnet выложила в открытый доступ исходники в KiCad несущей платы для другого opensource модуля ULX4M ... Читать дальше »

736

0

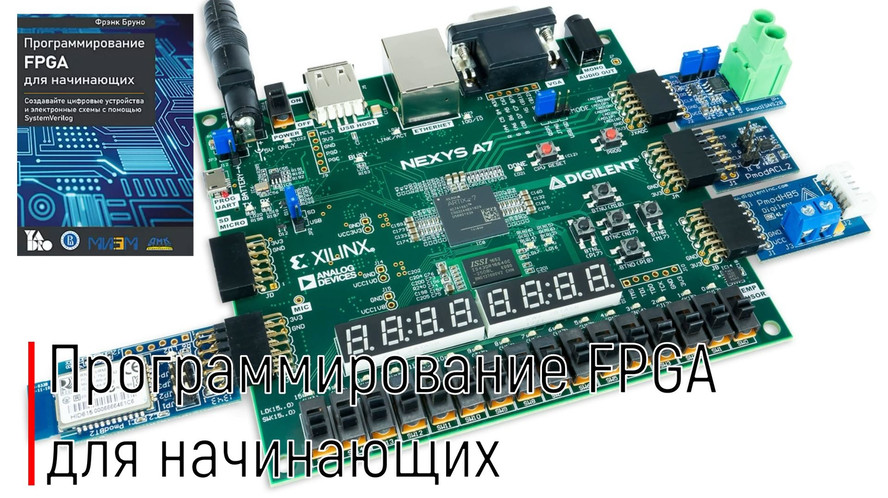

Книга: Программирование FPGA для начинающих

Затем вы узнаете о том, как создавать проект ... Читать дальше »

1660

2

|

0