Clock Domain Crossing

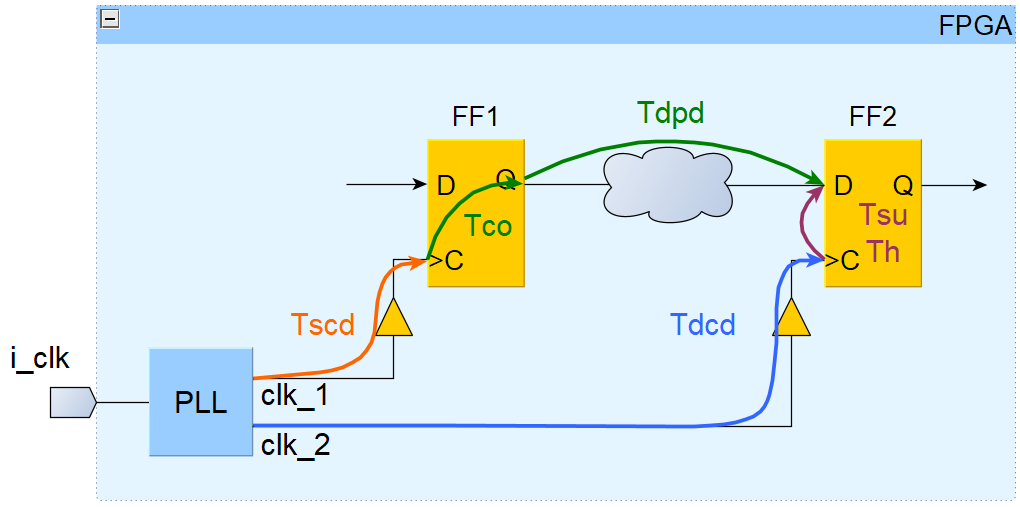

The primary goal in safely implementing any IC or FPGA project is to achieve a synchronous design. This implies that the relationship of all clocks and asynchronous resets to each other is defined in the synthesis constraints. Incorrect handling of clock-domain crossing (CDC) is probably the primary cause of sporadic errors, which are impossible to catch in a digital simulation and can cause a system to inexplicably fail in the field.

This webinar discusses situations in which CDC problems can occur and more importantly presents solutions for the most frequent scenarios.

Topics include:

-

What causes metastability

-

How to correctly implement CDC logic for simple signals, complex data and counters

-

How to use Synopsys Design Constraints (SDC) to ensure that static timing analysis (STA) produces reliable results in the context of multi-clock designs

The webinar will also feature a working example from Microchip® using PolarFire® FPGAs and SoCs and the Libero® SoC Design Suite.

Wednesday, November 06, 2024

Time: 10-11am (GMT) 11-12pm (CET) 3.30-4.30pm (IST)

Americas

Wednesday, November 06, 2024

Time: 10-11am (PST) 11-12pm (MST) 12-1pm (CST) 1-2pm (EST)