Архив новостей из мира FPGA

Вебинар: Автоматизированное регрессионное тестирование для VHDL/Verilog

... Читать дальше »

1147

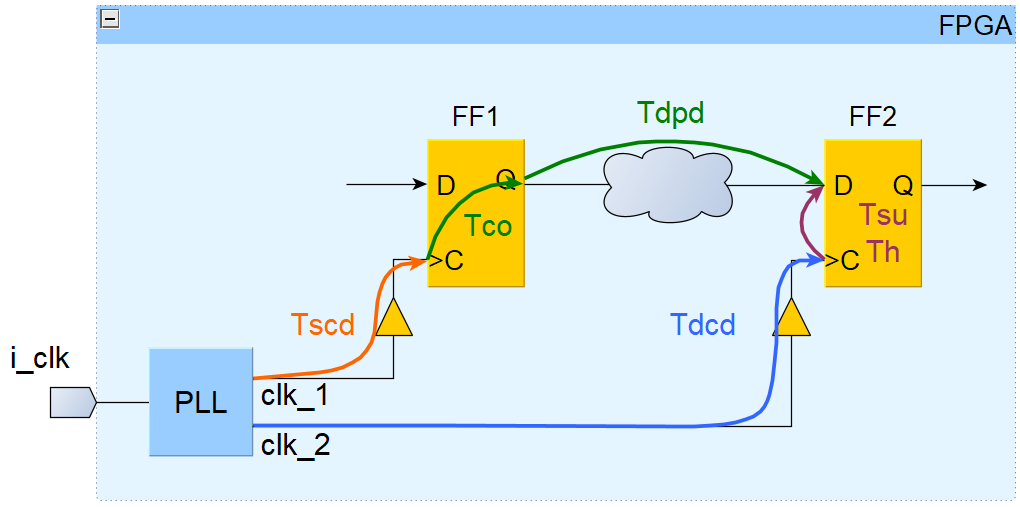

Clock Domain Crossing

The primary goal in safely implementing any IC or FPGA project is to achieve a synchronous design. This implies that the relationship of all c ... Читать дальше »

3704

0

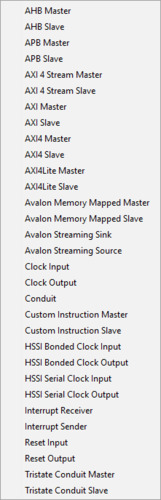

Статическая и динамическая верификация CDC для IP-блоков на основе AXI4 Stream

Протокол AXI4 Stream используется как стандартный интерфейс для обмена данными между подключенными IP-блоками внутри проектов FPGA. Для пересечения тактовых доменов AXI4 Stream использует коммутаторы, способные передавать данные в другой асинхронный тактовый домен. Альтернативным решением является двухпортовый AXI4 ... Читать дальше »

3902

0

Разработка и развитие Verilog и SystemVerilog

SystemVerilog - это Verilog нового поколения с модным маркетинговым названием. В SystemVerilog использованы многие возможности других языков и методологий. Возможности на основе классов, ограниченное выборочное тестирование (CRT) и функциональный охват были добавлены в SystemVerilog и включены в Универсальную методо ... Читать дальше »

4135

0

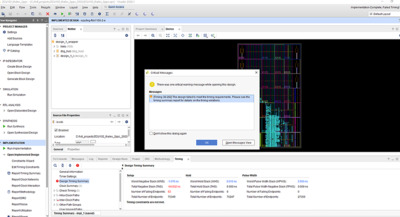

Ускорение разработки на SoC и FPGA с помощью Vitis™ Model Composer и Vivado™ Design Suite

Vitis ™ Model Composer предоставляет собой среду для разработки алгоритмов и среду проектирования на основе моделей. Vitis Model Composer также предлагает различные методы для ускорения процесса разработки и упрощения интеграции сложных IP-ядер в проекты. На этом вебинаре мы рассмотрим: ... Читать дальше »

7941

0

GOWIN Semiconductor приглашает на вебинар по i3c .

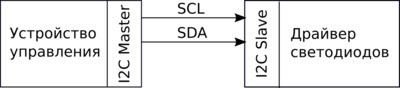

GOWIN Semiconductor приглашает на вебинар по i3c . Компания GOWIN Semiconductor рада представить клиентам FPGA семейство продуктов I3C IP. На протяжении десятилетий I2C был широко используемым интерфейсом в электронной промышленности для настройки, сенсорного интерфейса и других приложений с низкой про ... Читать дальше »

7506

0

Двухдневный семинар "Использование приложений видения с KRIA" (день 2)

Этот семинар посвящен Kria ™ System-on-Module (SOM) и Kria KV260 Vision AI Starter Kit от AMD Xilinx. Мы расскажем как ускорить работу vision-приложений, используя KV260 Starter Kit прямо из коробки без каких-либо знаний FPGA.

7017

0

Двухдневный семинар "Использование приложений видения с KRIA" (день 1)

Этот семинар посвящен Kria ™ System-on-Module (SOM) и Kria KV260 Vision AI Starter Kit от AMD Xilinx. Мы расскажем как ускорить работу vision-приложений, используя KV260 Starter Kit прямо из коробки без каких-либо знаний FPGA.

6921

0

Начало работы с UVM

Цель вебинара предоставить вам базу для начала изучения UVM, начиная с того, почему стоит ее использовать заканчивая описанием ключевых компонентов UVM тестбенча. На вебинаре будет представлен обзор интерфейса DUT и его взаимодействие между секвенсором и драйвером. Мы рассмотрим:

7029

0

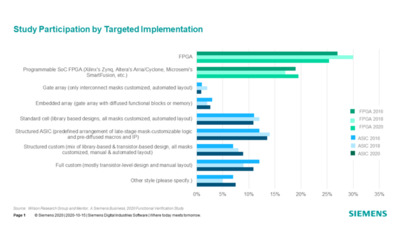

Высокоуровневый синтез для исследования архитектуры аппаратного/программного обеспечения для инференса

Периферийные устройства всех типов становятся умнее, благодаря способности слушать нас, понимать наши жесты и даже распознавать нас. Этот интеллект исходит из возможностей глубоких нейронных сетей. Обработка данных требует больших вычислительных затрат и может легко перегружать встроенные процессоры при огранич ... Читать дальше »

6850

0 |

0