Архив новостей из мира FPGA

Онлайн викторина по электронике

Уважаемые коллеги! Приглашаем вас принять участие в предновогодней викторине по электронике! Это мероприятие проводится в рамках проекта «Учим электронике». Онлайн викторина пройдёт 18.12 (суббота) в 14.00 по московскому времени на базе Томского политехнического университета. Вспомним основные разделы электроники и разыграем призы. Подключайтесь, скучно не будет. ... Читать дальше »

1214

Цифровые фильтры на ПЛИС. С чего начать

В эту субботу Томский политех открывает серию вебинаров по цифровой обработке сигналов на ПЛИС. ... Читать дальше »

1469

0

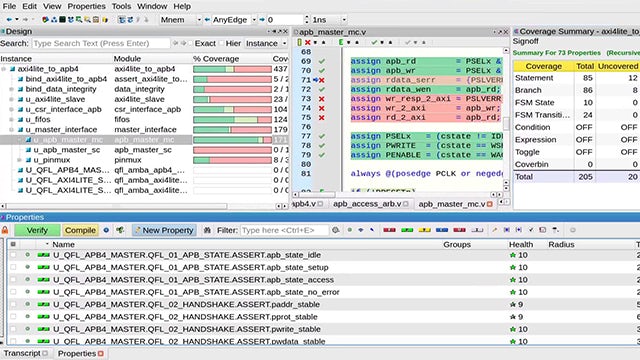

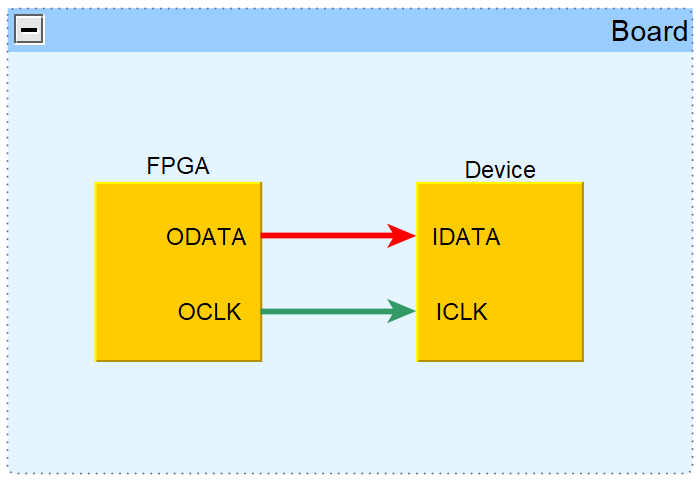

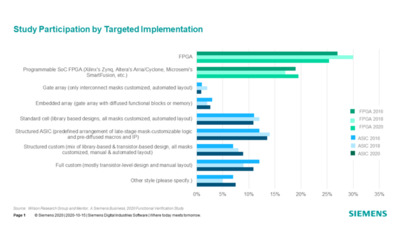

Платформа прототипирования СБИС и СФ-блоков от Siemens EDA

Вне зависимости от того, какой тип изделия вы разрабатываете, будь то процессор, ASIC / СБИС, сложно функциональный (IP) блок, или же изделие на базе FPGA, важнейшим этапом верификации разрабатываемого продукта является прототипирование. Прототипирование может быть реализовано на различных аппаратных конфигурациях и технологиях, но мировой опыт показывает, что прототипирование на базе ПЛИС стало стандартом де-факто, благодаря гибкости, модульности и масштабируемости. ... Читать дальше »

1464

0

Сто вопросов к основателю FPGA комьюнити

Всем PnR! Проект FPGA-Systems скоро отпразднует своё пятилетие. И команда Томского Политехнического Университета, которая недавно начала выпускать ролики по ПЛИС, предложила провести интервью с основателем FPGA комьюнити. Если вам интересно узнать об истории проекта FPGA-Systems, его кома ... Читать дальше »

1235

0

Вебинар «Разработка на ПЛИС с применением IP-ядер российского производства»

Вебинар «Разработка на ПЛИС с применением IP-ядер российского производства».

1223

0

Вебинар о инструментах разработки на языках C и C++ для ПЛИС Microchip — 16 и 17 ноября в 15.00(мск)

16 и 17 ноября пройдёт вебинар, посвященный малопотребляющим ПЛИС, и инструментам для разработки от Microchip, в том числе, о генераторе RTL-кода - Smart HLS.

1164

0

Как быстро завершить верификацию CDC+RDC с помощью иерархических методологий

Методологии разработки, которые не соответствуют возрастающей сложности и размеру проекта, в конечном итоге не дадут результатов. Иерархические методологии верификации дают возможность разделить и покорить более крупные и сложные проекты. Однако, если проект для анализа разбивается на части, то возникают рискованные компромиссы – страдает либо точность, либо производительность. На этом вебинаре будут показаны способы решения сложных задач проектирования с помощью иерархического подхода, который не теряет точности и производительности. ... Читать дальше »

1214

0

Formal 101 - Независимость от данных и Non-Determinism

На прошлом вебинаре “Formal 101 – Basic Abstraction Techniques” мы показали, как применять проверенные временем методы для безоп ... Читать дальше »

941

0

Проходим туториал по Questa Sim - FPGA Monkey Stream #36

Questa Sim и Model Sim - наверное один из самых популярных third-party симуляторов, который используется при разработке на FPGA. Это очень мощный инструмент, который при первом взгляде на его интерфейс, заставляет почувствовать боль, ужас и угнетение. Но за этой архаичной оболочкой, скрывается настолько потрясный функционал, что отвращением от GUI можно пренебречь. Самое сложное при работе с новым инструментов - это понять как он работает, а для этого в Questa есть отличный 300 страничный туториал из 20 лабораторок, который мы с вами и будем проходить на этом стриме. ... Читать дальше »

3008

0

Понимание стабильности рандомизации в SystemVerilog и UVM

Распространенной проблемой при накладывании ограничений на рандомизацию при моделировании является последующая возможность точного воспроизведения случайных воздействий для отлаживаемых объектов и запрета регрессионных тестов . Это особенно проблематично, когда исходный код нуждается в изменении, а сама проблема известна как стабильность случайности (стабильность рандомизации, random stability) На этом вебинаре, мы объясним: ... Читать дальше »

915

0 |

0