Разработка процессорной системы на базе софт-процессора MicroBlaze в среде Xilinx Vivado IDE/HLx. Часть 2.

Оглавление (кликабельно)

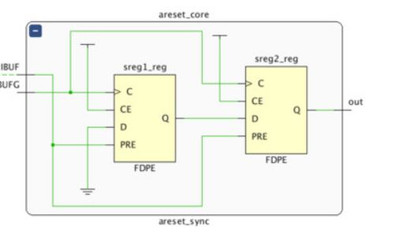

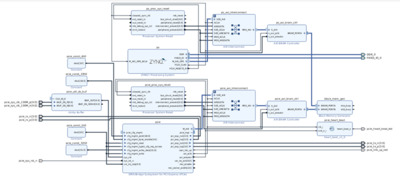

HW/SW части процессорной системы (см. Часть 1)

Создание нового проекта (см. Часть 1)

Создание HW-части (см. Часть 1,2)

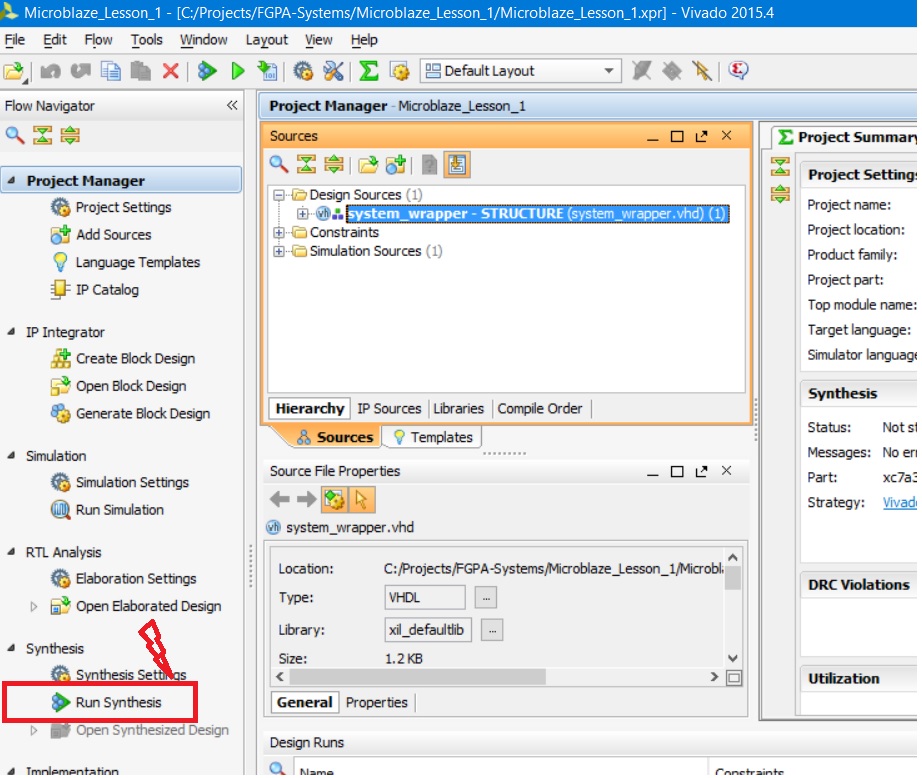

После создания обёртки наш модуль можно наконец-то запустить на синтез, нажав на кнопу Run Synthesis (рис. 40).

Рисунок 40. Запуск синтеза проекта

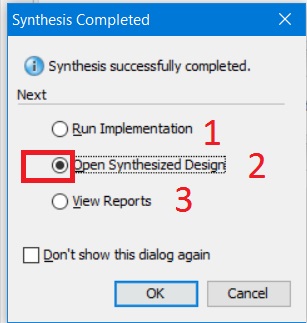

После окончания синтеза появится окно выбора действия (рис. 41):

Рисунок 41. Действие после синтеза

Окно, появляющееся после синтеза, предлагает выполнить:

1. Запустить имплементацию.

2. Открыть синтезируемый проект (Выберите этот пункт).

3. Просмотреть отчёты.

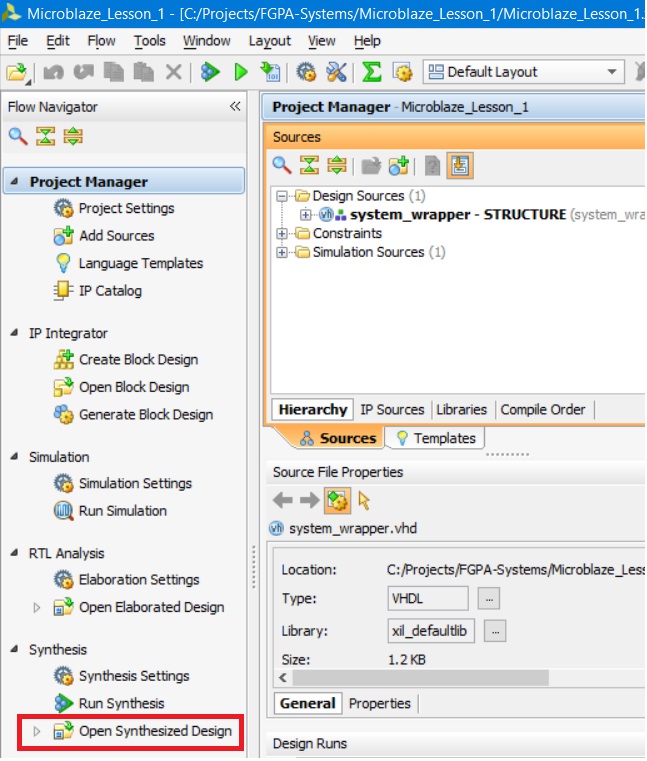

Выберите второй пункт – открыть синтезированный проект. Если Вы машинально закрыли окно на рис. 41, то можно открыть синтезированный проект другим способом – нажав на кнопку Open Synthesized Design, которая находится под кнопкой запуска синтеза (рис. 42). Обратите внимание, что кнопка Open Synthesized Design активна, если только у Вас есть результат синтеза; если проект не синтезирован, кнопка будет неактивна (см. рис. 40, где результатов синтеза ещё нет).

Рисунок 42. Кнопка открытия синтезированного проекта

Открытие синтезированного проекта нужно для двух вещей:

1. Проанализировать проект (если есть желание).

2. Выполнить назначение портам нашего проекта физических ножек FPGA.

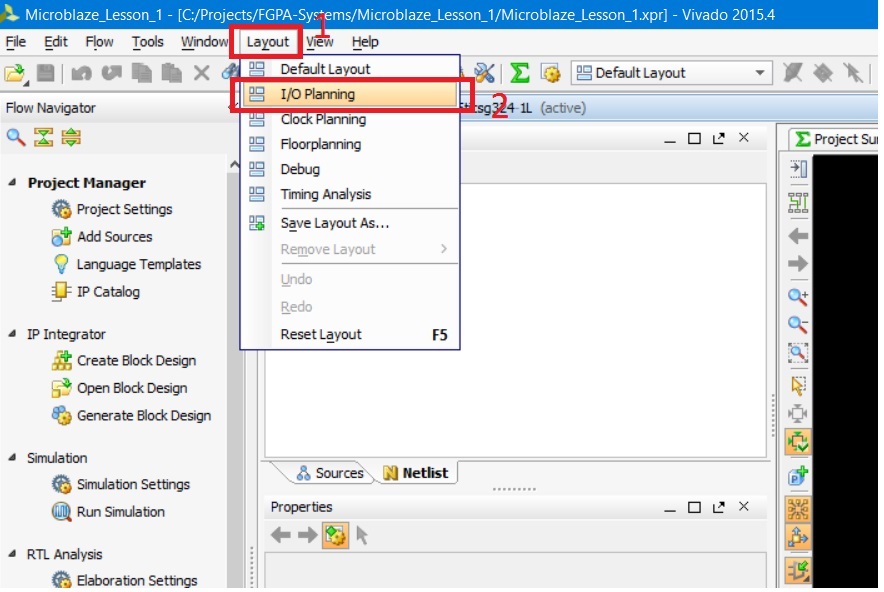

До текущего момента физически мы ещё не указывали, к каким ножкам подключить нашу HW-часть. Сделаем это сейчас в модуле I/O Planning. Чтобы его запустить, необходимо при открытом уже синтезированном проекте выбрать в меню Layout пункт I/O Planning (рис. 43).

Рисунок 43. Открытие модуля планировщика выводов FPGA (обязательно должен быть открыт синтезированный проект, в противном случае планировщик может быть недоступен).

Если всё сделано корректно, то должен открыться планировщик выводов (рис. 44).

Рисунок 44. Вид окна планировщика выводов с раскрытым списком портов модуля верхнего уровня нашего проекта

Теперь мы можем выполнить назначение физических ножек FPGA портам нашей процессорной системы. Сделать это можно многими способами. Один из них – явно заполнить необходимые поля. Нас будут интересовать только поля Site – название контакта FPGA и I/O Std – стандарт ввода-вывода, определяющей напряжения логических уровней и другие электрические параметры. Обратите внимание, что если Ваша плата – не Arty Board, то содержимое этих двух колонок может быть другим; надеюсь, Вы сможете прочитать принципиальную электрическую схему Вашей платы и указать во всех полях правильные значения. Для Arty Board они показаны на рис. 45.

Рисунок 45. Подключение портов к ножкам FPGA для Arty Board

Обратите внимание, что значки портов после выполнения назначений стали жёлтыми, а не серыми.

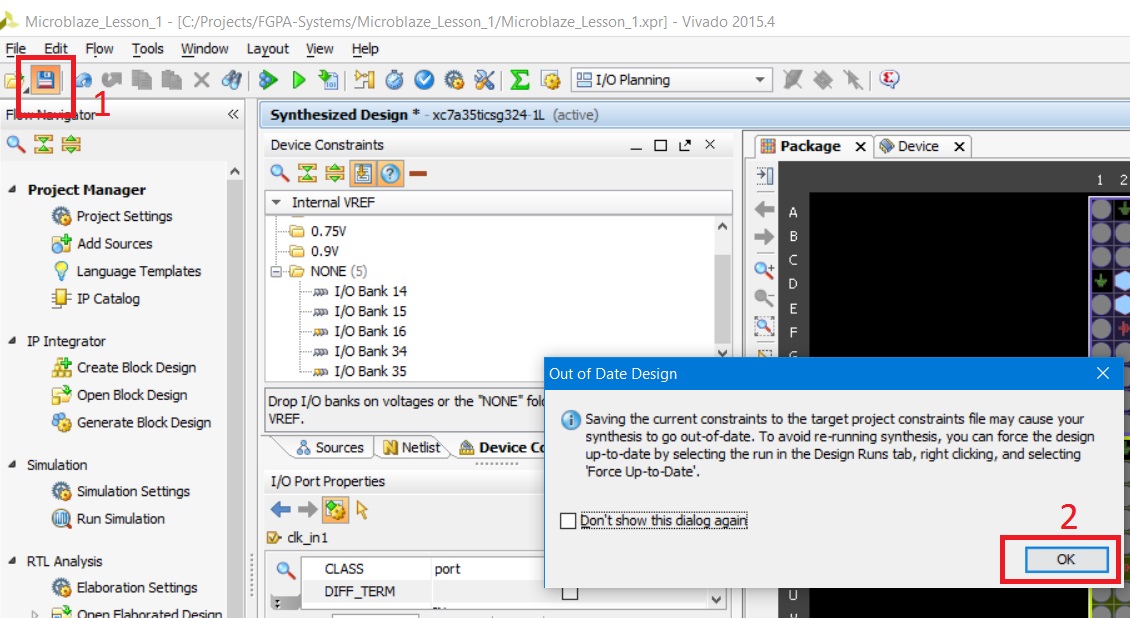

Сохраним результаты назначения, нажав кнопку сохранить (рис. 46). После нажатия на неё появится окно, которое говорит, что сохранение возможно приведёт к необходимости повторного синтеза. Нажимаем OK.

Рисунок 46. Сохранение в планировщике выводов произведённых изменений.

Сохранение параметров назначений ножек производится обычно в файл формата (и расширения) xdc – Xilinx Design Constraints. Его мы ешё не создавали, поэтому Vivado предлагает нам создать новый файл для сохранения (рис. 47).

Рисунок 47. Окно создания файла для сохранения результата

В окне, показанном на рис. 47:

1. Тип файла. Выберите XDC – Xilinx Design Constraint – файл с настройками для проекта

2. Имя файла; наберите constr.

3. Расположение файла – оставьте по умолчанию.

4. Нажмите OK.

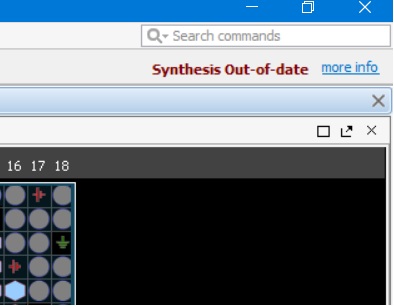

После сохранения результатов необходимо выполнить синтез проекта заново, о чём говорит надпись Synthesis Out-of-Date в правом верхнем углу (рис. 48).

Рисунок 48. Результаты синтеза устарели, синтез необходимо выполнить заново: Synthesis Out-of-date

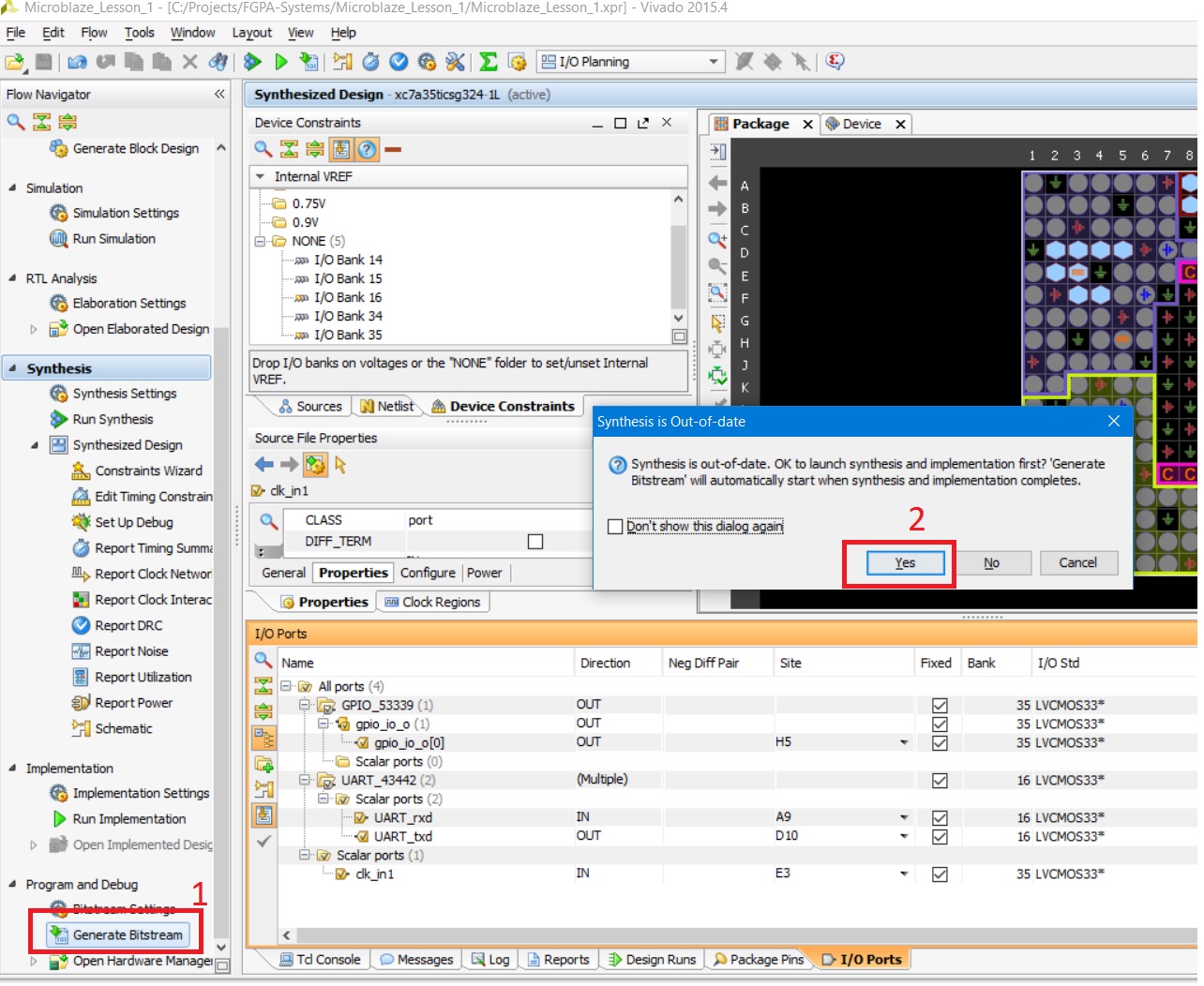

Мы позволим Vivado заново выполнить синтез, но в этот раз запустим не просто синтез, а сразу генерацию битстрима – bit-файла. При этом Vivado «увидит», что результатов синтеза и имплементации нет, и предложит выполнить их в автоматическом режиме, прежде чем сгенерировать bit-файл (рис. 49).

Нажмите Generate Bitstream и затем, когда Vivado предложит выполнить синтез и имплементацию перед запуском генерации bit-файла – нажмите Yes.

Рисунок 49. Запуск генерации bit-файла и окно, предупреждающее что сначала будут выполнены синтез и имплементация

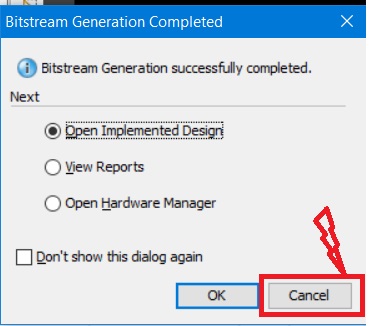

Теперь нам нужно ждать окончания генерации bit-файла. Это может занять минут 10-15 в зависимости от Вашего компьютера. По окончании генерации bit-файла появится окно (рис. 50), предлагающее выполнить одно из действий. Нам ничего дальше делать не нужно, поэтому его просто закрываем.

Рисунок 50. Окно завершения генерации bit-файла. Мы делать дальше ничего не будем, поэтому нажимаем кнопку Cancel.

На этом сборка HW-части закончена… Переходим к SW.

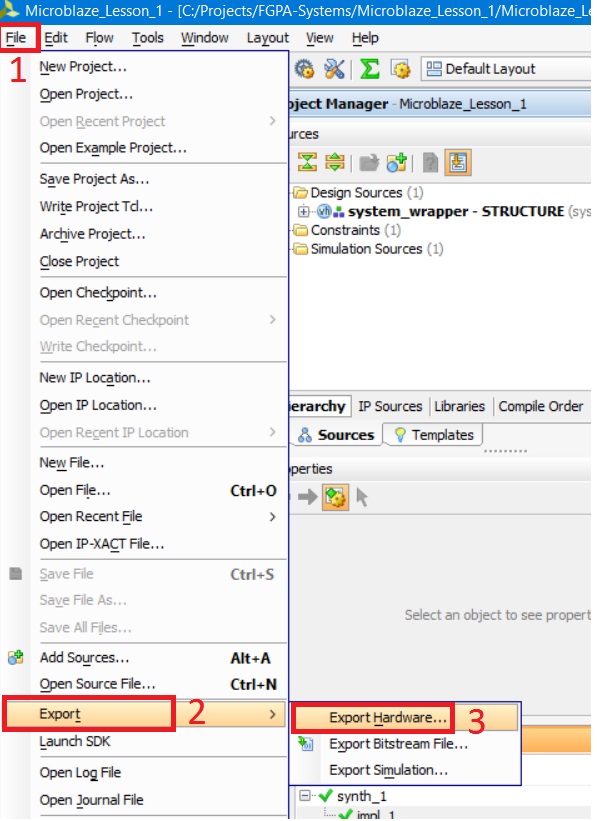

SW-часть (программная) необходима, чтобы «оживить» нашу собранную процессорную систему. Сейчас это просто кусок «железа», который не выполняет никаких действий. Как уже было сказано выше, разработка программной части выполнятся в среде Xilinx SDK, которая есть по сути Eclipse с плагинами от Xilinx. Разумеется, что Xilinx уже автоматизировал часть процесса написания программы и подготовил некоторые исходные файлы и библиотеки, так что писать мы будем не «с нуля». Сейчас нам необходимо передать Xilinx SDK информацию об аппаратной «начинке» нашей процессорной системы: какие использованы устройства, какова их конфигурация и адреса и т.д. В общем – выполнить экспорт нашей аппаратной (HW) части. Сделать это можно, выбрав в левом верхнем углу File-Export-Export Hardware (рис. 51).

Рисунок 51. Экспорт HW-части проекта в Xilinx SDK

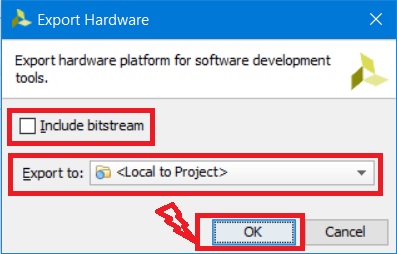

После этого появится окно (рис. 52), в котором указывается, нужно ли экспортировать bit-файл, и какую папку выбрать в качестве рабочей. Оставим все настройки в состояниях по умолчанию; bit-файл экспортировать сейчас не надо, мы добавим его позже. Нажимаем OK.

Рисунок 52. Параметры экспорта HW части

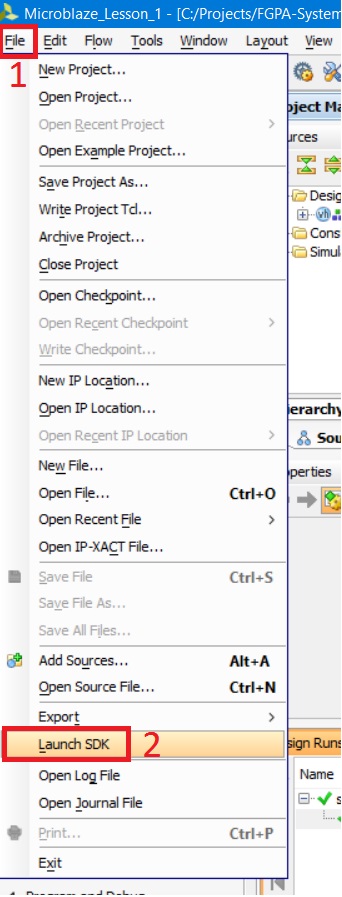

Теперь запускаем программу Xilinx SDK. Сделать это можно через главное меню Windows или из-под Vivado – просто выберите в левом верхнем углу File-Launch SDK (рис. 53).

Рисунок 53. Запуск Xilinx SDK из-под Vivado

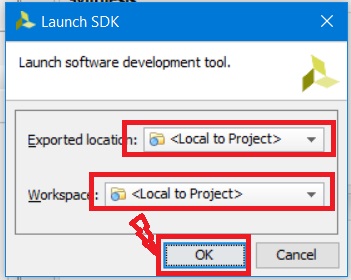

Теперь Vivado просит указать параметры запуска SDK; отставим их по умолчанию и нажмём OK (рис. 54):

Рисунок 54. Параметры запуска Xilinx SDK

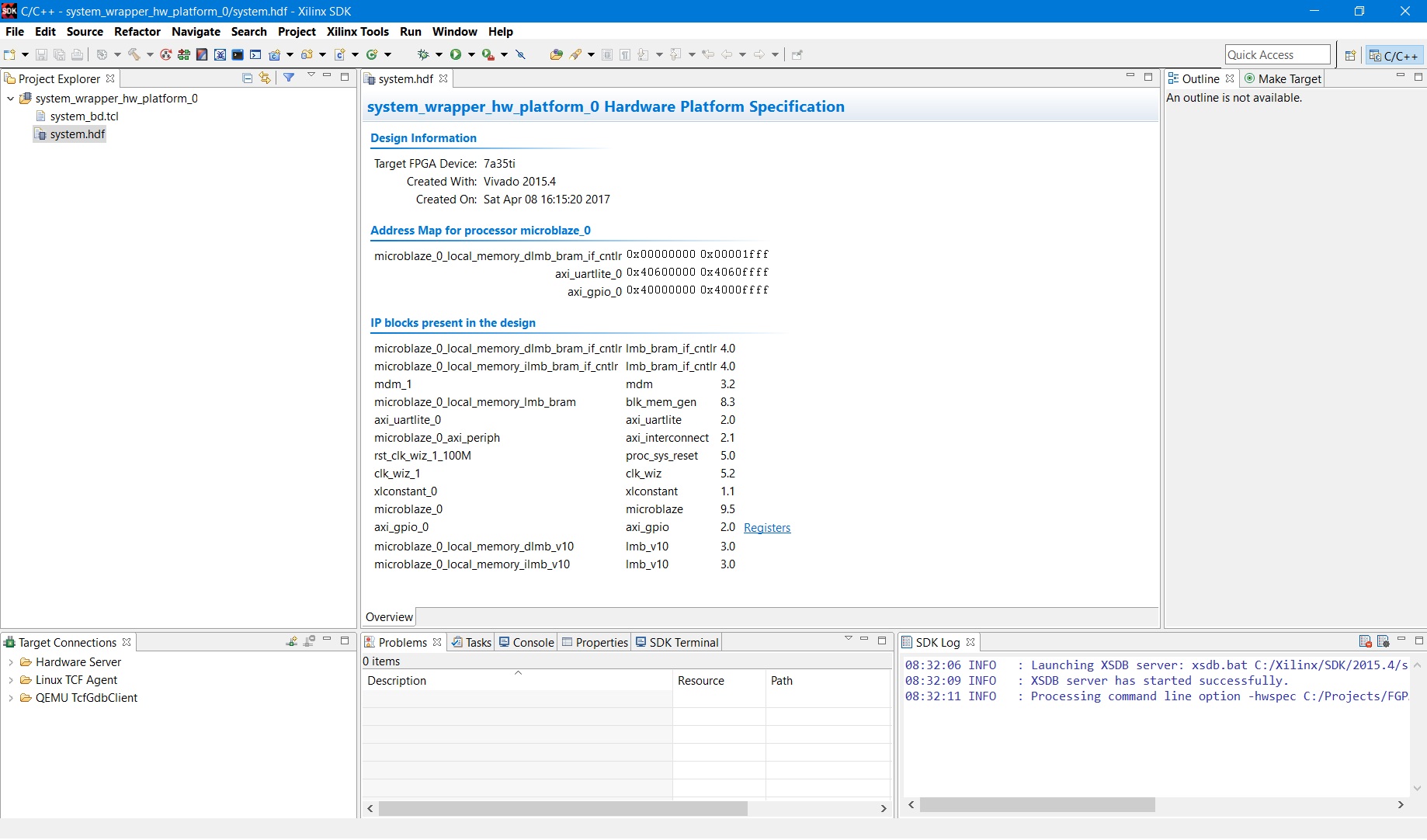

Если все сделано правильно, должно появиться окно, как на рис.55. Это и есть Xilinx SDK.

Рисунок 55. Основное окно Xilinx SDK

Сейчас мы не будем разбирать назначение каждого из внутренних окон системы, поскольку это выходит за рамки данной статьи. Единственное, о чём я могу упомянуть – так это о том, что у Xilinx SDK очень-очень-очень хорошая справка (рис. 56). Если у Вас возникают вопросы, в основном все ответы лежат в справке. Не поленитесь, ознакомиться с ней, если будет время.

Рисунок 56. Вызов справки Xilinx SDK

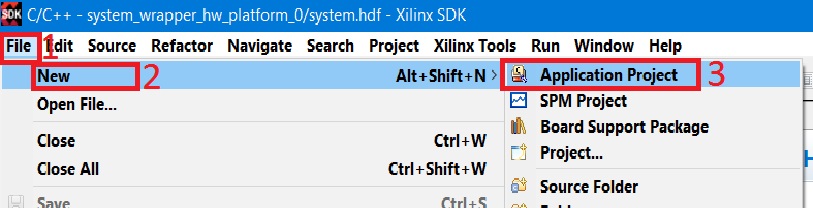

Приступим к созданию проекта. Выбираем File-New-Application project

Рисунок 57. Создание нового проекта в Xilinx SDK

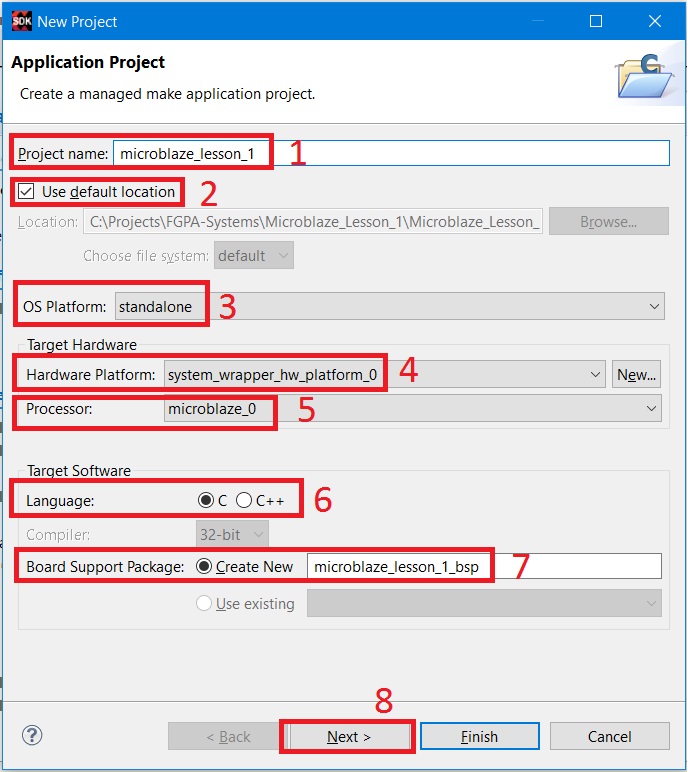

Задаём основные параметры проекта (рис. 58):

Рисунок 58. Параметры нового проекта

На рис. 58:

1. Название проекта.

2. Место расположения проекта (выставляем используемое по умолчанию).

3. Тип используемой в проекте операционной системы (без ОС – standalone).

4. Аппаратная конфигурация (если процессоров системе несколько, то будет список; у нас – только один).

5. Идентификатор процессора (актуально для многопроцессорных систем).

6. Язык программирования (C).

7. Пакет драйверов (создаём новый на основании информации о HW-части).

8. Нажимаем Next.

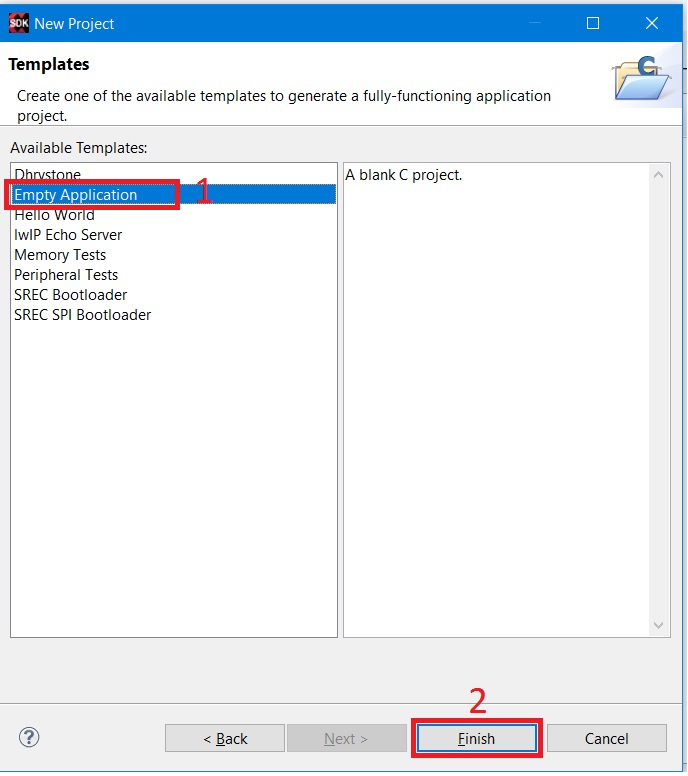

Теперь SDK предлагает выбрать один из нескольких готовых вариантов приложения (application), включая Hello, world (рис. 59). Мы же с Вами, для более подробного знакомства со структурой приложения, выберем пустое приложение (Empty Application), нажимаем Finish

Рисунок 59. Выбор типа проекта – пустой проект

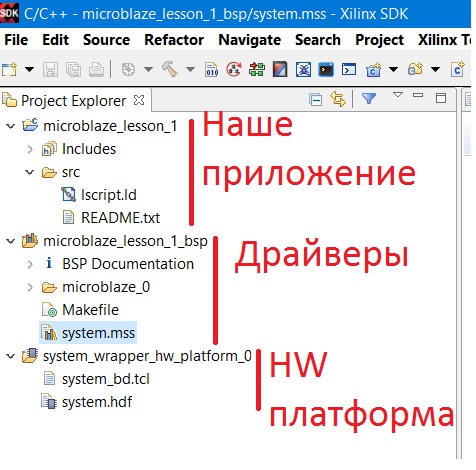

После нажатия на кнопку Finish в проект добавляется несколько файлов и папок (рис. 60).

Рисунок 60. После создания проекта добавляются приложение и драйверы.

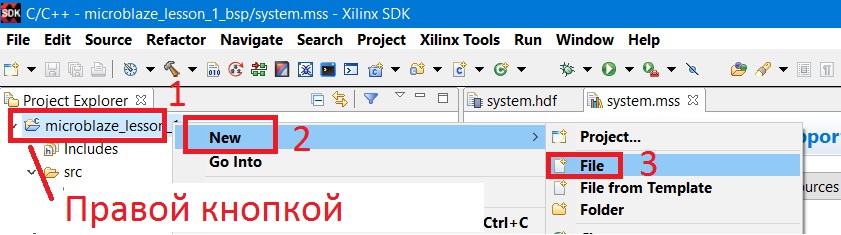

В нашем приложении ещё нет файла с исполняемой программой. Нам нужно создать его и добавить в проект. Поскольку качестве языка программирования был выбран C, то нужно добавить файл с расширением «.с». Для добавления нового файла в проект нажмите на значку нашего приложения правой кнопкой и выберите New – File (рис. 61).

Рисунок 61. Добавление нового файла в приложение

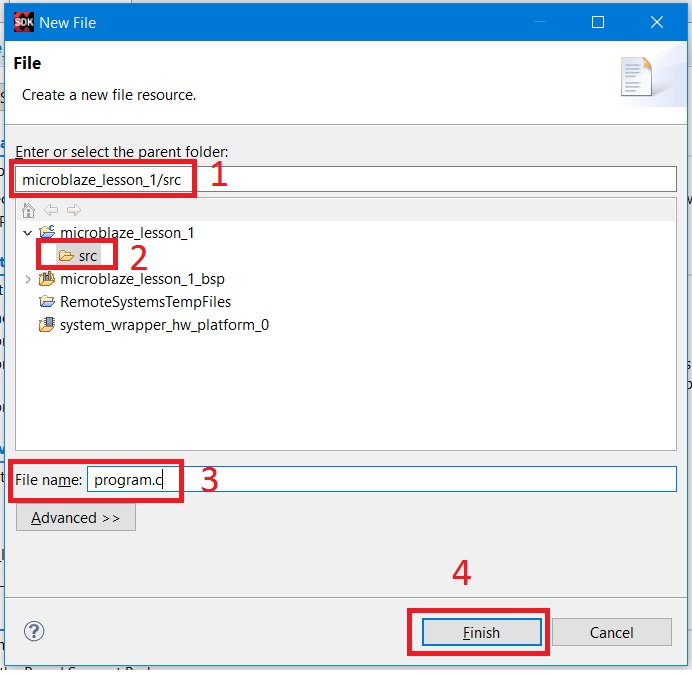

Теперь нужно указать параметры создаваемого файла (рис. 62). Путь к папке, в которой он будет создан, можно указать в строке 1, или же в дереве папок выбрать папку, в которой он будет создан.

Рисунок 62. Создание и добавление нового файла в проект.

На рис. 62:

1. Путь к файлу относительно каталога приложения.

2. Путь к файлу в дереве директорий.

3. Указываем название файла (program.c).

4. Нажмите Finish.

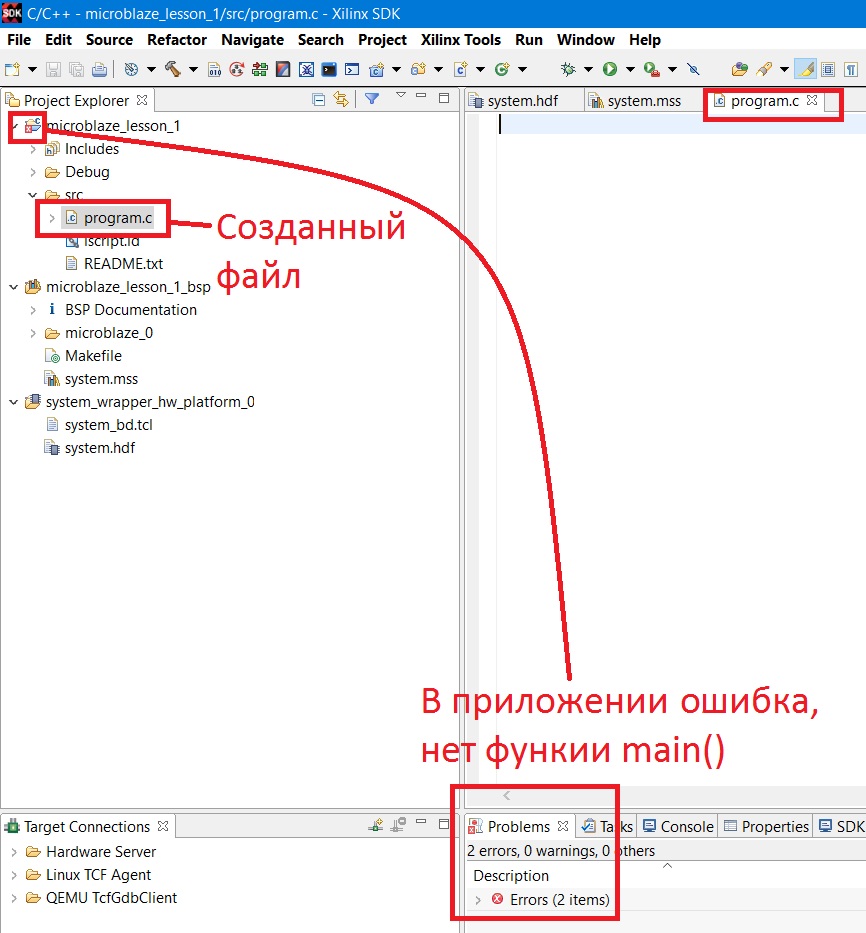

Созданный файл появится в папке src (рис. 63). Чтобы просмотреть его содержимое, дважды кликните по нему. После создания файла появилась ошибка, о чем говорит красный крестик в папке приложения. Дело в том, что файл – пустой, и в приложении нет функции main(). Нам необходимо написать программу в наш файл.

Рисунок 63. Ошибка из-за отсутствия функции main()

Откройте файл program.c и заполните его следующим кодом:

|

#include "xparameters.h" //Библиотека с параметрами IP-блоков XGpio gpio; //Создаем "программную" модель GPIO int main(){ u32 i = 0; //используем для задержки XGpio_Initialize(&gpio, XPAR_GPIO_0_DEVICE_ID);//Находим и инициализируем GPIO xil_printf("Hello, world!!!\n\r");//Автоматически цепляется Uartlite и выводит сообщение while(1){ //Бесконечный цикл мигания |

|---|

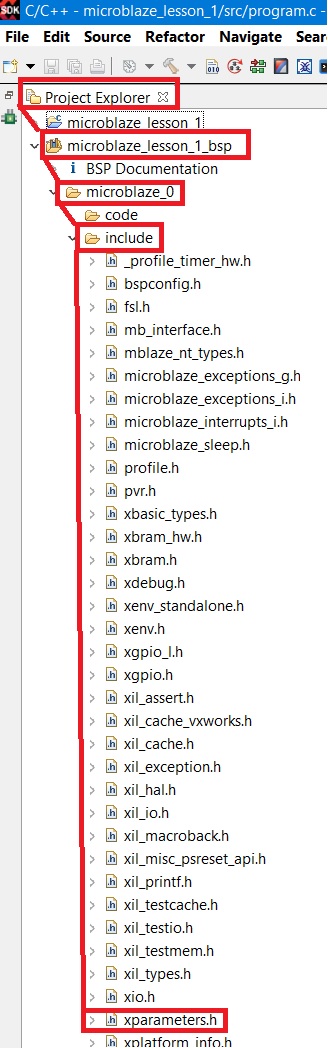

Файл xparameters.h является одним из наиболее важных файлов, который содержит адреса и номера устройств на шине нашей процессорной системы. Именно в нём определён номер (ID) нашего GPIO - XPAR_GPIO_0_DEVICE_ID. Если бы GPIO модулей было бы несколько, то для каждого из них было бы отдельное описание параметров адреса, ID и т.д. Файл xparameters.h можно найти (рис. 64) в Project Explorer – название_приложения_bsp – процессор – include.

Рисунок 64. Расположение файла xparameters.h

Мы создали программу, теперь можем её попробовать запустить. Мы не будем отлаживаться в пошаговом режиме, а сразу посмотрим результат. Но для начала нам необходимо подключить плату к компьютеру, что бы он определил какой COM порт будет задействован для UARTa.

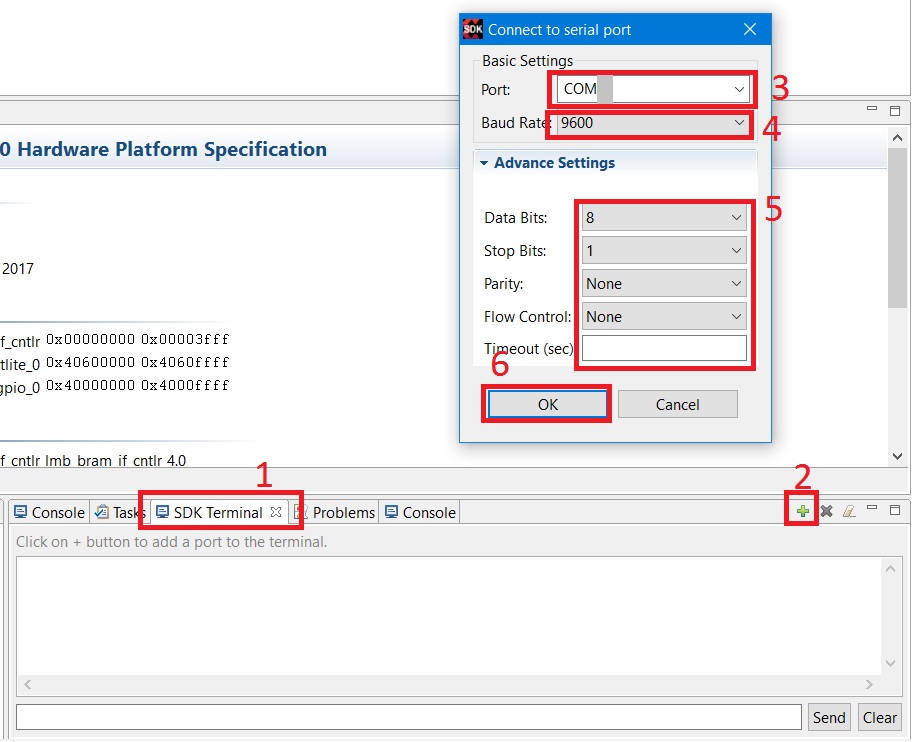

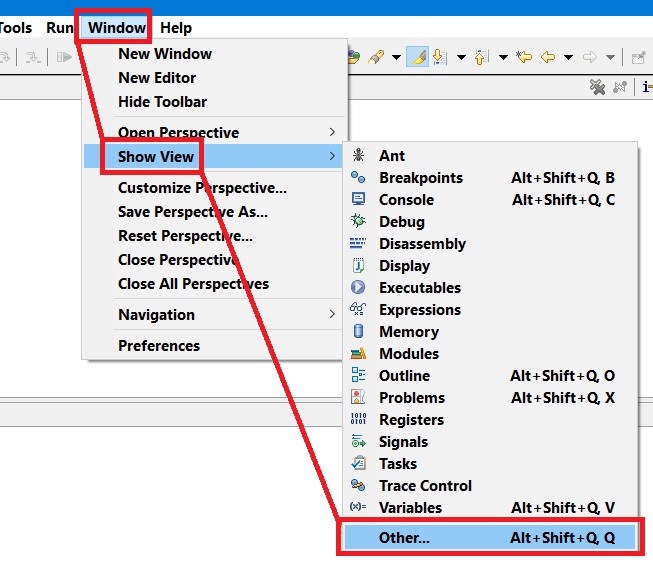

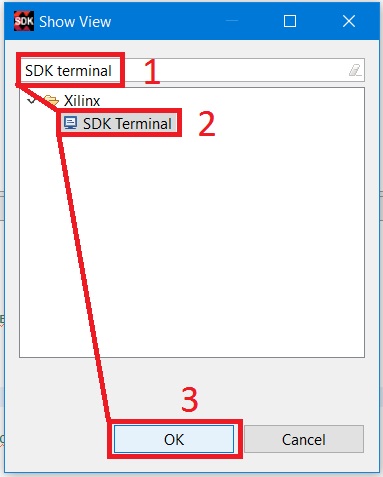

Для просмотра сообщений от UART мы будем использовать SDK terminal. Чтобы открыть SDK terminal, необходимо найти его в каталоге доступных окон. Для этого выберите Window – Show View – Others…, затем наберите в строке поиска SDK terminal, выберите его и нажмите OK (рис. 65).

Рисунок 65. Открытие окна SDK terminal

После этого должно появиться окно SDK terminal, которое мы будем использовать, чтобы «ловить» сообщения, посылаемые нашим Uartlite модулем. Теперь давайте настроим SDK terminal (рис. 66). Выберите окно SDK terminal, нажмите кнопку подключения к последовательном порту (зелёный крестик) и установите значения в соответствии с рис. 66, затем нажмите OK.

Рисунок 66. Настройка терминала SDK

Настройка терминала выполнена. По завершении настройки терминала, в нём может появиться «мусор». Если он Вам мешает нажмите кнопку очистить  , которая находится рядом с кнопкой подключения к порту (зелёный крестик 2 на рис. 66).

, которая находится рядом с кнопкой подключения к порту (зелёный крестик 2 на рис. 66).

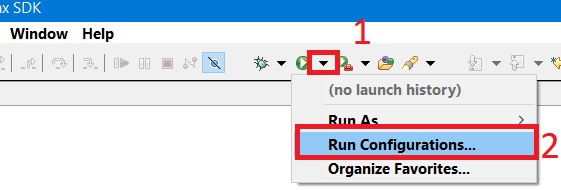

Теперь необходимо настроить запуск нашей программы: прошить FPGA и загрузить приложение в процессор. Всё это делается в одном окне, но в разных вкладках. Для настройки запуска (рис. 67) нажмите на треугольник рядом с кнопкой Run.

Рисунок 67. Вызов настроек запуска

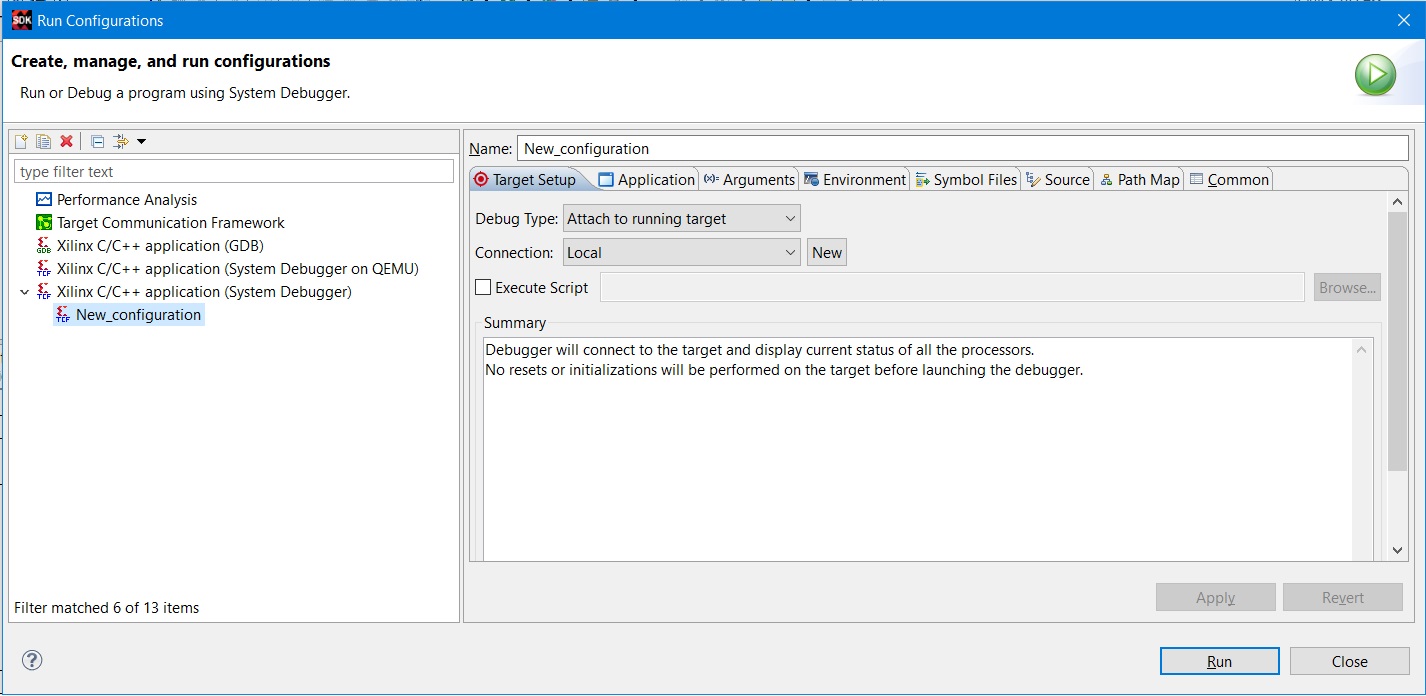

Окно на рис. 68 предназначено для выбора отладчика или инструмента запуска настройки запуска процессорной системы. Дважды кликните на System Debugger.

Рисунок 68. Окно выбора инструмента запуска

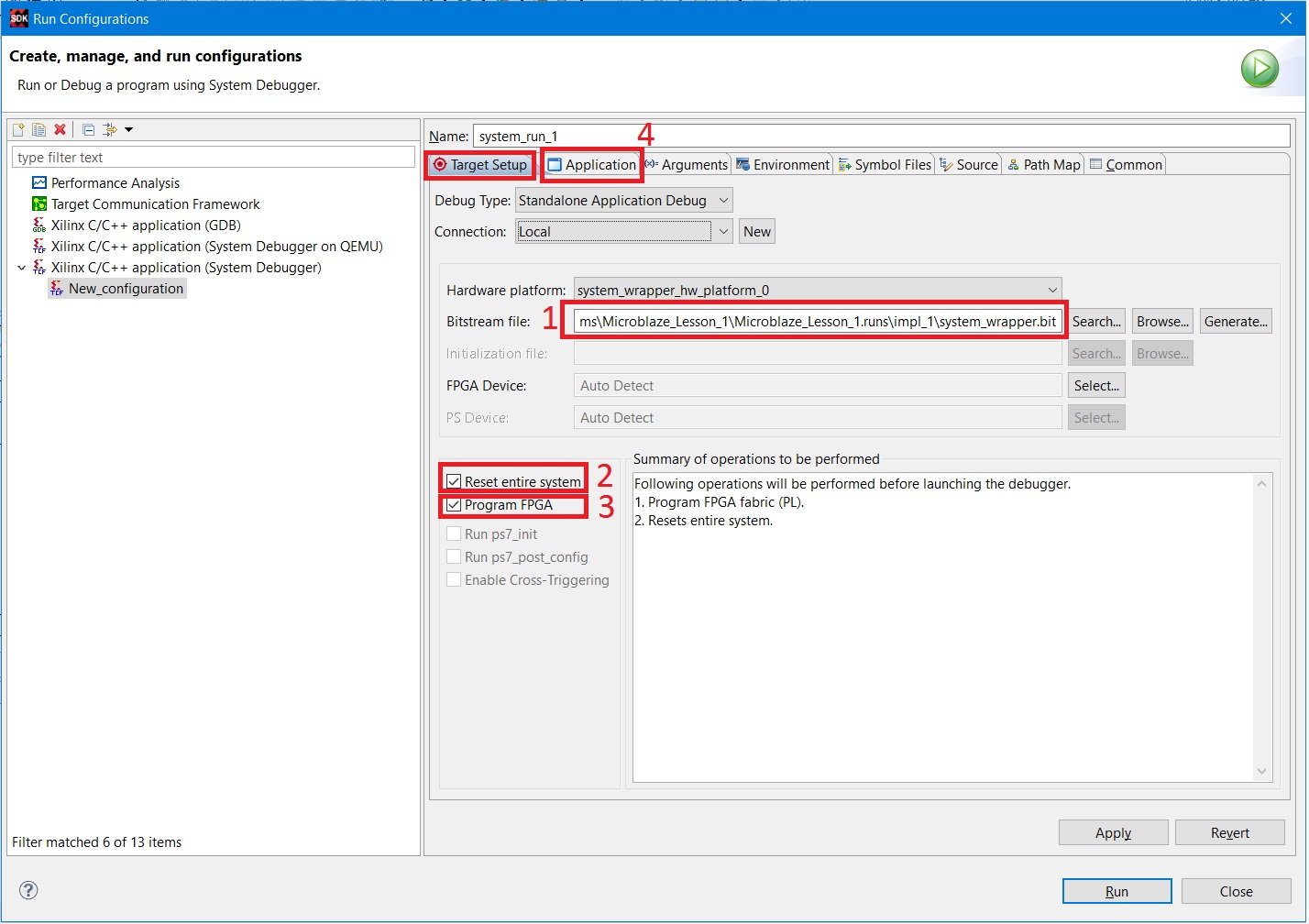

После этого окно должно приобрести вид, соответствующий рис. 69. Теперь можем приступить к настройке запуска.

Рисунок 69. Исходное окно настроек запуска

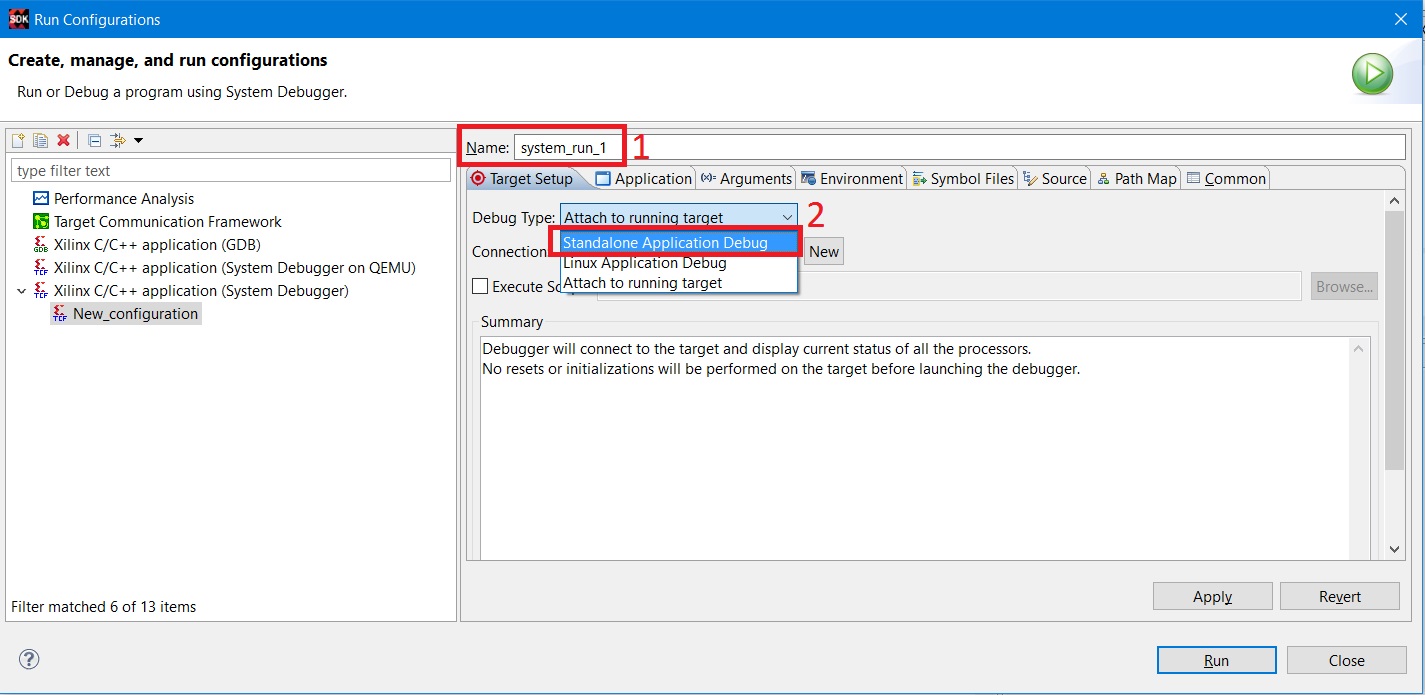

Измените название наших настроек на system_run_1, затем выберите Debug Type: Standalone Application Debug (рис. 70), после чего окно должно измениться.

Рисунок 70.Переименование настроек и выбор типа отладки

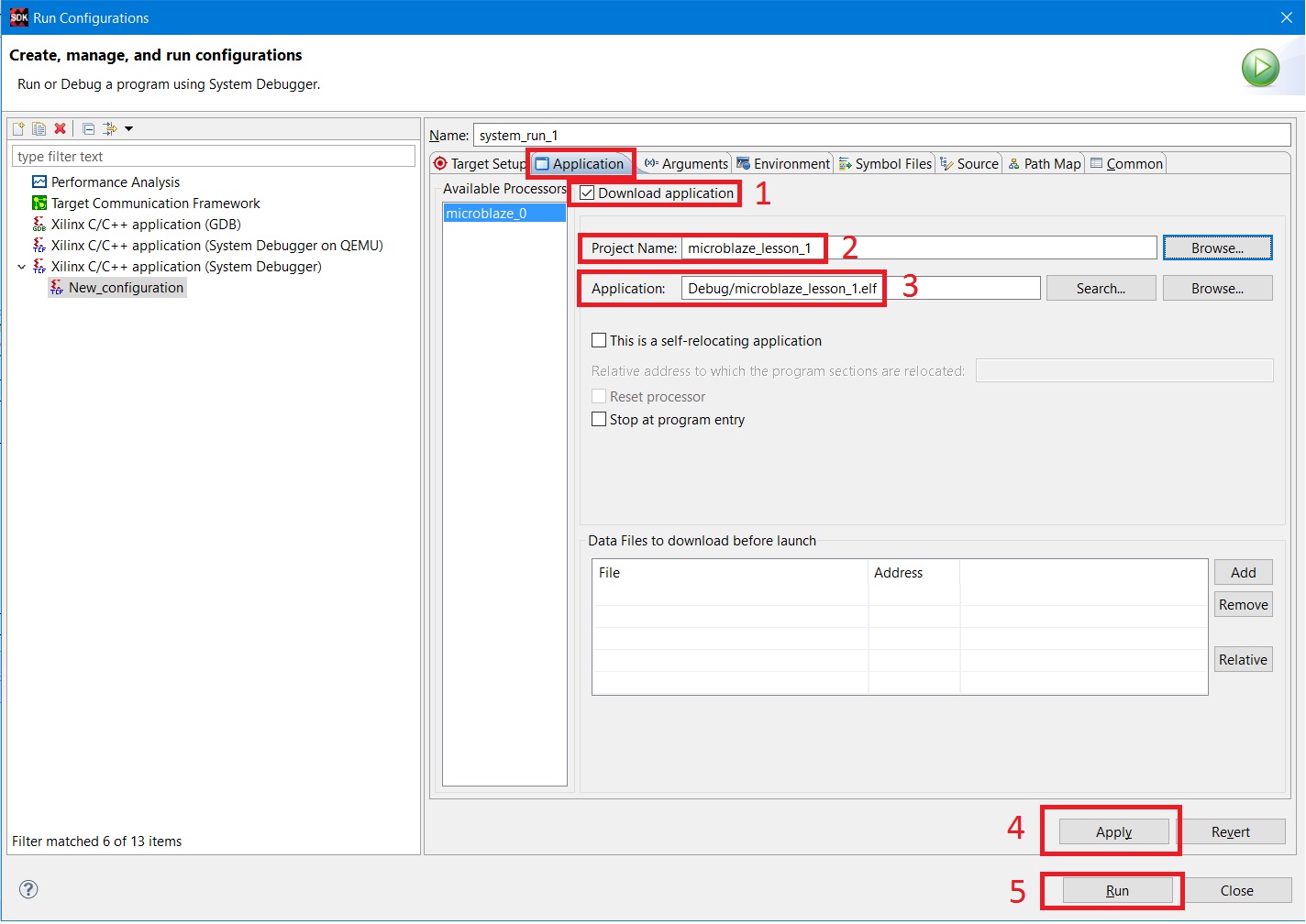

После изменения, заполните содержимое в соответствии с рис. 71.

Рисунок 71. Настройка HW параметров запуска

На рис. 71 обозначены:

1 Путь к бит файлу. Должен быть указан полный путь. Находится внутри папки с проектом (название_проекта – нзвание_проекта.runs – impl_1 – .bit)

2 Сброс системы после загрузки

3 Запрограммировать FPGA

4 Перейдите во вкладку Application

Рисунок 72. Настройка параметров запуска приложения

На рис. 72:

1 Загрузить приложение после загрузки FPGA

2 Название приложения, которое нужно загрузить

3 Путь к исполняемому .elf файлу приложения

4 Кнопка применить настройки

5 Запуск приложения

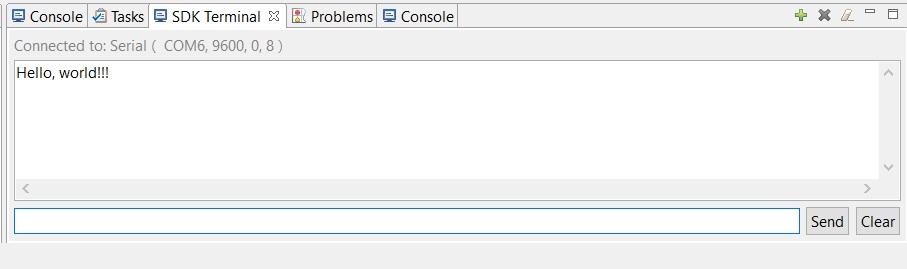

После нажатия кнопки Run произойдёт загрузка FPGA и запуск приложения, в результате чего светодиод LD4 на плате Arty Board должен начать мигать, а в SDK terminal должно появиться сообщение «Hello, world!», рис. 73.

Рисунок 73. Hello, world! В SDK terminal

На этом сборка и запуск процессорной системы, построенной на базе MicroBlaze, закончена.

Не смотря на то, что материал занимает более 60 страниц, для небольших проектов сборка процессорной системы на базе MicroBlaze занимает не многим больше 10 минут. Во многом этот процесс автоматизирован, что помогает избежать пользовательских ошибок. Ниже, в библиографическом списке, приведена некоторая подборка документов, которые могут послужить в качестве дополнительного материала для более глубокого понимания, как процесса разработки, так и функциональности используемых IP-блоков, а также приведены ссылки на доступные по данной тематике тренинги в сертифицированном тренинг центре компании Xilinx.

Если кто-то захочет попрактиковаться, то вот Вам домашнее задание:

1. На Arty Board установлены четыре зелёных светодиода. Сделайте из них бегущие огни или бегущую тень или счётчик. Тоже можно сделать и с трёхцветными светодиодами.

2. Настройте GPIO таким образом, что бы можно было считывать состояния кнопок, установленных на плате, и отображать их состояние в SDK terminal.

3. Сделайте запуск бегущих огней по кнопке – любой на Ваш выбор.

1. UG984. MicroBlaze Processor Reference Guide. Xilinx Inc.

2. MicroBlaze на сайте Xilinx

3. Vivado на сайте Xilinx

4. DS180. 7 Series FPGAs Data Sheet: Overview. Xilinx Inc.

5. Описание Arty Board на сайте Digilent

6. Сайт компании Регион-Вирта

7. UG995. Designing IP Subsystems Using IP Integrator. Xilinx Inc.

8. UG782. Software Development Kit (SDK) Help

9. PG144. AXI GPIO - LogiCORE IP Product Guide

10. PG142. AXI UART Lite - LogiCORE IP Product Guide

11. PG059. AXI Interconnect - LogiCORE IP Product Guide

12. UG1037. Vivado AXI Reference Guide

Список тренингов

по MicroBlaze в сертифицированном тренинг центре компании Xilinx:

1. Построение встраиваемых процессорных систем

2. Дополнительный курс по построению встраиваемых процессорных систем

3. Разработка ПО для встраиваемых процессорных систем

4. Доп. курс по разработке ПО для встраиваемых процессорных систем

5. Полный список курсов