Архив новостей из мира FPGA

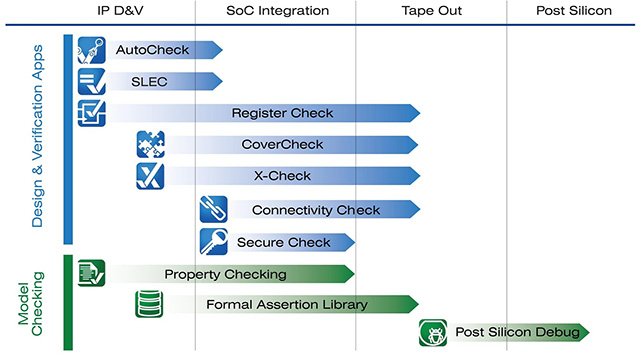

Практический маршрут для непрерывной интеграции: используйте EDA на максимум

Верификация изменений в коде RTL и коде тестового окружения перед релизом для остальной части команды - лучший способ избежать ошибок, которые приводят к массовым сбоям в работе всей команды. На этом вебинаре вы познакомитесь с примерами маршрутов проектирования, которые при использовании с системой непрерывной инте ... Читать дальше »

884

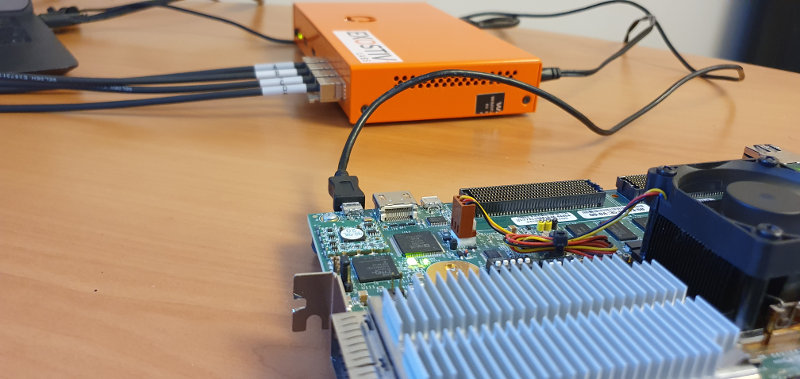

Захват огромного числа данных при отладке FPGA проектов

Если вы используете Xilinx Ultrascale(+), то вы знаете о сложностях, которые могут возникнуть при работе с этими ПЛИС, и о значительном времени и усилиях, необходимых для проверки функциональности разрабатываемых на них проектов. Даже при наличии всех доступных современных методов проверки дизайна и обширных лаборат ... Читать дальше »

1395

0

Интерактивный онлайн батл "ПЛИС vs Процессоры"

В эту субботу Томский политехнический университет проводит онлайн трансляцию! Это будет батл процессоров и программируемой логики. ... Читать дальше »

1194

0

Тестбенчи

Сотрудники Томского политехнического университета проводят бесплатный вебинар по теме "Тестбенчи". Познавательно, увлекательно ... возможно будет 23.10 в 14.00 по московскому времени. Мы только учимся выходить в онлайн, поэтому не судите слишком строго и приходите поо ... Читать дальше »

956

0

Вебинар от ALDEC: Краевые случаи как источник ошибок при проектировании ПЛИС

Краевые случаи в циклах - это, возможно, наихудшая и наиболее частая причина трудно обнаруживаемых ошибок во многих проектах ПЛИС. Чтобы объяснить это на простом примере - возьмем счетчик событий, где количество подсчитанных событий является критическим фактором, и вы считываете и обнуляете этот счетчик на регулярной основе. Типичный краевой случай - если вы считываете или обнуляете этот счетчик ровно в тот момент, когда приходит новое событие, которое надо посчитать. Тут возникает множество рисков и странного поведения счетчика. ... Читать дальше »

1025

0

История FPGA с Kapil Shankar

OSFPGA представляет содержательную серию вебинаров "История ПЛИС", на которых будет рассмотрена и обсуждена эволюция технологий ПЛИС, компаний и рынков, а также то, как она информирует и открывает возможности для инноваций и бизнеса в развивающихся сегментах рынка. ... Читать дальше »

1105

0

UVM для FPGA (часть 4): стандарт IEEE 1800.2 - изменения UVM

Докладчик: Srinivasan Venkataramanan, Entrepreneur and Head of VerifWorks Описание: Начиная с первого релиза Accellera 1.0a, UVM эволюционировала в заметные версии UVM 1.1 и UVM 1.2. Как и многие другие популярные стандарты, возникло желание стандартизации UVM, что и произошло в IEEE в 2017 году. Что интересно, UVM - это первая из стандартизованных методологий верификации, и ее текущая версия - IEEE 1800.2-2020. ... Читать дальше »

1246

0

Портирование свёрточных нейронных сетей на платформу Xilinx Zynq Ultrascale Plus и ускорение их работы

Компания Макро Групп приглашает на вебинар по нейронным сетям разработчиков решений на платформах Xilinx и специалистов по искусственному интеллекту и нейросетям. На вебинаре вы узнаете, какие шаги необходимо выполнить для запуска собственной сверточной нейросети на платформе Xilinx Zynq Ultrascale+, и увидите её ра ... Читать дальше »

1230

0

Двухдневный семинар по Xilinx Versal от Doulos 15-16.09 или 29-30.09 без оплаты.

15-16 и 29-30 сентября в 18:00 по Москве будет проводиться семинар по платформе Xilinx Versal. Семинар проводится одной из крупнейших европейских онлайн-школ Doulos. Оплата не требуется , тогда как обычная цена этого двухдневного семинара - 990 долларов США. Спонсирует всё Xilinx. Два дня занятий по 4 часа.

... Читать дальше »

919

0

Что нового в OSVVM?

В течение 2020 года OSVVM имел 6 обновлений. В 2021 тенденция сохранилась и произошел релиз обновлений в феврале, июне и июле. На этом вебинаре мы осудим, что именно изменилось в OSVVM в 2021 году.

Вебинар состоится ... Читать дальше »

1205

0 |

0