Архив новостей из мира FPGA

Вебинар: Kria – новый подход к проектированию встраиваемых систем на ПЛИС Xilinx

Приглашаем вас на русскоязычный вебинар, посвящённый новому классу изделий, выпускаемых компанией Xilinx – системы-на-модуле Kria. Kria – это новое законченное решение промышленного класса исполнения, готовое к применению в серийных изделиях, выполненное на базе Zynq UltraScale+. На вебинаре мы определим место Kria в линейке продуктов Xilinx, локализуем области применения Kria, а также рассмотрим: ... Читать дальше »

1005

Очередной вебинар от Doulos по основам UVM

1077

0

Вебинар: Внедрение ИИ в EDGE устройства на FPGA Xilinx

Приглашаем вас на вебинар по внедрению искусственного интеллекта и аналитики в Edge устройства на базе систем-на-кристалле и ПЛИС. Новейшее решение iWave Edge AI, Corazon-AI, построенное на XILINX Zynq UltraScale+ MPSoC, отлично подходит для удовлетворения растущих требований к интеллекту в краевых устройств ... Читать дальше »

1289

0

Проектирование RTL на Haskell/Clash

Clash (https://clash-lang.org/) - это методология проектирования цифровых схем на основе функционального языка программирования Haskell (https://haskell.org). Модель приложения и ее имплементация в виде схемы могут быть описаны на Clash. Поскольку реализация может быть получена из модели , оставаясь в рамках од ... Читать дальше »

1499

0

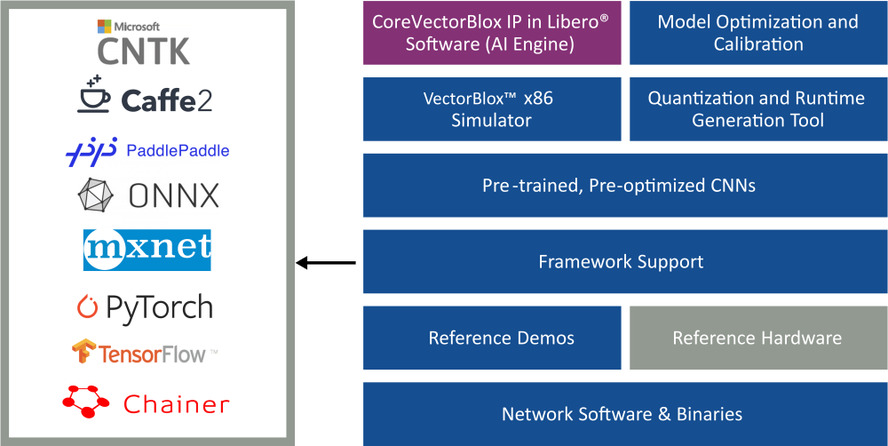

Выложены материалы вебинара по развертыванию сверточных нейронных сетей на основе ПЛИС Microchip

На предыдущей неделе прошёл вебинар, посвященный обзору малопотребляющих ПЛИС Microchip и развертыванию на них сверточных нейронных сетей с помощью фреймворка VectorBlox. Запись можете посмотреть на нашем Y ... Читать дальше »

1432

0

SoM-модули Trenz Electronic для проектирования и производства устройств на ПЛИС Xilinx. Вебинар

Проектирование современной электроники – это довольно сложный и затратный процесс. Написание ПО, разводка и изготовление печатных плат, отладка и тестирование – эти и другие этапы работы над конечным устройством могут занимать много времени и финансовых ресурсов даже при грамотной организации рабочего пр ... Читать дальше »

1388

0

Вебинар о построении сверточных нейронных сетей на основе ПЛИС Microchip

20 апреля состоится вебинар, посвященный обзору малопотребляющих ПЛИС Microchip и развертыванию на них сверточных нейронных сетей с помощью фреймворка VectorBlox.

1081

0

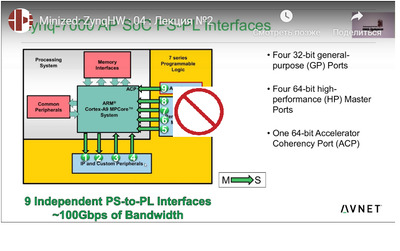

Захват огромного потока данных в FPGA

Если вы используете ПЛИС Xilinx Ultrascale (+) в своих проектах, то вы наверняка знаете насколько такие проекты могут быть сложными, требующими больших временных затрат и усилий. Даже при наличии всех современных методов верификации проектов и лабораторных испытаний считается, что более 80% ПЛИС в изделия ... Читать дальше »

1487

0

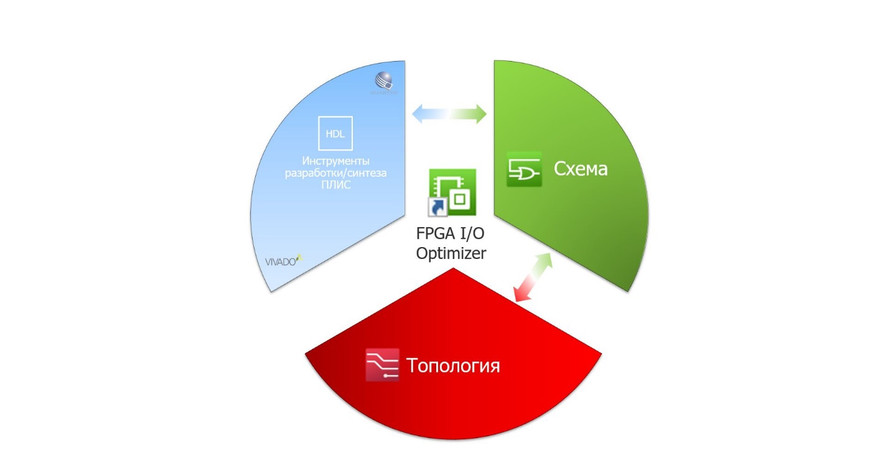

Ускорение процесса проектирования печатных плат с использованием ПЛИС

Мощность, гибкость и непосредственная доступность ПЛИС привела к тому, что они получили широкое распространение при разработке проектов печатных плат. Очевидно, что благодаря более быстрому выходу на рынок за счет достоинств и высокой производительности, ПЛИС стали перспективной альтернативой по сравнению с более ресурсоемкими IC/ASIC решениями. ... Читать дальше »

1614

0

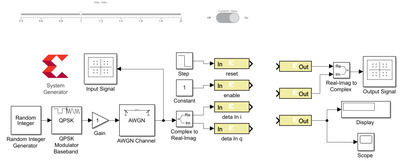

Увеличение продуктивности верификации RTL кода в Matlab и Simulink

Проверка RTL кода остается серьезной проблемой в FPGA и ASIC проектах. На этом вебинаре мы увидим, как инженеры с различными навыками могут использовать инструменты MATLAB / Simulink для повышения эффективности и сокращения времени верификации. ... Читать дальше »

1794

0 |

1