Проектирование RTL на Haskell/Clash

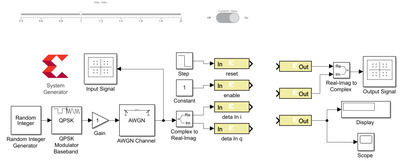

Clash (https://clash-lang.org/) - это методология проектирования цифровых схем на основе функционального языка программирования Haskell (https://haskell.org). Модель приложения и ее имплементация в виде схемы могут быть описаны на Clash. Поскольку реализация может быть получена из модели , оставаясь в рамках одного и того же языка на каждом этапе, Clash предлагает уникальную среду для проектирования, основанного на модели. Кроме того, Clash предлагает компилятор, который переводит полученные высокоуровневые описания схем в структурный (системный)Verilog и/или VHDL для конфигурации FPGA или для реализации ASIC.

Однако Clash не является ни HLS, ни так называемым поведенческим синтезом для Haskell: Clash переводит описания схем в их максимально параллельную реализацию и вводит только триггеры и другие типы последовательных элементов там, где их фактически написал разработчик. Таким образом, с Clash разработчик всегда полностью контролирует ситуацию.

Вебинар состоится

- 20 мая в 8:00, 16:00, 22:00 по Мск

- 26 мая в 8:00, 16:00, 22:00 по Мск

- Ссылка на регистрацию