Подключение подсистемы памяти к MicroBlaze (MIG 7 Series)

Аннотация

В статье описано подключение к процессорной системе подсистемы оперативной памяти с использованием MIG 7 Series в Vivado 2018.3. Будут рассмотрены основные моменты настройки IP ядра и его подключение к процессору MicroBlaze.

Введение

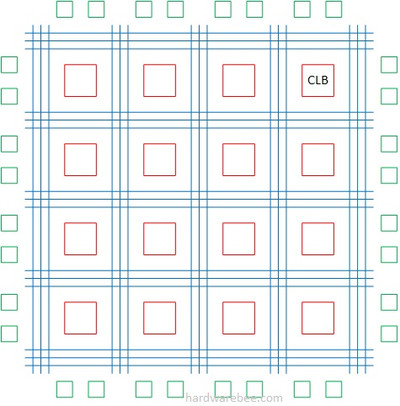

Память DDR очень часто является неотъемлемой частью многих проектов и охватывает широкий круг задач, потому включение в проект контроллеров памяти просто необходимо. MIG 7 Series поддерживает всю седьмую серию FPGA Xilinx, а также SoC Zynq-7000, и позволяет подключать DDR3 и DDR2 SDRAM, QDR II + SRAM, RLDRAM II / RLDRAM 3 и LPDDR2 SDRAM. [1]. Однако при сборке процессорной подсистемы с Microblaze возможно настроить контроллер для работы только с DDR3 и DDR2 SDRAM. Вероятнее всего, это связано с наличием AXI4 интерфейса только для этих конфигураций памяти и отсутствием такового у других. Однако эта тема выходит за рамки данной статьи, но, возможно, будет затронута в будущем.

Целью статьи является описание основных настроек MIG 7 для памяти DDR3 и DDR2 SDRAM и пояснение этапов подключения подсистемы к ядру MicroBlaze.

Настройка

Перед началом настройки необходимо создать проект в Vivado. У меня на текущий момент установлена версия Vivado 2018.3, и создавать проект я буду под Spartan с 50К ячеек, который стоит на плате ARTY S7 от Digilent [2]. Так как это уже было описано ранее [3], повторяться не будем и сразу перейдем к моменту добавления IP Core в блок дизайне.

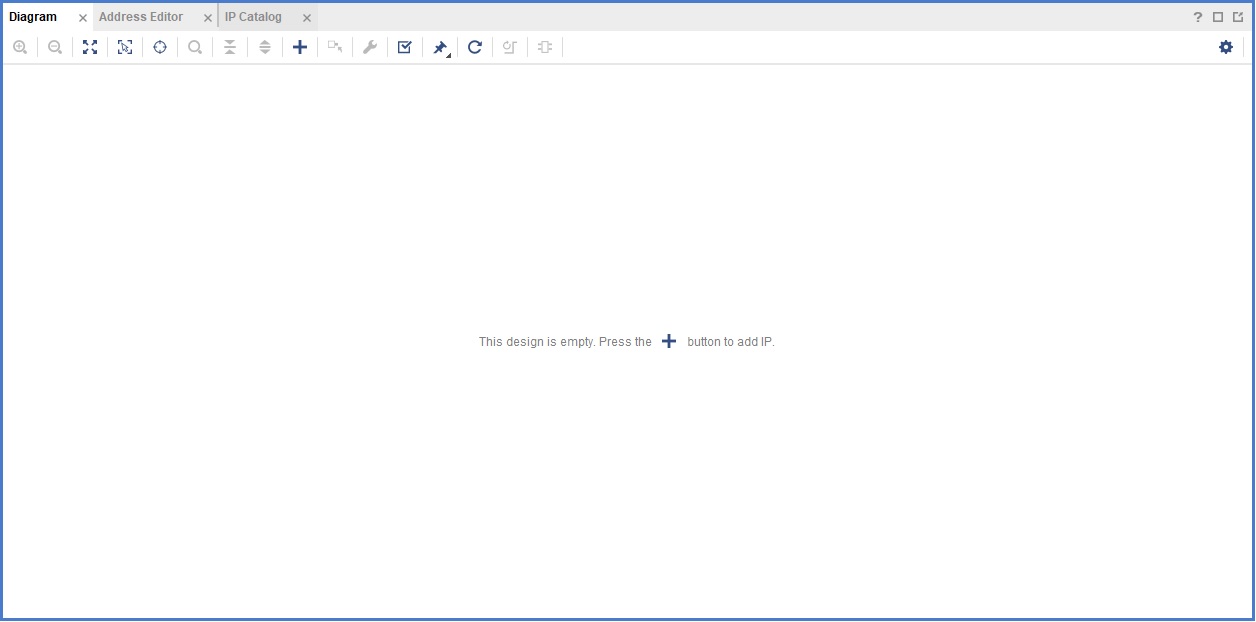

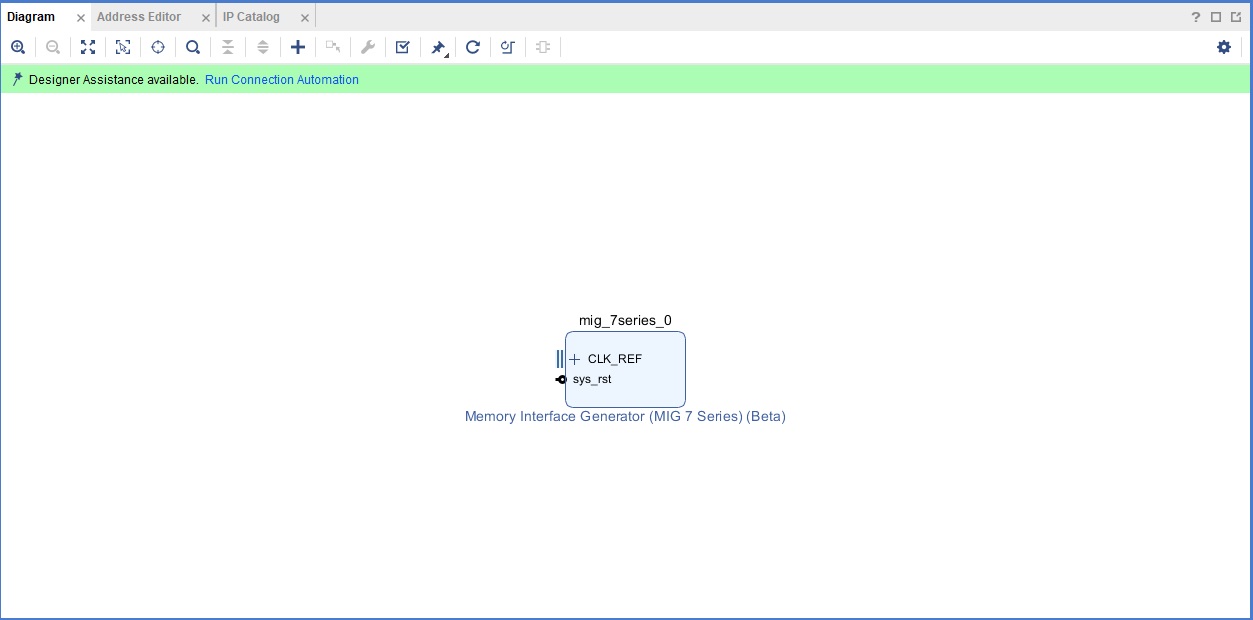

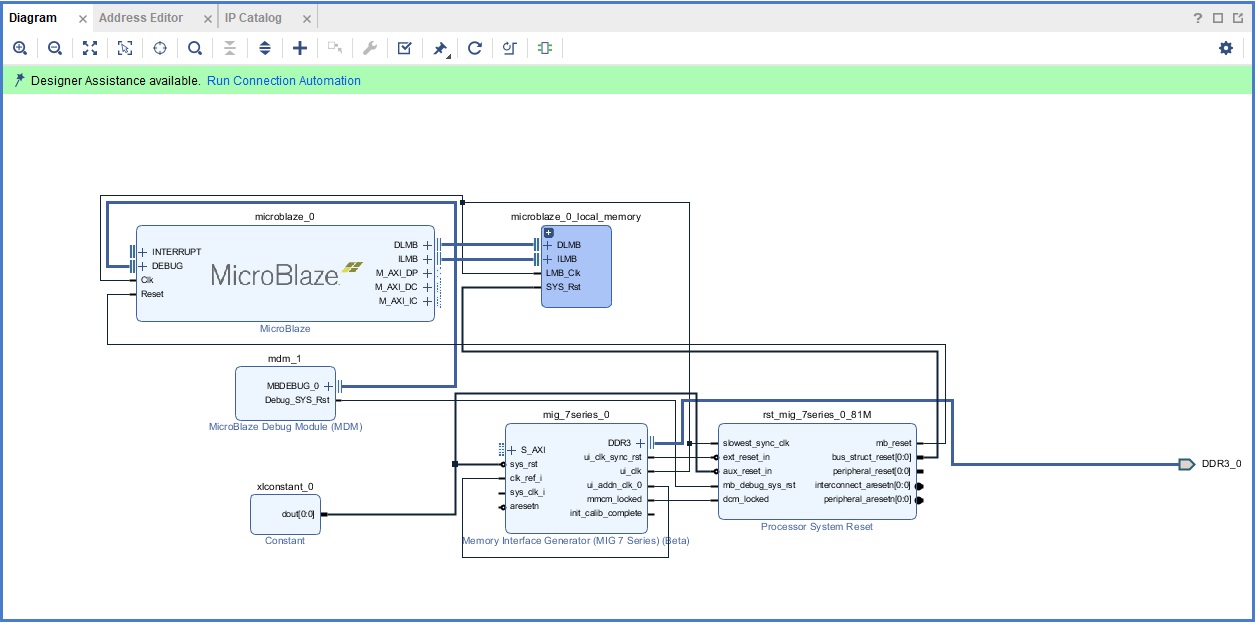

После создания проекта и блок дизайна мы видим следующее окно (рисунок 1):

Рисунок 1 – Окно Block Design

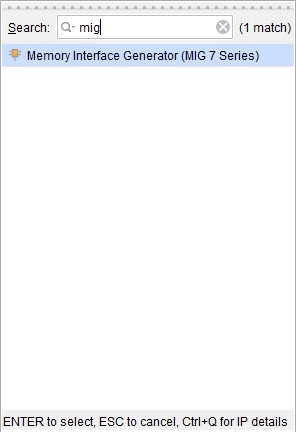

Теперь мы можем добавлять различные ядра, включая MIG 7, с него и начнем. Откроем каталог доступных ядер и введем MIG в строке поиска. Мы должны увидеть следующее окно (рисунок 2):

Рисунок 2 – Окно с доступными ядрами

Дважды кликаем по нему и теперь можем увидеть, как он добавился в наш проект (рисунок 3).

Рисунок 3 – Окно Block Design с добавленным MIG 7

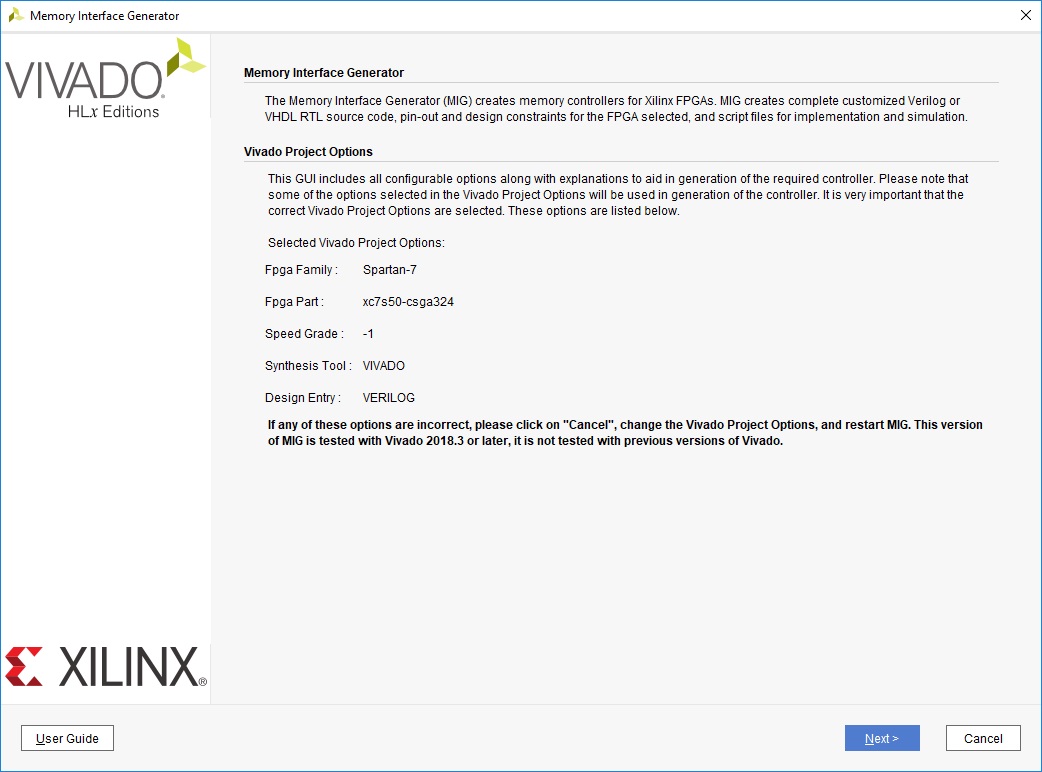

Дважды щелкнем мышкой по нему и вызовем окно настройки контроллера памяти (рисунок 4).

Рисунок 4 – Окно настройки MIG

Подробно каждый пункт настройки описан в UG586 [4]. Поэтому, если кто-то захочет найти дополнительную информацию, лучше всего начинать поиск именно оттуда. На этой вкладке мы можем увидеть немного вводной информации об этом ядре и настройках текущего проекта. Нам предлагают ознакомиться с ними и продолжить, если все корректно, либо закрыть это окно, исправить необходимое и снова сюда вернуться. Переходим на следующую вкладку (рисунок 5).

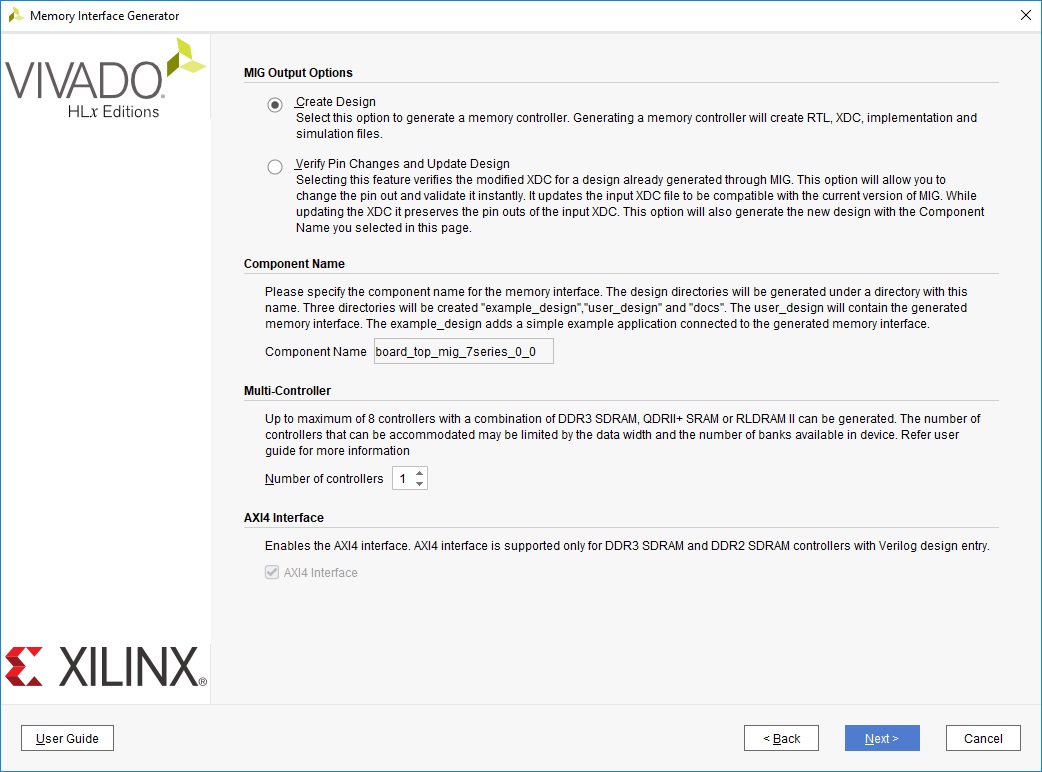

Рисунок 5 – Вкладка настройки общих параметров

Тут мы имеем возможность выбора создания нового или верификации дизайна предыдущими настройками. Для плат Digilent’a можно найти эти настройки на гитхабе [5] и скачать или склонировать себе на компьютер. Также можно выбрать количество контроллеров в системе. Последняя неактивная вкладка должна давать нам возможность выбора интерфейса с шиной AXI. Но активной она становится только при запуске MIG из IP каталога в отдельной вкладке. Тут мы можем увидеть, что только контроллеры памяти DDR3 и DDR2 могут поддерживать эту опцию, и только если выбран Verilog как основной язык. На этой вкладке мы ничего не будем менять и потому продолжим на вкладке Pin Compatible FPGA (рисунок 6).

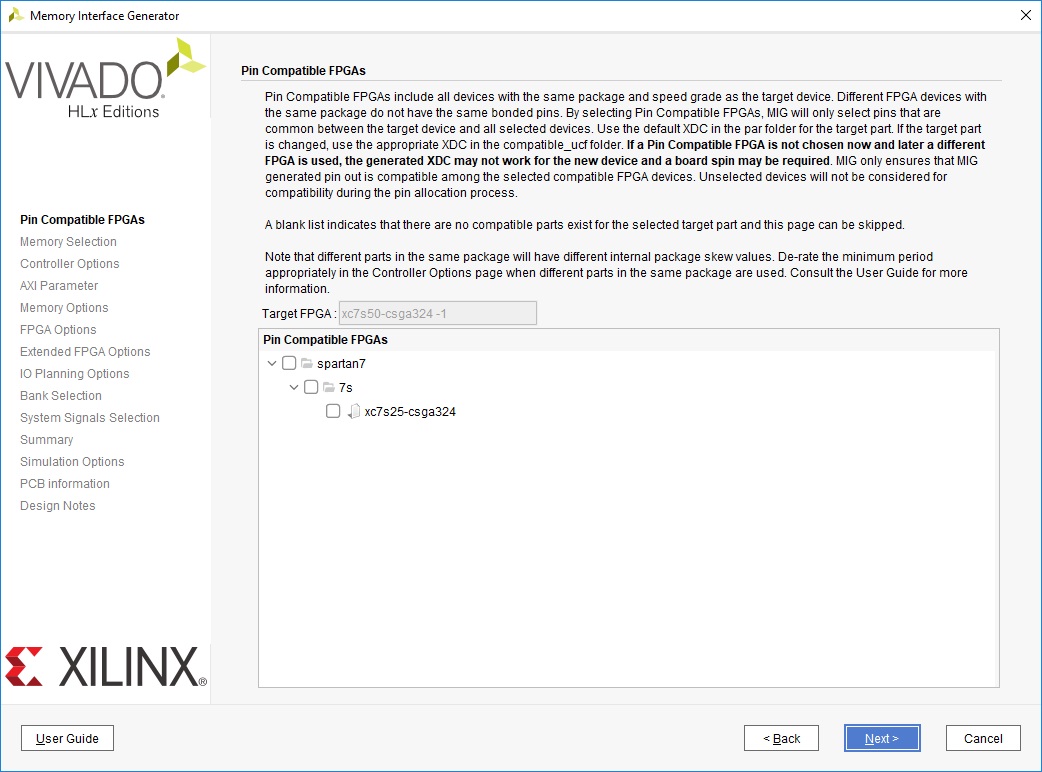

Рисунок 6 – Вкладка Pin Compatible FPGA

На текущей вкладке мы можем выбрать дополнительные FPGA, совместимые с нашей по корпусу и температуре. При выборе дополнительно совместимых FPGA, MIG будет резервировать только те выводы, которые являются общими для всех выбранных микросхем. Так как сейчас нам это не нужно, мы можем продолжить и перейти к вкладке Memory Selections (рисунок 7).

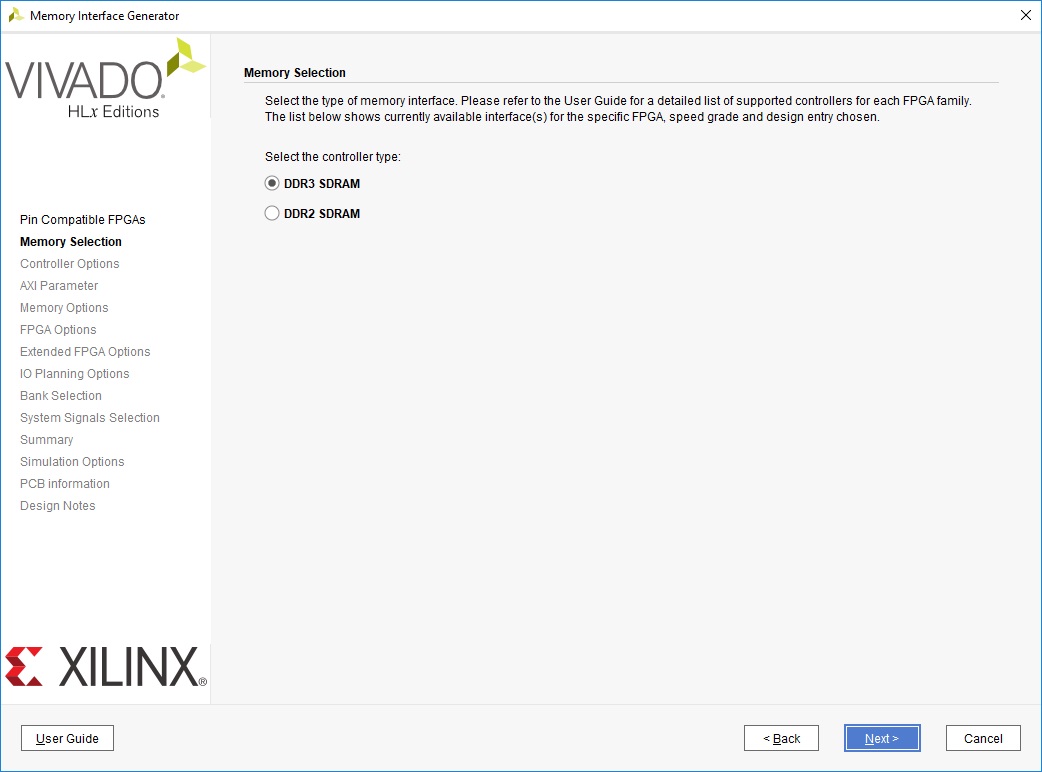

Рисунок 7 – Вкладка Memory Selection

Здесь мы выбираем необходимую нам память. На платах Digilent’a стоят микросхемы памяти DDR3, поэтому для моей платы ничего менять не нужно. Нажимаем «продолжить» и переходим к следующей вкладке (рисунок 8).

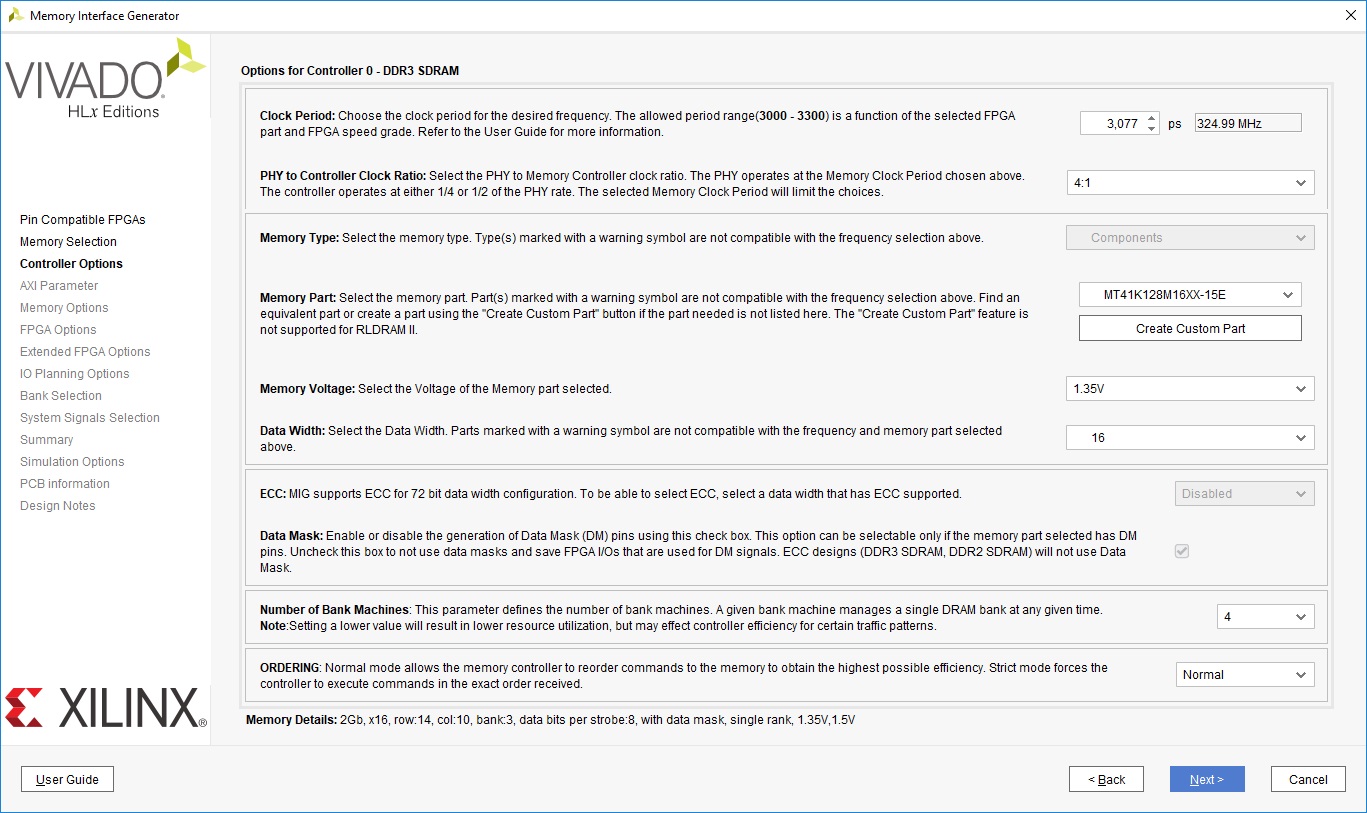

Рисунок 8 – Вкладка Controller Options

На этой вкладке мы выбираем частоту контроллера, частоту системного клока и настраиваем память. Мои настройки на этой странице совпадают с настройками Digilent’a, но на других платах они могут отличаться. Частота памяти настраивается в соответствии с вашей FPGAи ее Speed Grade’ом. Вторая строка настройки определяет отношение частоты работы памяти к частоте пользовательского клока. В нашем проекте этим клоком будет тактироваться MicroBlaze.

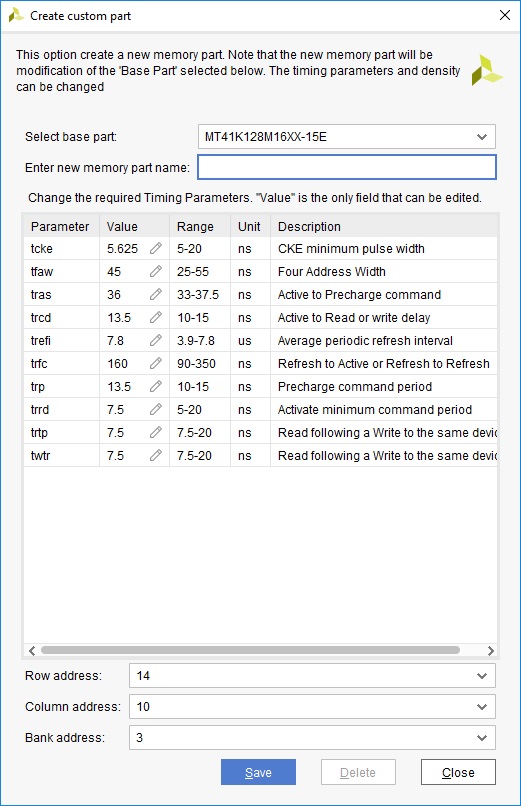

Следующий блок настраивает физические параметры используемой памяти. Временные параметры можно выбирать из некоторого количества предустановленных конфигураций, но даже если ее найти не получилось, можно создать свою конфигурацию на основе одной из имеющихся (рисунок 9).

Рисунок 9 – Настройка временных параметров

Все временные параметры можно найти в документации на вашу память. Напряжение питания и ширина шины данных также находятся в этой документации.

Number of Bank Machines оставим по умолчанию, а параметр Ordering сменим на Normal. Это должно повысить эффективность, так как дает контроллеру изменять приоритеты обращения к памяти автоматически, но принципиально никак не должно повлиять на будущий вид этого IP. Теперь можно перейти к следующей вкладке (рисунок 10).

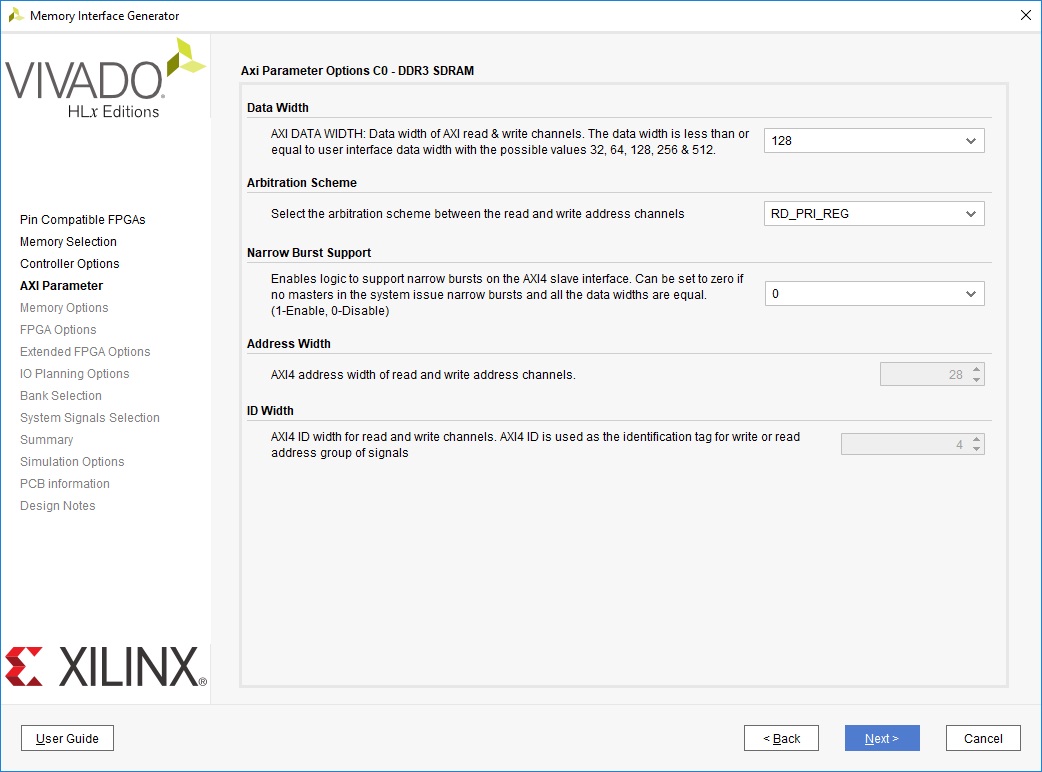

Рисунок 10 – Вкладка AXI Parameters

На данной вкладке требуется настроить внутреннюю шину, через которую наше ядро будет подключаться к Microblaze. Ширину шины данных можно выбрать из предложенных значений, но не меньше ширины подключаемого пользовательского интерфейса. Вторая вкладка определяет порядок приоритетов чтения и записи. Третья вкладка позволяет включить поддержку Narrow Burst. Она необходима, если ширина шин устройств не совпадает, однако, как указано в документе [4], XPS в состоянии сама рассчитать необходимость ее поддержки после анализа подключенных мастеров к шине. Оставим все настройки по умолчанию и перейдем к вкладке Memory Options (рисунок 11).

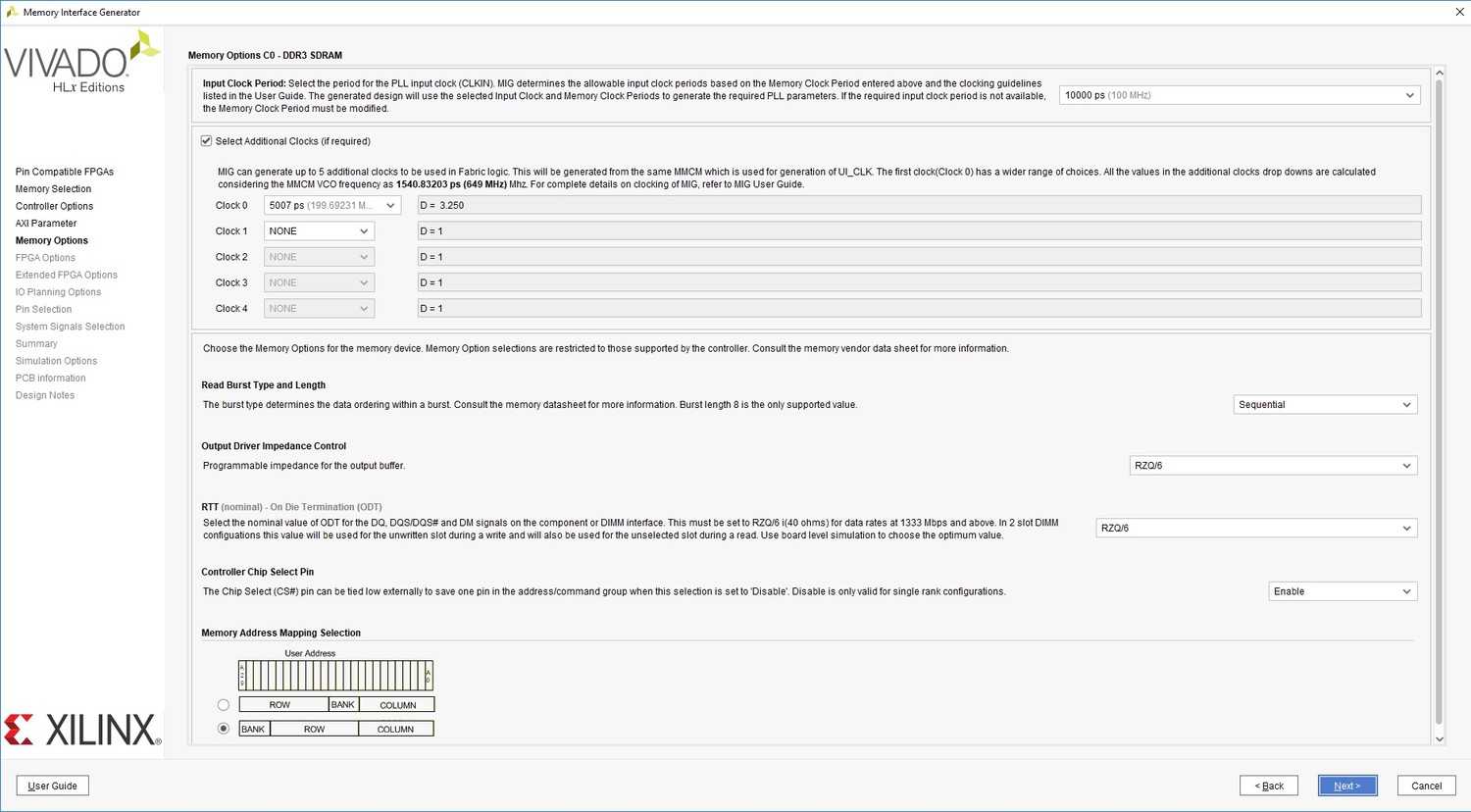

Рисунок 11 – Вкладка Memory Options

На этой вкладке мы настраиваем входные и выходные клоки, а также импеданс буферов и терминальных резисторов. На ARTY S7 в банке с DDR стоит генератор на 100 МГц, поэтому выбираем его как входной клок. Также дополнительно генерируем 200 МГц, они понадобятся нам в будущем для опорного клока. Помимо 200 МГц, можно вывести до пяти других частот, если такие понадобятся в нашем проекте. Если нужные частоты получить не удается, можно попытаться вернуться назад и изменить частоту памяти.

Burst Type and Length настраивает тип пакетных передач. Для DDR3 и DDR2 длина может быть только 8. Output Driver Impedance Control и ODT выставим в соответствии с настройками Digilent’a. При настройке другой платы выходной импеданс нужно искать в документации. Остальные настройки оставим по умолчанию и перейдем на вкладку FPGA Options (рисунок 12).

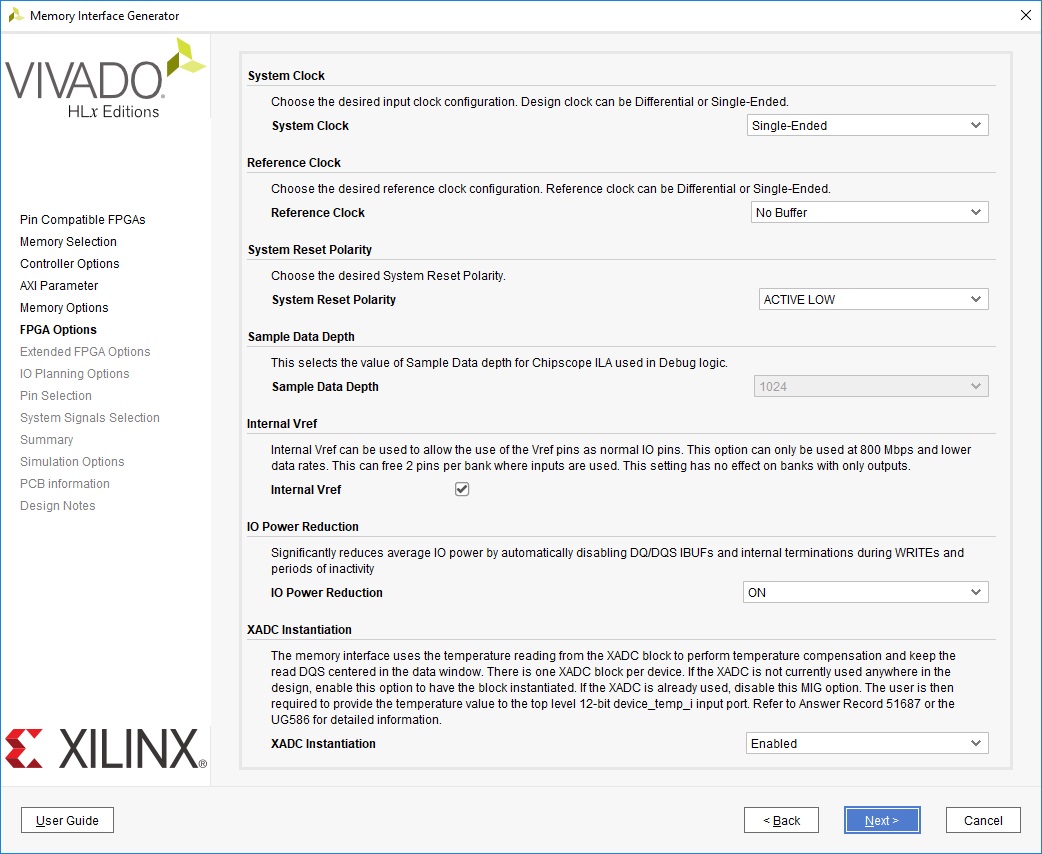

Рисунок 12 – Вкладка FPGA Options

Выбираем входную частоту как Single-Ended и опорную частоту как No Buffer. Опорную частоту можно тактировать и от входной частоты, если она входит в диапазон от 199 МГц до 201 МГц. Она нужна для тактирования модулей IDELAYCTRL и элементов IDELAY в банке ввода-вывода, подключаемом к памяти. Установим галочку напротив Internal Vref. Это позволит сэкономить выводы, отведенные под опору, и использовать их в проекте как Single-Ended. Однако это возможно только на скоростях передачи ниже 800 Mbps. Также оставим включение XADC в ядро, потому что использовать его в проекте больше не планируем. Пропустим вкладку Extended FPGA Options, потому что там ничего менять не будем, и перейдем на вкладку IO Planning Options (рисунок 13).

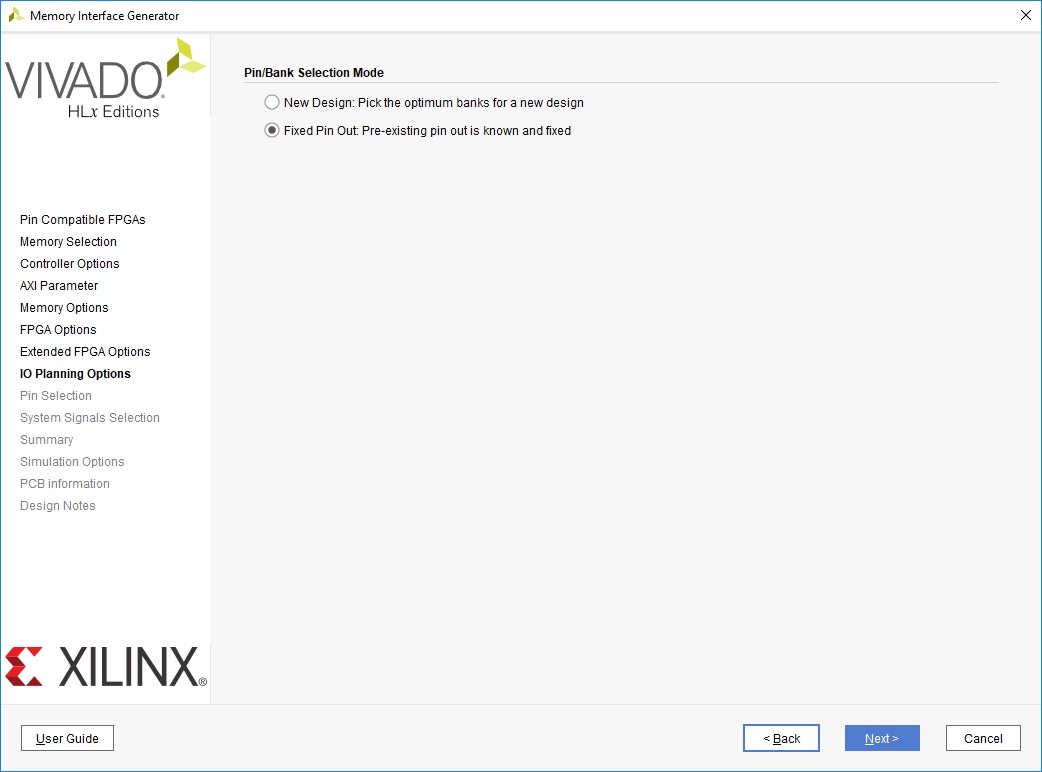

Рисунок 13 – Вкладка IO Planning Options

От выбора на этой вкладке зависит то, как будут назначены сигналы для памяти. Если ядро генерируется для нового проекта, то можно зарезервировать выводы в соответствии с группами байт. Мы же воспользуемся вторым вариантом, так как наши пины уже известны заранее. На следующей вкладке Pin Selection увидим следующую картинку (рисунок 14):

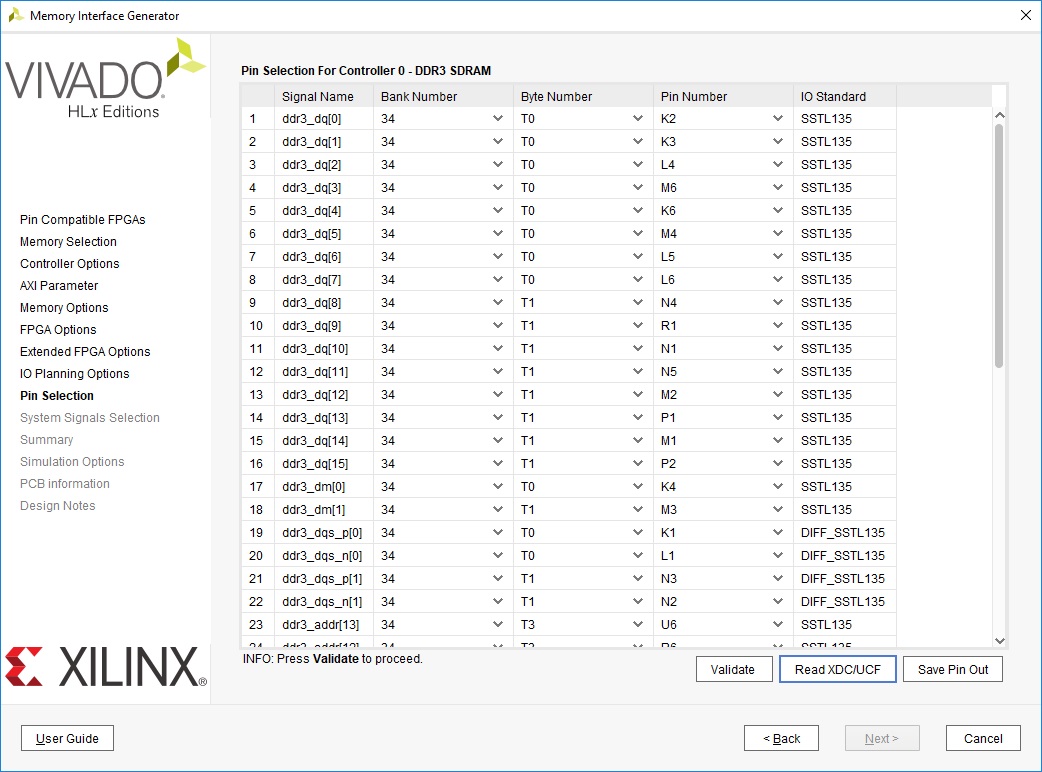

Рисунок 14 – Вкладка Pin Selection

Воспользуемся констрейнами от Digilent’a, нажав кнопку Read XDC/UCFи выбрав соответствующий файл из репозитория. Для каждого сигнала должны обновиться номера выводов и их стандарты. Нажимаем на кнопку Validate и, если все нормально, переходим к следующей вкладке (рисунок 15).

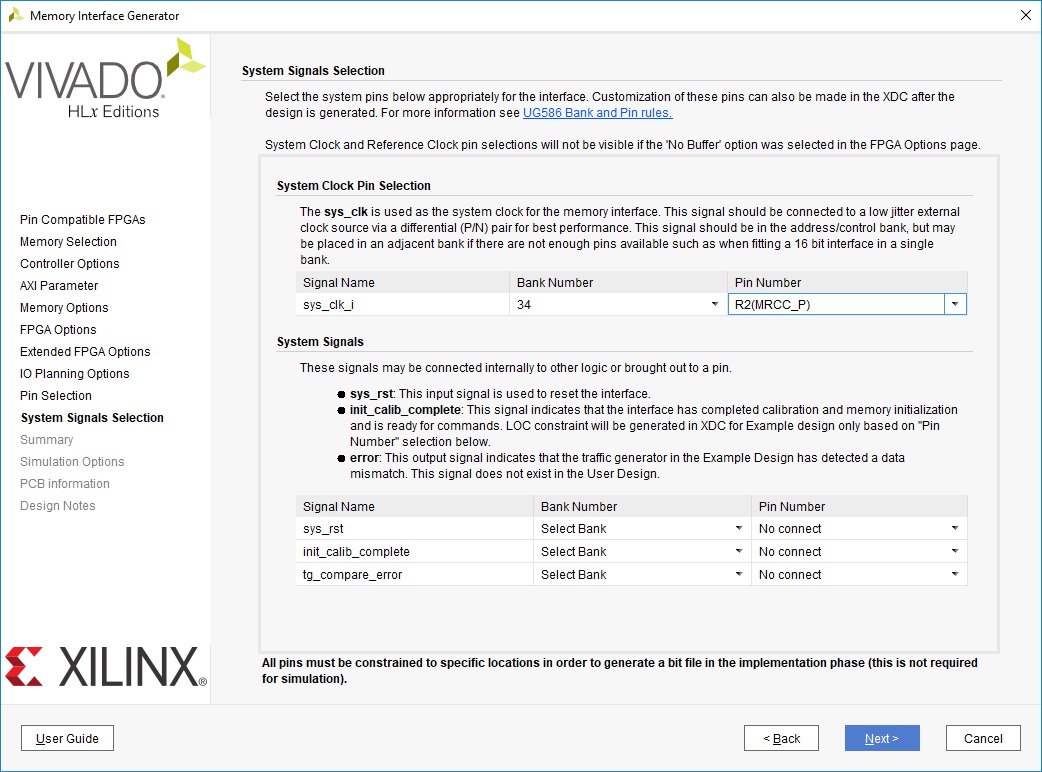

Рисунок 15 – Вкладка System Signals Selection

Выбираем выводы для задействованных сигналов. Так как внешним у нас является только системный клок, то назначаем ему один из предложенных выводов, предварительно сверившись со схемой отладочной платы. Генератор подключен на вывод R2, его и выбираем. Больше нас на этой вкладке ничего не интересует.

На оставшихся вкладках нет никаких настроек, потому с ними можно ознакомиться самому, принять лицензионное соглашение и на последней нажать кнопку Generate.

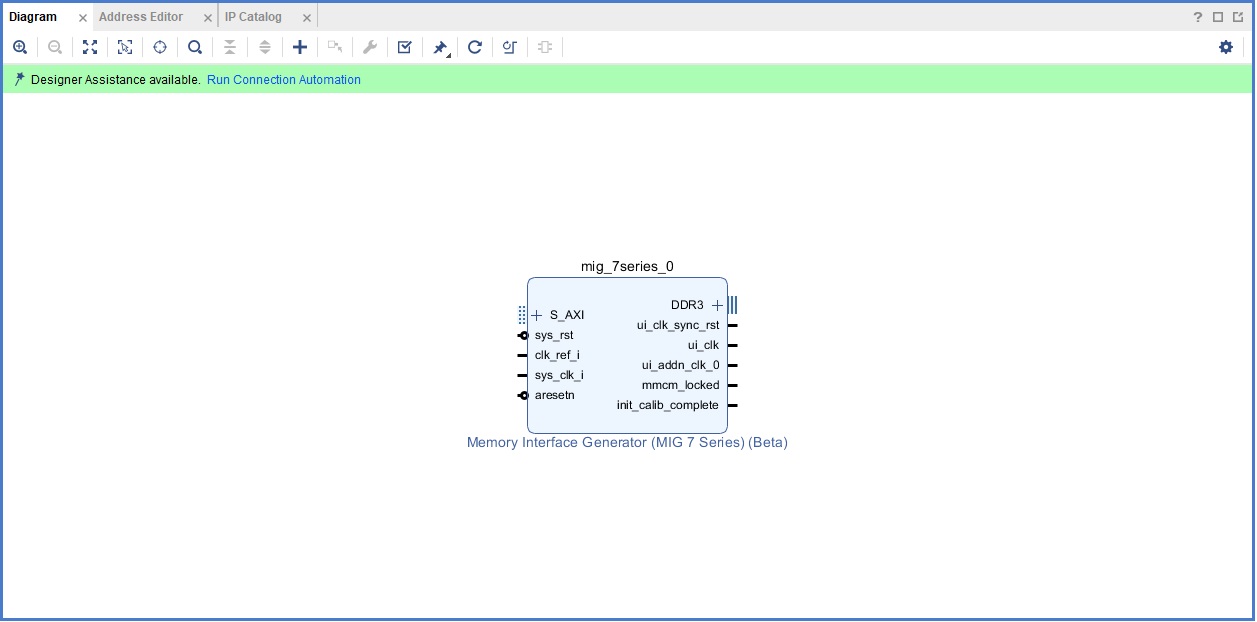

В результате чего наше ядро должно преобразоваться и принять следующий вид (рисунок 16):

Рисунок 16 – Окно Block Design с обновленным MIG 7

Подключение процессора к памяти

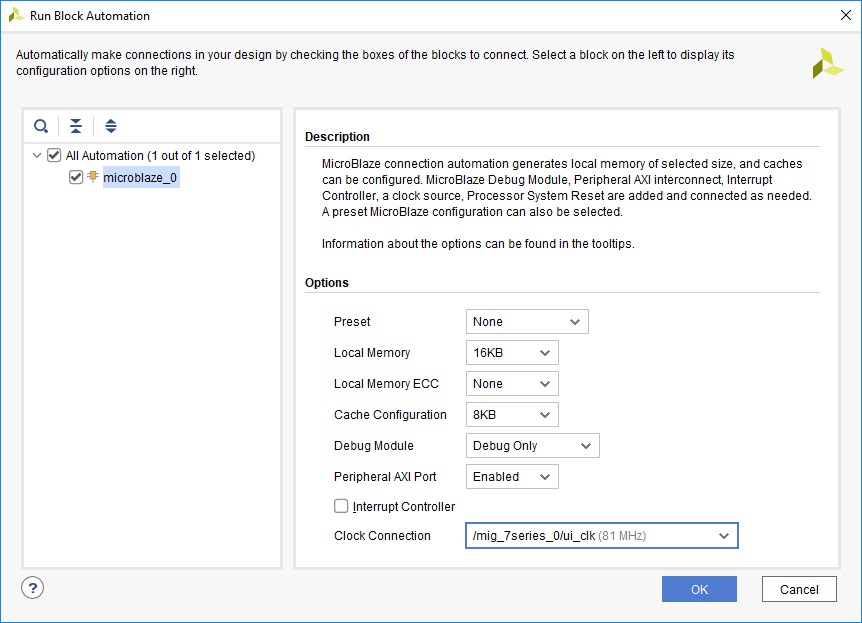

Теперь мы можем добавить MicroBlaze в наш проект. Нажимаем кнопку Add IP и добавляем его в рабочее пространство. Запустим Run Block Automation и установим следующие параметры (рисунок 17):

Рисунок 17 – Настройки для Microblaze

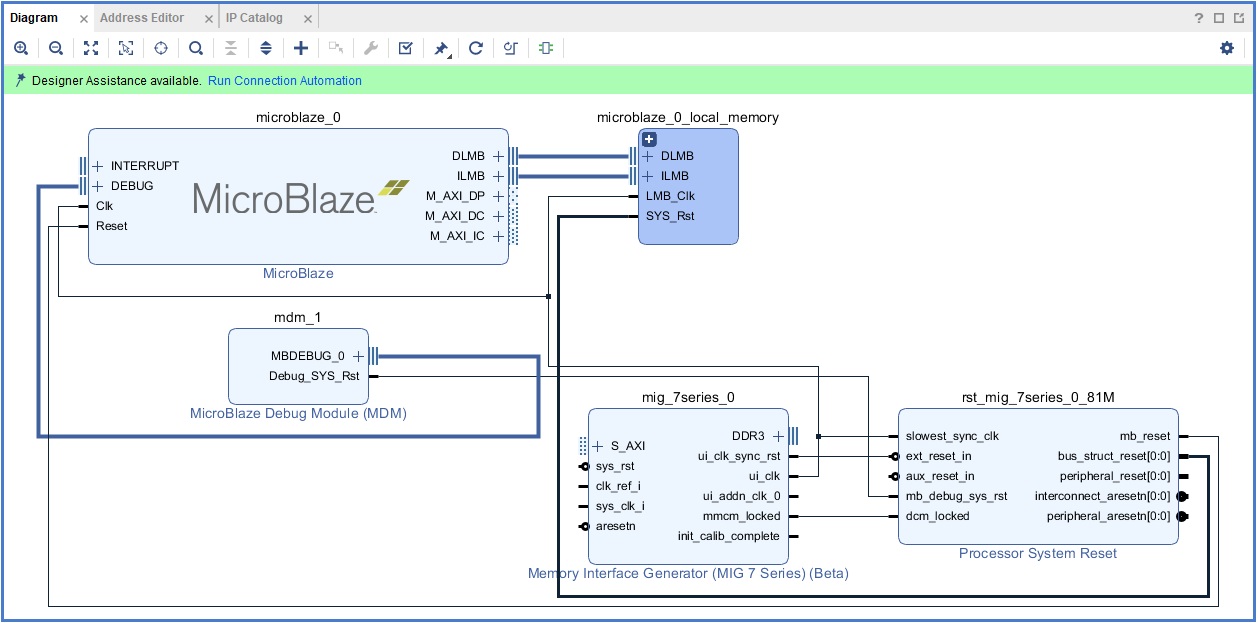

После завершения автоматизации появятся локальная память, модуль дебага и модуль сброса (рисунок 18).

Рисунок 18 – Окно Block Design после автоматизации

Добавим подтяжку к «1» для входов сброса, подключим опорную частоту к 200 МГц и выведем наружу сигналы памяти DDR. Окно теперь должно выглядеть вот так (рисунок 19):

Рисунок 19 – Окно Block Design после автоматизации

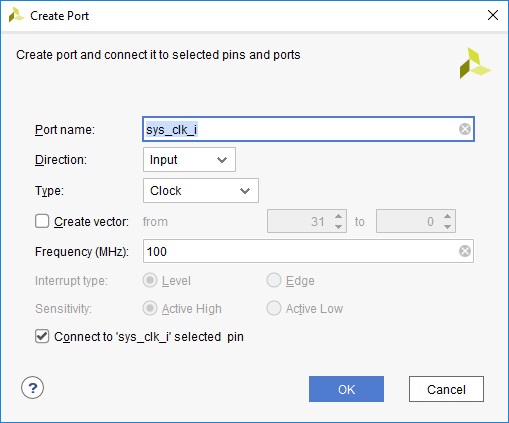

Теперь добавим внешний порт к нашей входной частоте. Нажмем один раз на sys_clk_i в блоке MIG 7, чтобы выделить его, затем в свободном поле щелкнем правой кнопкой мыши и выберем пункт Create Port. Должно открыться следующее окно (рисунок 20):

Рисунок 20 – Создание порта

Оставляем все по умолчанию и нажимаем Ok. Если просто выбрать опцию Make External, Vivado создаст внешний порт с именем, отличным от того, которое было создано в файле констрейнов, и на этапе синтеза и имплементации появится критическое предупреждение, указывающее на отсутствие в дизайне порта с именем sys_clk_i.

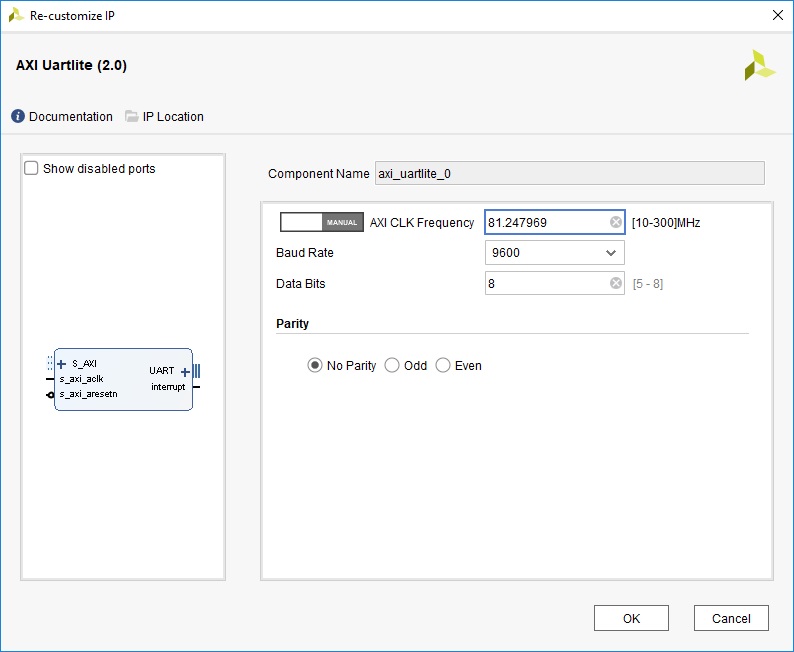

Добавим модуль UARTLite и сконфигурируем его следующим образом (рисунок 21):

Рисунок 21 – Конфигурация UARTLite

Установленная частота соответствует частоте, сгенерированной MIG 7 для пользовательского интерфейса. UART нам понадобится позже для теста памяти

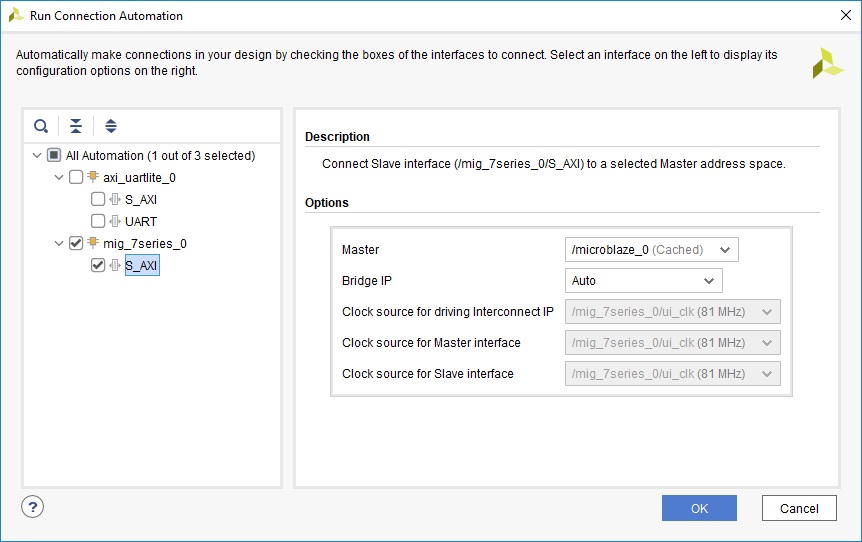

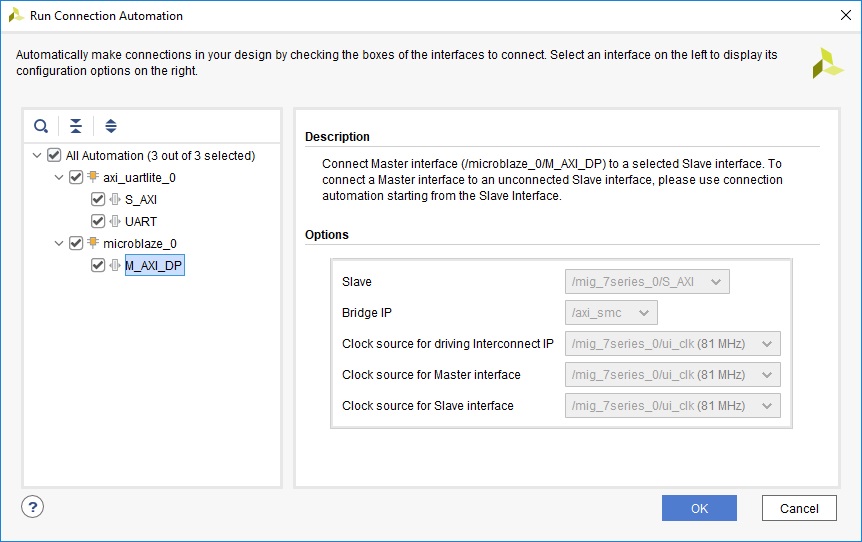

Теперь запустим Run Connection Automation для кэша MicroBlaze (рисунок 22).

Рисунок 22 – Run Connection Automation для кэша MicroBlaze

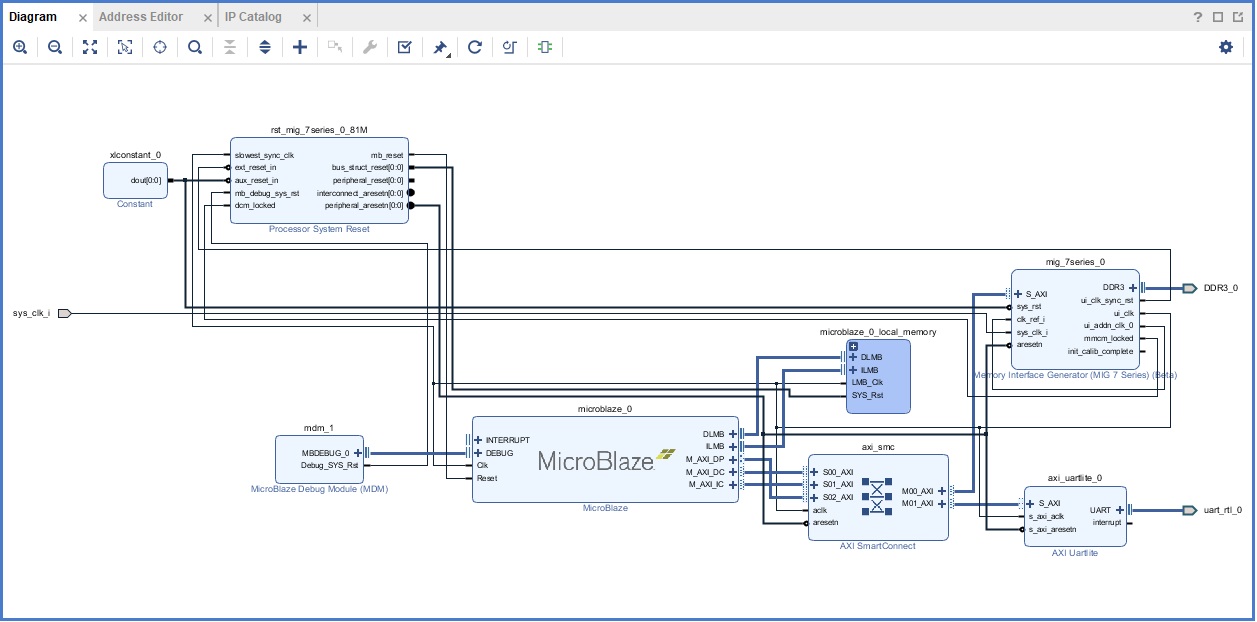

Теперь запустим автоматизацию подключения периферии (рисунок 23).

Рисунок 23 – Run Connection Automation для периферии

После этого нажмем кнопку Optimize Routing и получим следующее поле блок дизайна (рисунок 24):

Рисунок 24 – Окно Block Design после регенерации

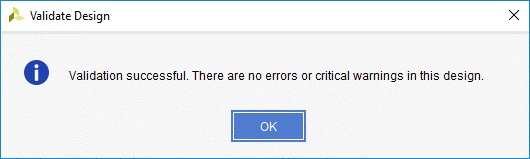

Теперь можно запустить Validate Design, и, если все правильно, мы получим следующее уведомление (рисунок 25):

Рисунок 25 – Уведомление об успешной проверке

Запустим синтез, предварительно создав обертку нашего блок дизайна, и немного подождем.

После синтеза откроем I/O Planning и назначим оставшимся сигналам порты. Сохраним свой констрейн файл и запустим генерацию битстрима. Если никаких ошибок и критических предупреждений не появилось, то после ее окончания выберем File -> Export -> Export Hardware без битстрима, а затем запустим SDK.

Запуск проверки памяти

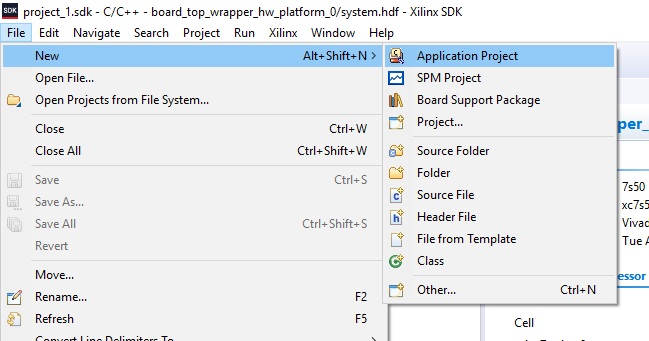

После запуска SDK создадим Application Project (рисунок 26):

Рисунок 26 – Создание нового проекта

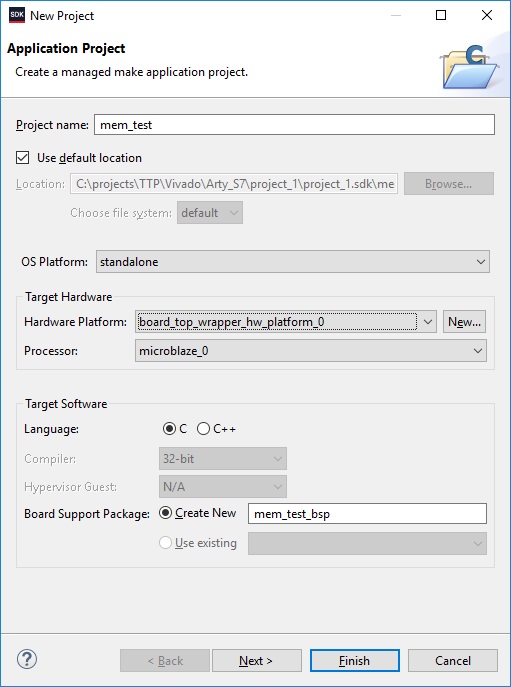

Выставим следующую конфигурацию в первой вкладке создания проекта (рисунок 27):

Рисунок 27 – Конфигурация на первой вкладке

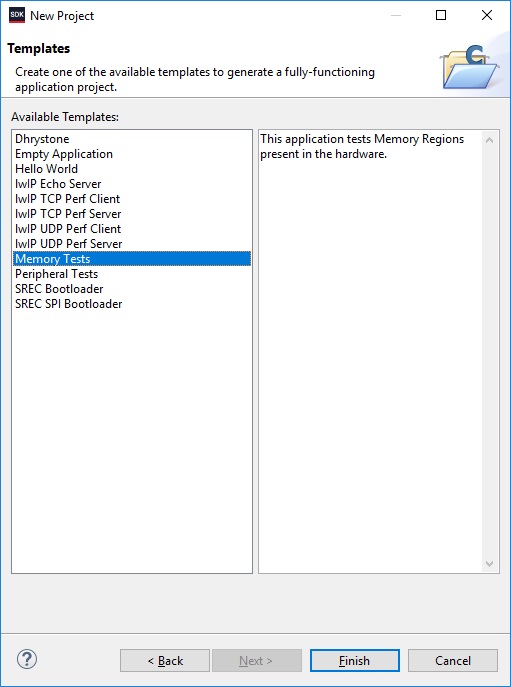

На второй вкладке выберем шаблон проекта Memory Tests (рисунок 28).

Рисунок 28 – Шаблоны проектов

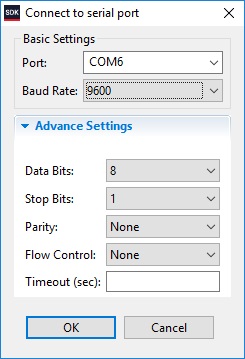

Теперь добавим и запустим SDK Terminal со следующими настройками, исключая номер COM-порта, так как он у вас может быть любым другим (рисунок 29):

Рисунок 29 – Настройки COM-порта

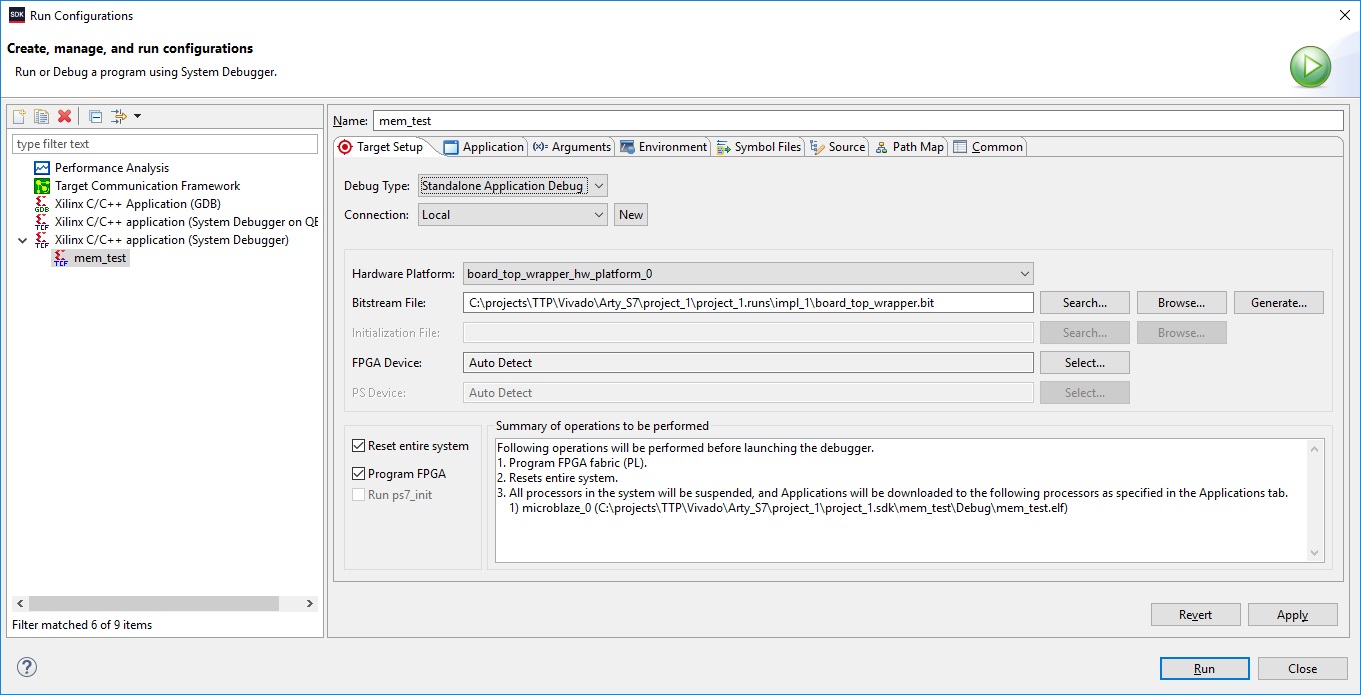

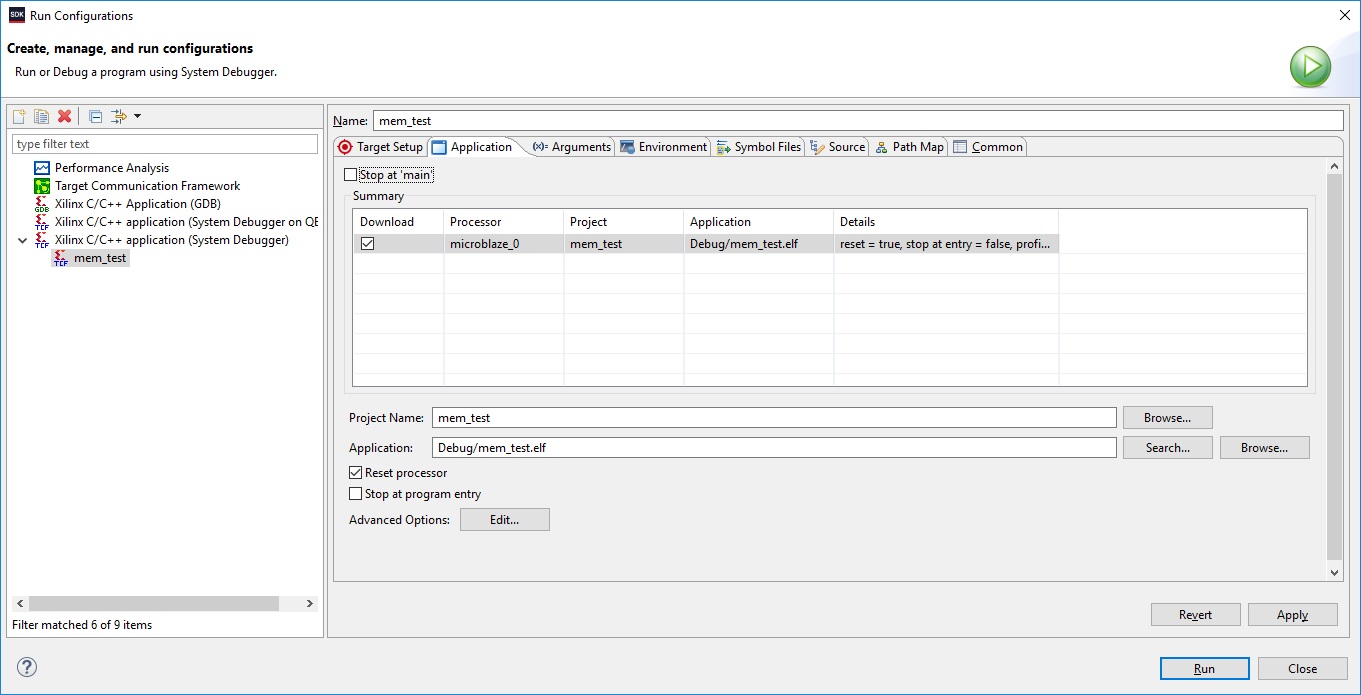

Теперь настроим Run Configuration (рисунок 30).

Рисунок 30 – Настройка Run Configuration, вкладки Target Setup

И во второй вкладке (рисунок 31):

Рисунок 31 – Настройка Run Configuration, вкладки Aplication

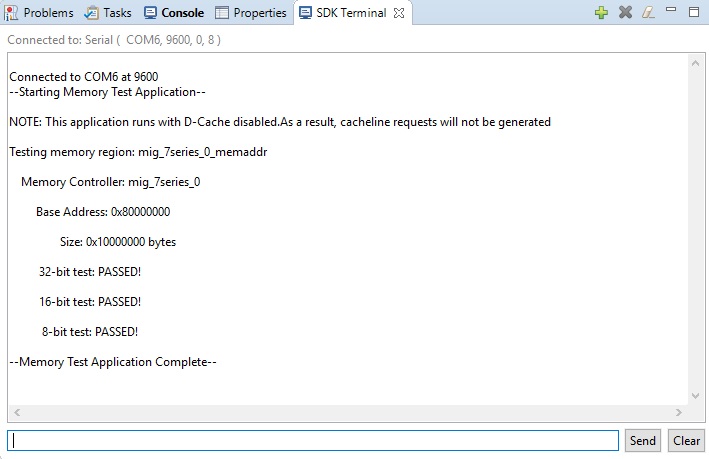

Теперь запустим программирование нашей FPGA. Если все было сделано правильно, то в строке терминала мы увидим похожую запись (рисунок 32):

Рисунок 32 – Сообщение о прохождении теста памяти

Это означает, что тест нашей памяти был пройден и все настроено правильно. Теперь можно самостоятельно посмотреть файлы тестового проекта и попытаться в них разобраться. Если возникли ошибки, то можно вернуться к самому началу или попытаться почитать предыдущие статьи о настройке процессорной системы MicroBlaze.

Список литературы