Архив новостей из мира FPGA

Компания Analog Devices поглотила производителя eFPGA - компанию FlexLogix

Компания Analog Devices поглотила производителя eFPGA - компанию FlexLogix (а производителей eFPGA на рынке раз-два и обчелся)

3714

FPGA 2024.1 : Слёт и второй номер журнала

ПЛИС-культ привет, FPGA комьюнити! Два коротких объявления: 1. Ищем докладчиков для нашего слета FPGA разработчиков, который состоится в Москве-Питере-Новосибирсике/Томске в концеМая--началеИюня. Регистрация пока не открыта, но мы хотим сформировать программу заранее Т ... Читать дальше »

4711

0 Бесплатные тренинги от Intel на июль

Товарищи, если вы сможете попасть на эти тренинги, поделитесь, пжлст, материалами тренинга или их записью с FPGA коммунити. Напишите мне в телегам @KeisN13 или почту admin@fpga-systems.ru Давайте сделаем бесплатные материалы тренингов доступными для всех.

5093

0

AMD анонсирует самый ёмкий FPGA чип

Компания AMD / Xilinx не перестаёт нас радовать покорением новых вершин. Вслед за недавним анонсом Spartan US+ мы в первом-втором квартале 2024 сможем лицезреть монстра серии Versal - VP1902,которая должна стать самой ёмк ... Читать дальше »

3344

0

Релиз Chisel v3.6.0-RC2

Разработчики языка генерации аппаратуры Chisel выпустили в свет новую версию 3.6.0. Версия примечательна прежде всего тем, что в ней заменили компилятор ... Читать дальше »

2973

0

RISC-V в образовании

RISC-V в образовании Коллеги из RISC-V International попросили поделиться с вами опросником о заинтересованности в подготовке, преподавании курсов на базе RISC-V. В любом из возможных направлений, будь то: Processor Design, Compilers, OS, Embedded System Design. Ассоциация RISC-V стремится наладить к ... Читать дальше »

2483

0

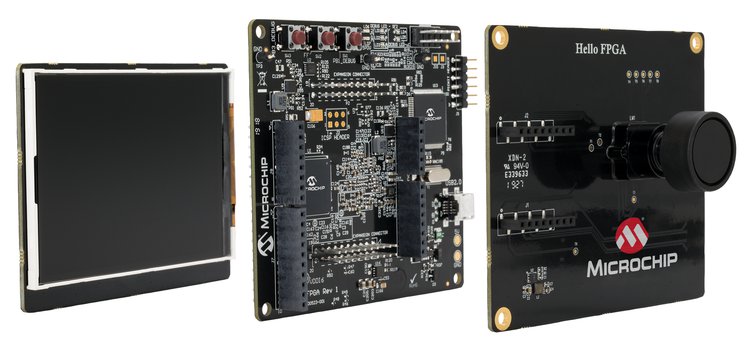

Розыгрыш отладок Hello FPGA от Microchip

На портале Crowd Supply появилась информация о розыгрыше 30 отладочных комплектов " Hello FPGA", выполненной на ПЛИС от компании Microchip. Согласно анонсу будет три способа получить отладку: ... Читать дальше »

2763

0

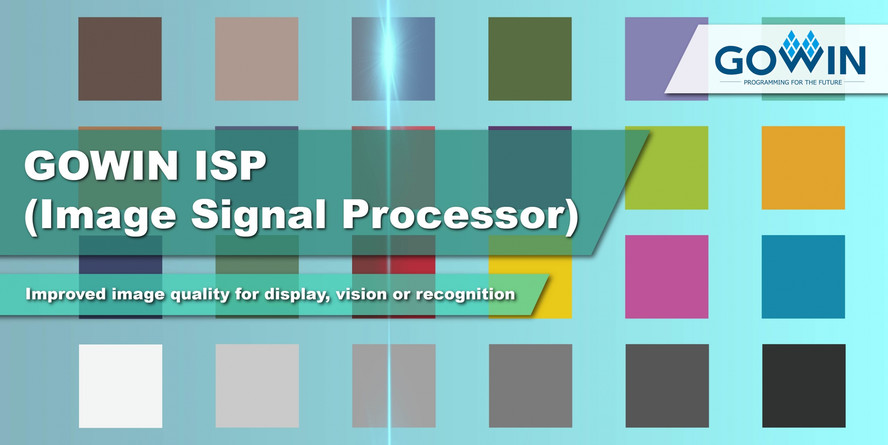

GOWIN Semiconductor пополняет библиотеку IP собственным ISP (Процессор обработки изображений)

GOWIN Semiconductor Corp., самая быстрорастущая в мире компания по программируемой логике, пополняет свой IP-портфель решением ISP (процессор обработки изображений) и эталонный дизайн для ПЛИС GOWIN. Портфель IP-ядер включает CFA (Матрица цветовых фильтров/Дебаер), CCM (Матрица цветокоррекции), Гамма-коррекции, AE (Автоматическая экспозиция) и AWB (Автоматический баланс белого) ... Читать дальше »

2765

0

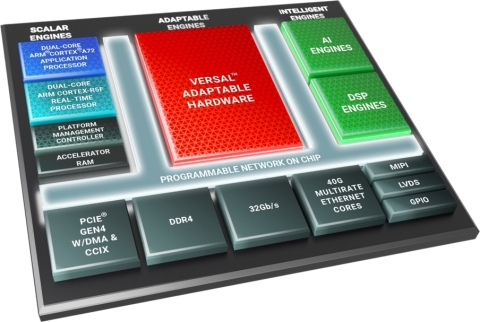

Анонсированы Xilinx Versal ACAP серии AI Edge

Компания Xilinx представила Versal™ серии AI Edge. Обладая в 4 раза большей производительностью ИИ на ватт по сравнению с GPU и в 10 раз большей плотностью вычислений по сравнению с адаптивными SoC предыдущего поколения, серия Versal AI Edge является самым масштабируемым и адаптируемым изделием в мире для распределенных интеллектуальных систем следующего поколения ... Читать дальше »

2871

0

XIlinx приобрел Silexica

Компания Xilinx объявила о покупке компании Silexica, частного поставщика инструментов высокоуровнего синтеза C/C++. Набор утилит SLX FPGA от Silexica предоставляет разработчикам беспрецедентный опыт разработки приложений на ПЛИС и адаптивных SOC на языках C/C++. Эта технология будет интегрирована с единой программн ... Читать дальше »

3022

0 1-10 11-20 |

0