Архив новостей из мира FPGA

Путь в opensorce инструменты для FPGA

Тони и Адам обсудят инновации и изменения, необходимые для привлечения внимания к open-source. Набор инструментов Raptor Design Suite от Rapid Silicon уже доказал, что проекты могут быть безопасными даже в среде с открытым исходным кодом. Вебинар состоится 25 января 2022 Врем ... Читать дальше »

6489

Вебинар Understanding Versal

3735

0

Серия из 3-х семинаров Vitis AI Development on AMD Xilinx Adaptive Platforms

3070

0

Вебинар: Hacking FPGAs & SoC FPGAs

ПЛИС все чаще используются в критически важных приложениях.

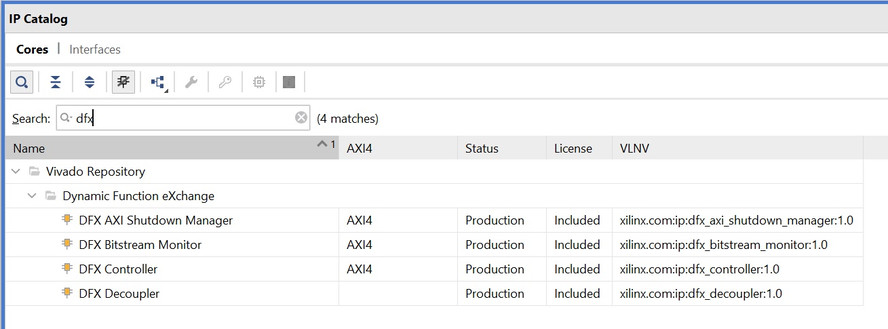

Введение в технологию DFX от Xilinx. Вебинар

Современная технология реализации частичной реконфигурации (DFX – Dynamic Function eXchange) позволяет загружать в ПЛИС только те ядра, которые используются в данный момент, и, таким образом, эффективно и экономно использовать объём за счет разделения ресурсов ПЛИС. В текущих условиях экономия ресурсов – это актуальная задача. Кроме того, на технологии DFX построены аппаратные ускорители Xilinx. Разработка c использованием DFX значительно сложнее, чем стандартный маршрут проектирования. ... Читать дальше »

801

0

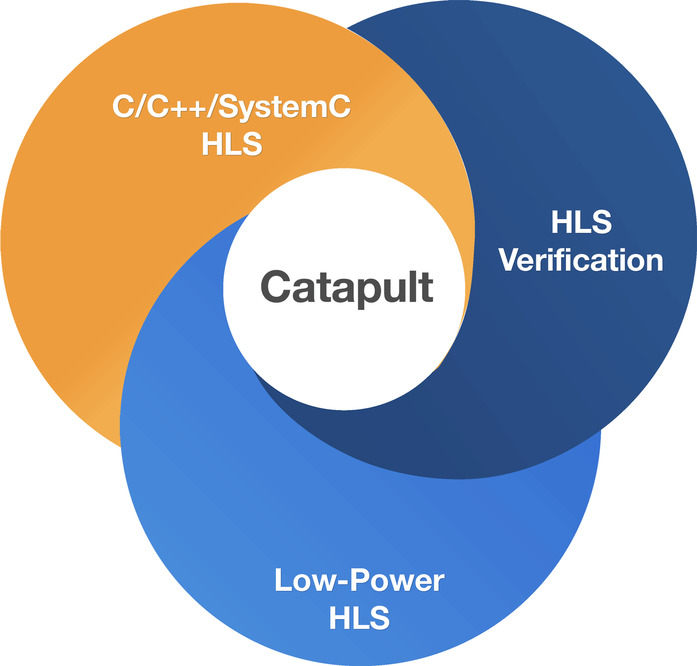

Использование Catapult HLS для SW/HW разработки микросхемы ИИ ускорителя в Harvard University

Аннотация Замедление закона Мура в сочетании с растущей популярностью машинного обучения привело к появлению чипов с ориентированной на приложения архитектурой, поскольку простого масштабирования кремния уже недостаточно для достижения желаемых показателей производительности и мощности. Чтоб ... Читать дальше »

1251

0

Вебинар: Common Mistakes in VHDL 26.01.2022

26.01.2022 намечается интересный вебинар. Судя по названию речь пойдёт о типичных ошибках при написании кода на языке VHDL. Подробная программа и регистрация здесь: ... Читать дальше »

919

0

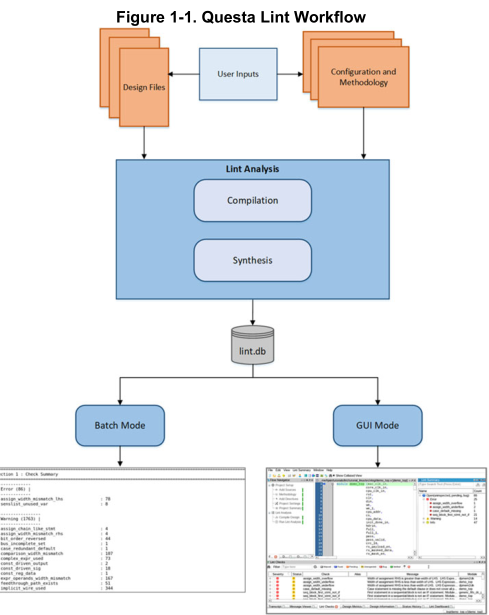

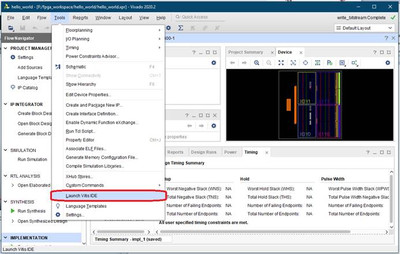

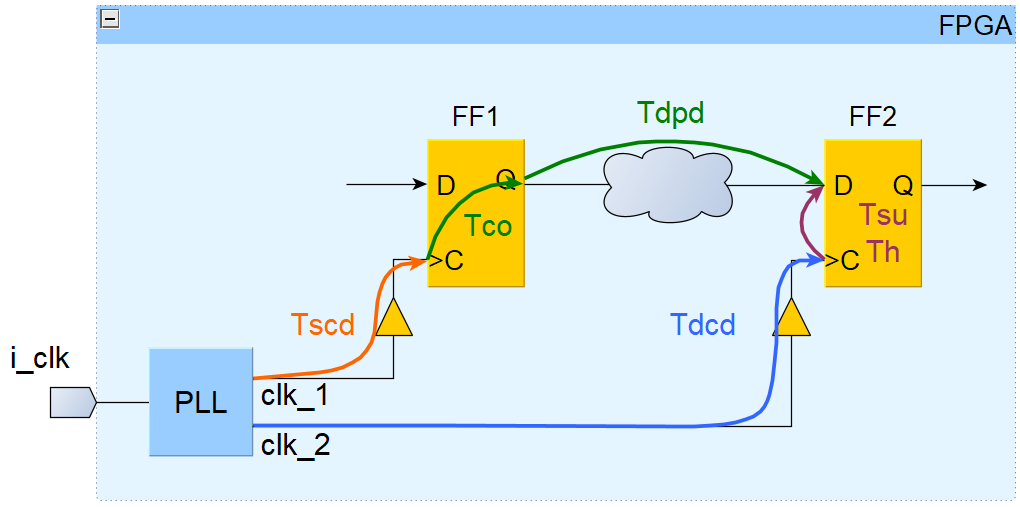

Введение в Questa Lint и Questa CDC для разработчиков

Вы когда-нибудь встречали RTL-код, который проходит симуляцию, но все равно приводит к ошибкам из-за наличия недостижимого кода, выхода значений за допустимый диапазон или неправильного порядка выполнения? Вы когда-нибудь ... Читать дальше »

1648

0

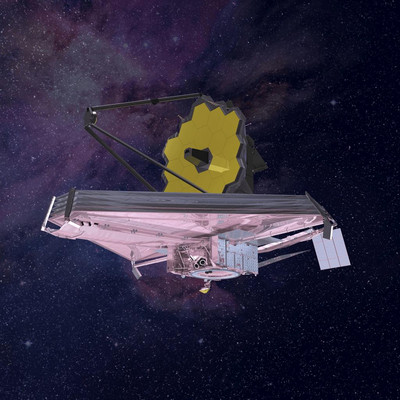

Xilinx Technologies for New Space / Space 2.0

Рынок нового космоса (космоса 2.0) продолжает расти очень быстрыми темпами, и заказчики требуют от ПЛИС и SoCs все больше функций, высокоскоростных интерфейсов, программирования на орбите и качественных программных инструментов и поддержки IP. ... Читать дальше »

1075

0

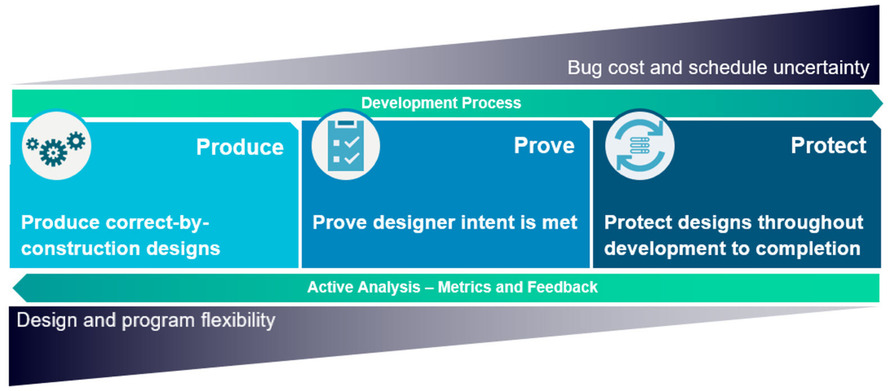

Повышаем качество RTL кода

Проектирование электроники, процесс итеративный, требующий постоянной верификации. В случае разработки микросхем или сложнофункциональных (СФ) блоков, ошибки могут приводить к многомиллионным затратам на перевыпуск в кремнии или исправлению багов в серийно выпускаемом изделии. Очевидным методом сокращения подобных издержек и снижением нагрузки на конечные этапы верификации, является выявление потенциальных ошибок непосредственно в RTL коде, еще до этапа создания тестового окружения. ... Читать дальше »

1403

0 |

0