Введение в Questa Lint и Questa CDC для разработчиков

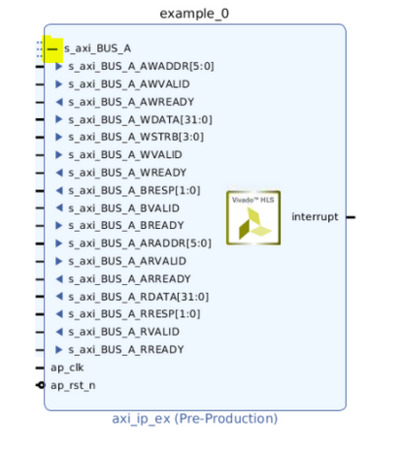

Вы когда-нибудь встречали RTL-код, который проходит симуляцию, но все равно приводит к ошибкам из-за наличия недостижимого кода, выхода значений за допустимый диапазон или неправильного порядка выполнения? Вы когда-нибудь имели дело с проектами, содержащими несколько тактовых доменов, приводящих к возникновению глитчей и сбоев на устранение которых уходили недели? Повторное переписывание и перекомпиляция кода для ПЛИС - это чрезвычайно медленный и подверженный ошибкам процесс. Поэтому важно использовать правильные инструменты верификации, прежде чем делать релиз.

Моделирование и статический временной анализ отлично подходят для начальной проверки, но этого недостаточно для полноценной верификации. Для достижения доверенности к коду уровня релиза необходимо применять методологии, которые выходят за рамки простого моделирования.

В рамках вебинара мы сосредоточимся на:

- Вопросе почему качество кода имеет решающее значение, не зависимо от того, пишите ли вы под FPGA, ASIC или разрабатываете IP?

- Что такое метастабильность и как она повлияет на первый запуск изготовленной микросхемы?

- Как решение этих вопросов в процессе проектирования имеет решающее значение для достижения поставленных сроков при ограниченных ресурсах?

Вы узнаете:

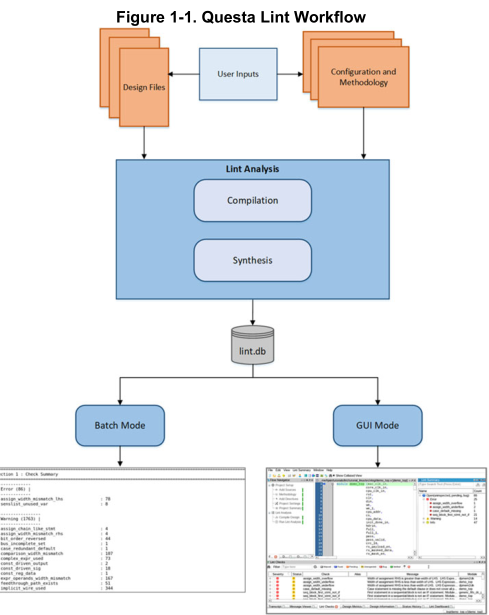

- Как линтинг может улучшить код RTL

- Как правильно строить схемы передачи данных при пересечении тактовых доменов

Целевая аудитория

- Инженеры-разработчики и верификаторы ASIC / FPGA / IP

- Руководители отделов RTL разработки и верификации

Затрагиваемые продукты

Вебинар состоится 25 января 2022

Время 10:00 AM Pacific Standard Time

Ссылка на регистрацию