Vivado Quality of Result (Перевод статьи MicroZed Chronicles)

В данной статье будут рассмотрены инструменты Quality of Result Assesment [QoRA] и Quality of Result Suggestions [QoRS] поскольку оба этих инструмента предоставляют информацию для достижения необходимых временных ограничений [timing closure - временное соответствие, временные ограничение].

В предыдущей статье был проведен разбор инструмента Design Analysis Report в Vivado для понимания разрабатываемого дизайна и корректировки расхождения результатов временных ограничений, получаемых на этапе имплементации.

Хотя нам не нужно запускать все доступные инструменты доступные для имплементации заново, а достаточно иметь открытым окно задач имплементации [как показано на скриншоте выше], чтобы получить результаты отчета для QoR Assesment или QoR Suggestions.

В данном примере, был выполнен синтез и начальная оптимизация этапа имплементации. Выполнение только предварительных этапов имплементации значительно экономит время и позволяет раньше найти и исправить возникающие ошибки.

Сначала рассмотрим QoR Assesment. Мы можем сгенерировать данный отчет [report] Используя следующую команду в TCL-консоли [подробнее про эти команды можно прочитать в Vivado Design Suite Tcl Command Reference Guide UG835 ]:

report_qor_assessment -file <filename>

# report_qor_assessment - доступен с 18-й версии Vivado

Определив имя файла, мы можем сохранить отчет как текстовый файл, что намного удобнее, чем просто просматривать результаты в окне TCL.

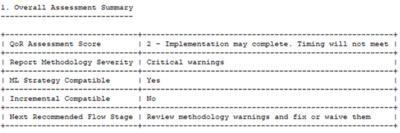

Отчет об оценке QoR Assement будет разделен на три раздела:

- Общая оценка

- Детали QoR Assesment

- Детали проверки методологии

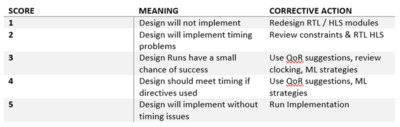

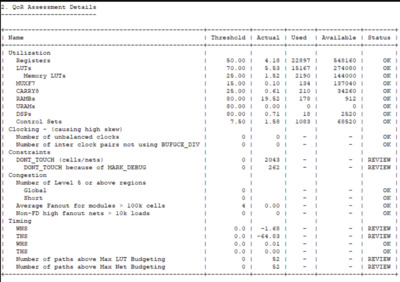

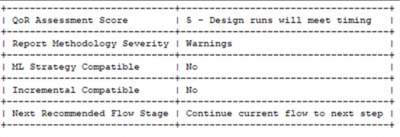

Общая оценка присваивает проекту балл от 1 до 5 и указывает на вероятность того, что дизайн будет реализован без проблем.

Как показано в примере - для данного дизайна имплементация будет выполнена, но необходимые временные ограничения не будут достигнуты.

Детальный отчет QoRA предоставляет информацию о низкоуровневых элементах [примитивах], результаты которых можно объединить для получения общей оценки. REVIEW в поле Status, означает что рекомендованные параметры [например WNS] были превышены или не соблюдены.

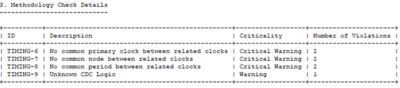

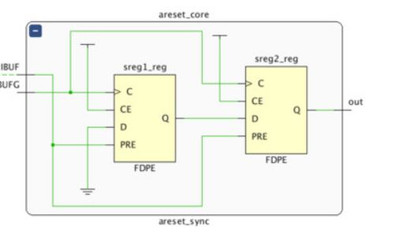

Наконец, проверка методологии покажет, какая методология проектирования не соблюдается должным образом. В этом случае мы видим, что у нас нет констрейнов, которые определяют связь между clock’ами в дизайне.

Теперь, выполнив начальную оптимизацию (opt_design в окне TCL) и получив отчет QoRA, мы можем внести любые необходимые изменения, необходимые для констрейнов, настроек имплементации, выбора целевого кристалла и speed grade. При необходимости возможно внести любые необходимые изменения в модулях RTL и HLS в рамках проекта.

Если оценка QoRA равна 5, можно просто запустить оставшиеся этапы имплементации и генерации bitstream. Однако в более сложных проектах, скорее всего, придется выполнить дополнительный анализ для того чтобы этап имплементации завершился без ошибок.

Хотя в отчете QoRA могут быть указаны возможные проблемы, дополнительно необходимо провести оценку дизайна (place_design - выполнить в окне TCL) и получить отчет QoR Suggestions, прежде чем предпринимать какие-либо действия.

report_qor_suggestions -file <filename>

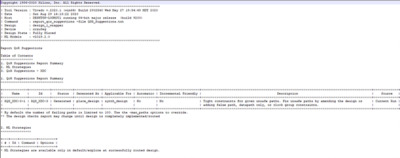

В верхней части таблицы отчета QoRS представлены рекомендации и предложения, которые окажут наибольшее влияние на анализируемый дизайн.

В таблицу также включен столбец под названием Automatic. В данном столбце указано будут ли предложения и рекомендации автоматически применены после повторного запуска имплементации или необходимо вручную внести правки, чтобы исправить выявленные проблемы и недостатки.

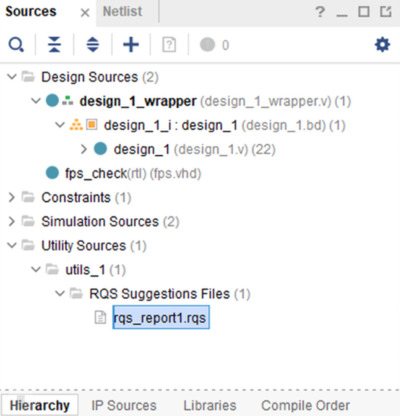

Чтобы использовать QoRS, необходимо сохранить RQS файл, а затем добавить его в проект. Запись результатов QoRS в файл выполняется следующей командой:

write_qor_suggestions <filename.rqs>

Файл RQS должен быть добавлен в проект в качестве Utility Sources:

В данном примере необходимо было исправить файл констрейном для корректного определения связей между clock.

После исправление файла констрейнов и перезапуска инструмента QoRA отчет указывает, что дизайн оценивается в 5 баллов, что означает что имплементации успешно завершится с заданными временными ограничениями .

Использование инструментов QoR Assessment и QoR Suggestions может помочь достигнуть заданных временных ограничений.