Высокоуровневый синтез для исследования архитектуры аппаратного/программного обеспечения для инференса

Периферийные устройства всех типов становятся умнее, благодаря способности слушать нас, понимать наши жесты и даже распознавать нас. Этот интеллект исходит из возможностей глубоких нейронных сетей. Обработка данных требует больших вычислительных затрат и может легко перегружать встроенные процессоры при ограниченных бюджетах энергопотребления некоторых периферийных систем. Одним из способов решения этой проблемы является перенос вычислительно сложных частей алгоритма в аппаратуру, где это может быть выполнено быстрее и эффективнее.

Практический способ приблизиться к этому - использовать виртуальную платформу, которая представляет собой программное представление аппаратной платформы (система на кристалле или плате), смоделированное на достаточно высоком уровне абстракции, где выполнение программного обеспечения может быть смоделировано без сложностей аппаратного обеспечения низкого уровня. Платформа может выполнять весь программный стек, включая ОС и гипервизор, на модели процессора с имитацией набора команд (ISS), которая, в свою очередь, моделируется на главном компьютере.

На этом семинаре будет представлен процесс проектирования, включающий совместное проектирование HW / SW и высокоуровневый синтез (HLS), который позволяет разработчикам переносить вычислительные функции из программного обеспечения, работающего на встроенном процессоре, на аппаратный ускоритель. Перенос функции из программного обеспечения в аппаратное повышает производительность и эффективность проектирования.

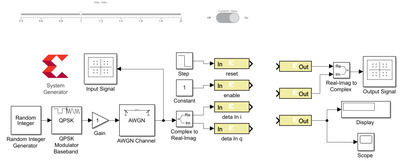

В примере дизайна, использованном на этом семинаре, будет реализован алгоритм wake word. Алгоритмы Wake word должны непрерывно отслеживать входной аудиопоток для одного или нескольких ключевых слов и пробуждать систему, если слово найдено. Это требует значительной предварительной обработки звука, а также инференса для глубокой нейронной сети. Эти вычисления выполняются несколько раз в секунду. Перенос функций на аппаратное обеспечение значительно увеличит время автономной работы этого приложения.

Вы увидите, как SpaceStudio от Space Codesign охватывает этап создания/захвата алгоритма и проверку алгоритма на виртуальной платформе. Оптимизация архитектуры, такая как исследование для разделения алгоритма между многоядерным процессором и ПЛИС, может быть выполнена с полной компиляцией системы для выполнения на физической плате.

Agenda

- 8:00AM PST-11:30AM PST

- 8:00 AM (30 min) - Intro and Overview of High-Level Synthesis

- 8:30 AM (30 min) - Algorithm Description

- 9:00 AM (30 min) - Introduction to SpaceStudio

- 9:30 AM (30 min) - HW/SW Partitioning with SpaceStudio: A Practical Case Study - Part 1

- 10:00 AM (30 min) - Designing with HLS

- 10:30 AM (30 min) - Architecture refinement at the C++ level

- 11:00 AM (15 min) - HW/SW Partitioning with SpaceStudio: A Practical Case Study - Part 2

- 11:15 AM (15 min) - Results and conclusion

- 11:30 AM (15 min) - Wrap-up and Q&A

Семинар состоится: 24 января 2023

Время: в 19-23:30 по Мск

Трансляция и запись будут доступны на нашем Youtube канале по ссылке