Vivado reprorts => report_clocks

report_clocks

Vivado 2017.3

Синтаксис

report_clocks [-file <arg>] [-append] [-return_string] [-quiet] [-verbose] [<clocks>]

Возвращаемое значение

Нет

Категории

Report, Timing

Описание

Возвращает таблицу, показывающую все тактовые сигналы в проекте, включая тактовые сигналы различных типов: propagated, generated, auto‑generated, virtual, inverted в текущем открытом синтезированном или имплементированном проекте. Более детальную информацию о каждом тактовом сигнале проекта можно получить командой report_clock_utilization.

Примечание: по умолчанию команда выдаёт отчёт в TCL консоль или стандартное устройство ввода/вывода. Однако результаты также могут быть записаны в файл или возвращены в виде строки.

Аргументы

-file <arg> - (опционально) Записать отчёт в файл. Если файл существует, он будет перезаписан или же информация будет добавлена в файл, если использована опция –append

Примечание: если путь не указан в имени файла, то файл будет записан в текущую рабочую директорию или в директорию, из которой запущена среда.

-append – (опционально) добавить выходные данные команды в файл, вместо того, что бы его перезаписать.

Примечание: опция –append может быть использована только с опцией ‑file

-return_string – (опционально) Сформировать выход команды в TCL строку, вместо того, что бы отобразить её в стандартном устройстве ввода/вывода. TCL строка может быть определена как переменная и в последующем обработана.

-quiet – (опционально) Команда выполняется в «тихом» режиме, сообщения команды не отображаются. Команда возвращает TCL_OK независимо от каких-либо ошибок её выполнения.

Примечание: Если ошибка обнаружена в командной строке при вводе команды, то ошибка будет отображена. Не отображается ошибки, которые появляются во время выполнения команды.

-verbose – (опционально) Временное переопределение ограничений на количество выводимых сообщений команды.

Примечание: количество выводимых сообщений может регулироваться с помощью команды set_msg_config.

<clocks> - (опционально) Вывод отчёта ля тактовых сигналов, соответствующих шаблону. По умолчанию шаблон состоит из подстановочного символа «*», который позволяет вывести все тактовые сигналы проекта. Может быть указан более чем один тактовый сигнал.

Примеры

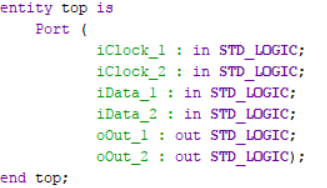

Рассмотрим модуль, у которого имеется два тактовых сигнала «iClock_1» и «iClock_2»:

Код архитектуры, реализующий два триггера по одному на каждый тактовый сигнал:

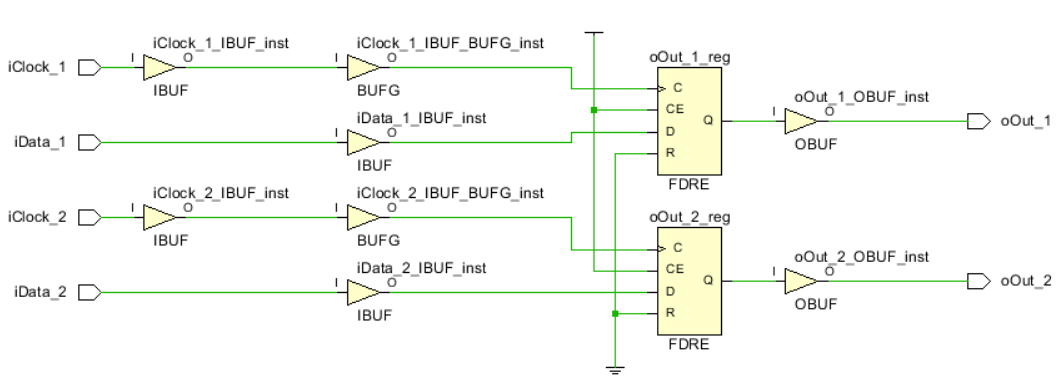

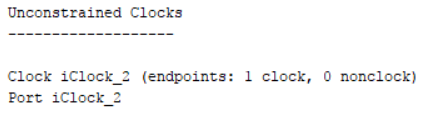

Предположим, что параметры определены только для тактового сигнала «iClock_1», а сигнал «iClock_2» не имеет каких либо параметров.

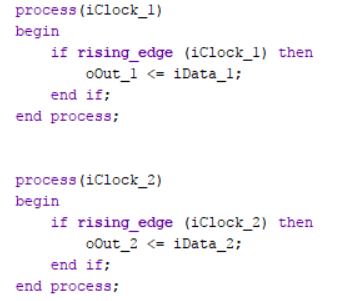

- Выполним синтез. Netlist выглядит следующим образом

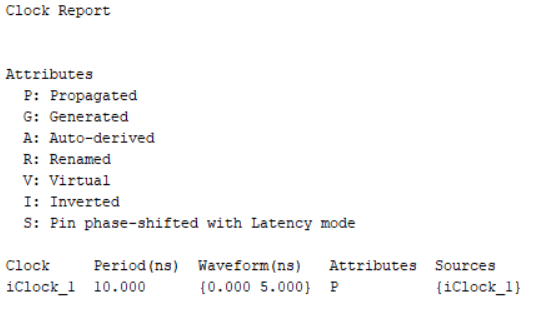

- Запустим report_clocks:

Как вы видите, отчёт report_clock выдаёт только сведения о тех тактовых сигналах, которые имеют соответствующие ограничения. Не определённые тактовые сигналы «undefined» в этом отчёте не отображаются.

Примечание: узнать какие сигналы являются «undefined» или «Unconstrained» можно с помощью команды report_clock_networks

- Следующая команда возвращает имя, период, временную диаграмму и источник тактовых сигналов в текущем проекте и записывает выход команды в файл:

report_clocks –file {report_clocks.txt}

Содержимое отчёта в текстовом файле аналогично тому, что выводится в консоль.

- Следующий пример возвращает отчёт для тактовых сигналов, которые содержат символы «Clock» в имени (чувствительно к регистру букв):

report_clocks *Clock*

Также посмотрите:

• create_clock

• create_generated_clock

• report_clock_utilization

Литература

UG835 Vivado Design Suite Tcl Command Reference Guide