FPGA Daily News #038

31.08.2022 08:17

1321

0

0.0

- AnDAPT adds PMICs for Xilinx UltraScale+ FPGAs: embedded

AnDAPT releases custom power delivery products for AMD-Xilinx Zynq UltraScale+ and Xilinx Artix UltraScale+ FPGA and adaptive SoC families.

- RVfpga In-person One-day Workshop - RISC-V International

About this event RVfpga (RISC-V fpga) Understanding Computer Architecture – A Hands-On, In-Person, One-Day-Workshop Bring RISC-V to your course in computer architecture using RVfpga This workshop shows how...

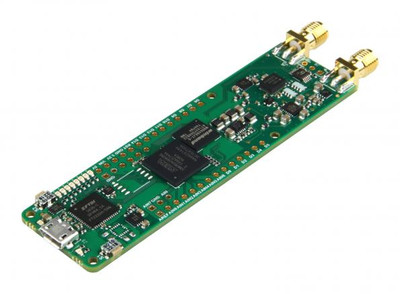

- Bajiu Lite | Crowd Supply

An open source, resource-rich FPGA development board with a custom RISC-V development environment

- ResearchGate

ResearchGate is a network dedicated to science and research. Connect, collaborate and discover scientific publications, jobs and conferences. All for free.

- Adaptive Subsampling for ROI-based Visual Tracking: Algorithms and FPGA Implementation | IEEE Journals & Magazine | IEEE Xplore

There is tremendous scope for improving the energy efficiency of embedded vision systems by incorporating programmable region-of-interest (ROI) readout in the image sensor design. In this work, we study how ROI programmability can be leveraged for vision applications by anticipating where the ROI will be located in future frames and switching pixels off outside of this region. We refer to this process of ROI prediction and corresponding sensor configuration as adaptive subsampling. Our adaptive subsampling algorithms comprise an object detector and an ROI predictor (Kalman filter) which operate in conjunction to optimize the energy efficiency of the vision pipeline with the end task being object tracking. To further facilitate the implementation of our adaptive algorithms in real systems, we select a candidate algorithm and map it onto an FPGA. Leveraging Xilinx Vitis AI tools, we designed and accelerated a YOLO object detector-based adaptive subsampling algorithm. In order to further improve the algorithm post-deployment, we evaluated several competing baselines on the OTB100 and LaSOT datasets. We found that coupling the ECO tracker with the Kalman filter has a competitive AUC score of 0.4568 and 0.3471 on the OTB100 and LaSOT datasets respectively. Further, the power efficiency of this algorithm is on par with, and in a couple of instances superior to, the other baselines. The ECO-based algorithm incurs a power consumption of approximately 4 W averaged across both datasets while the YOLO-based approach requires power consumption of approximately 6 W (as per our power consumption model). In terms of accuracy-latency tradeoff, the ECO-based algorithm provides near-real-time performance (19.23 FPS) while managing to attain competitive tracking precision.

- GitHub - giuseros/nand2tetris

Contribute to giuseros/nand2tetris development by creating an account on GitHub.

- 12_components_low_res.png (2317×1330)

- Versatile, Compact and High-Performance TySOM-M Embedded Development Board Based on PolarFire® SoC FPGA Device | Microchip Technologies - RISC-V International

Learn more about Aldec's high-performance and versatile FPGA development platform. Versatile, Compact and High-Performance TySOM-M Embedded Development Board Based on PolarFire® SoC FPGA Device

- Get Your Code Future-Ready with FREE Technical Webinars

Sign up today to attend LIVE SESSIONS covering the latest overviews, insights, and how-to’s on topics that drive our cross-architecture, heterogeneous-compute world—oneAPI, AI, HPC, rendering & ray tracing, video & media, IoT, and more.

- VHDL When-Else / With-Select Yapıları – QoreHub

VHDL tasarımları içerisinde, koşula bağlı bir çıktı istediğimiz zaman ilk başvurulabilecek opsiyonlar if-else, when-else ya da with-select yapılarıdır. Örneğin tasarımınızda bir sayaç (counter) bulunuyor ve bu sayacın süresini bir koşula bağlı olup değişken olmasını istiyorsunuz. Bu ...

- Dragon Li's Bajiu Lite Is a Flexible FPGA Development Board with RISC-V SoC Capabilities - Hackster.io

Using the VexRiscv CRiscV soft- core, users can tailor the device for workloads ranging from computer vision to robotics.

- Home - Embedded Systems Week

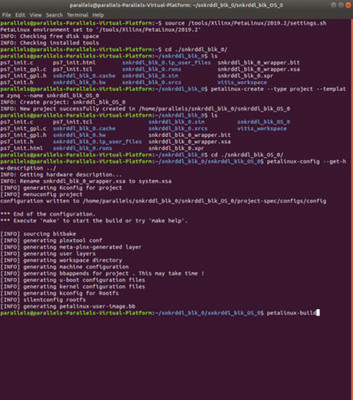

- Rapid Silicon : Raptor Deep Dive

A few weeks ago, we looked at took a high-level view of the open-source tools which are combined to create the Rapid Silicon Raptor tool chain. In this blog we are going to look through the tool and examine the basic flow. For this blog I will be using an early very early release running on an ubuntu virtual machine, while we can script the follow, I will show the GUI approach in FOEDAG. The application is small being less than 1.5 GB including the Litex IP library, once installed we can start t

- First RISC-V processor starts operation in orbit - eeNews Europe

The first RISC-V processor in space developed by CAES is operating in the Trisat-R nanosat developed by the University of Maribor in Slovenia

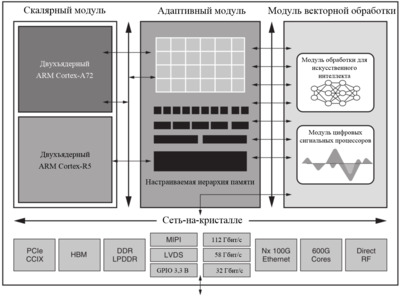

- AMD представила DPU-платформу 400G Adaptive Exotic SmartNIC / ServerNews

На конференция Hot Chips 34 AMD представила новую платформу 400G Adaptive Exotic SmartNIC. В самой концепции формально нет ничего нового, поскольку DPU уже снискали популярность в среде гиперскейлеров, но вариант AMD сочетает достоинства не двух, а трёх миров: классического ASIC, программируемой логики на базе FPGA и Arm-процессора общего назначения.

- Navigating the Transition to Versal ACAP - eeNews Europe

The aerospace and defense industry is taking a technological leap with the Xilinx® Versal® Adaptive Compute Acceleration Platform (ACAP).

- Robust BLDC Motor Control with the TI DRV10866 — Tremaine Consulting Group

Control loop analysis of a brushless senorless DC motor using a TI DRV10964 driver chip, including an FPGA digital speed control loop.

- Getting started with Nios V and Ashling RiscFree IDE for Intel FPGAs | Adiuvo Engineering and Training, Ltd.

NIOS-V is the RISC-V Implementation for Intel FPGAs replacing the extremely popular NIOS-2.In this workshop we are going to not only take a look at the NIOS-V but also examine the development tools...

- The Cost-Optimized, Small yet Mighty Zynq UltraScale+ ZU1 MPSoC for Edge Applications

- AnDAPT adds PMICs for Xilinx UltraScale+ FPGAs: embedded

AnDAPT releases custom power delivery products for AMD-Xilinx Zynq UltraScale+ and Xilinx Artix UltraScale+ FPGA and adaptive SoC families.

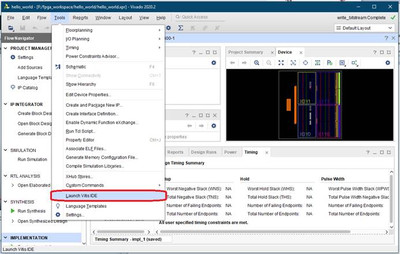

- Vitis – Huge Debugging Varieties - WEBINAR

- FPGA Design Fundas 0.2: The Need For Simulation Verification & Integration Testing – Tech Blog

- Faraday FPGA-Go-ASIC™ Service | LinkedIn

- Periodic Table of Embedded Systems: 118 Interactive Tech Terms

Glossary: discover key technologies and tools used in Embedded Systems Engineering with our Interactive Periodic Table of Tech Terms

- Tasarım Mimarlık ve Mühendislik Dergisi » Makale » FPGA BASED RECONFIGURABLE IMPLEMENTATIONS OF SPIKING NEURAL NETWORKS: A MINI REVIEW

- ADM-VPX3-9Z5 | Alpha Data

- JLPEA | Free Full-Text | FPGA Implementation of Mutual Authentication Protocol for Medication Security System

Medication safety administration is a complicated process involving the information of patients, drugs, and data storage. The sensitive data transmitted through wireless sensor networks (WSNs) from Internet of things (IoT) over an insecure channel is vulnerable to several threats and needs proper attention to be secured from adversaries. Taking medication safety into consideration, this paper presents a secure authentication protocol for wireless medical sensor networks. The XOR scheme-based algorithm is applied to achieve the purposes of data confidentiality. The proposed architecture is realized as hardware in a field-programmable gate array (FPGA) device which acts as a secure edge computing device. The performance of the proposed protocol is evaluated and simulated via Verilog hardware description language. The functionality of the proposed protocol is verified using the Altera Quartus II software tool and implemented in the Altera Cyclone II DE2-70 FPGA development module. Furthermore, the output signals from the FPGA are measured in the 16702A logic analyzer system to demonstrate real-time functional verification.

- A faster prototyping device-under-test connection - SemiWiki

When discussing FPGA-based prototyping, we often focus on how to pour IP from a formative SoC design into one or more FPGAs so it can be explored and verified before heading off to a foundry where design mistakes get expensive. There's also the software development use case, jumpstarting coding for the SoC before silicon arrives.…