Статьи из категории: Общее

Категория:Общее

Сага о светодиодах

Начало пути. Представлены материалы исследования поведения языка Verilog при моделировании простых схем, а также небольшие отступления в стандарт языка Verilog.

4099

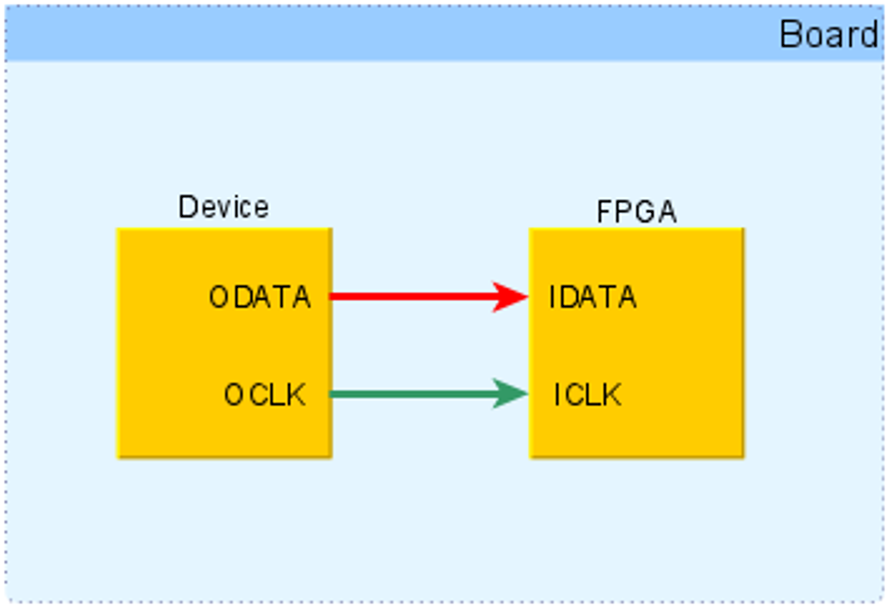

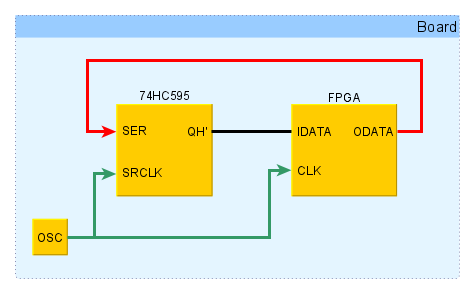

Основы статического временного анализа. Часть 3: Source Synchronous Input Delay Constraint.

В статье представлен временной анализ передачи сигналов в FPGA из внешнего устройства. Рассмотрены теоретические основы анализа для трех различных вариантов выравнивания данных относительно тактового сигнала. Также разобраны два практических примера создания временных ограничений.

6915

1

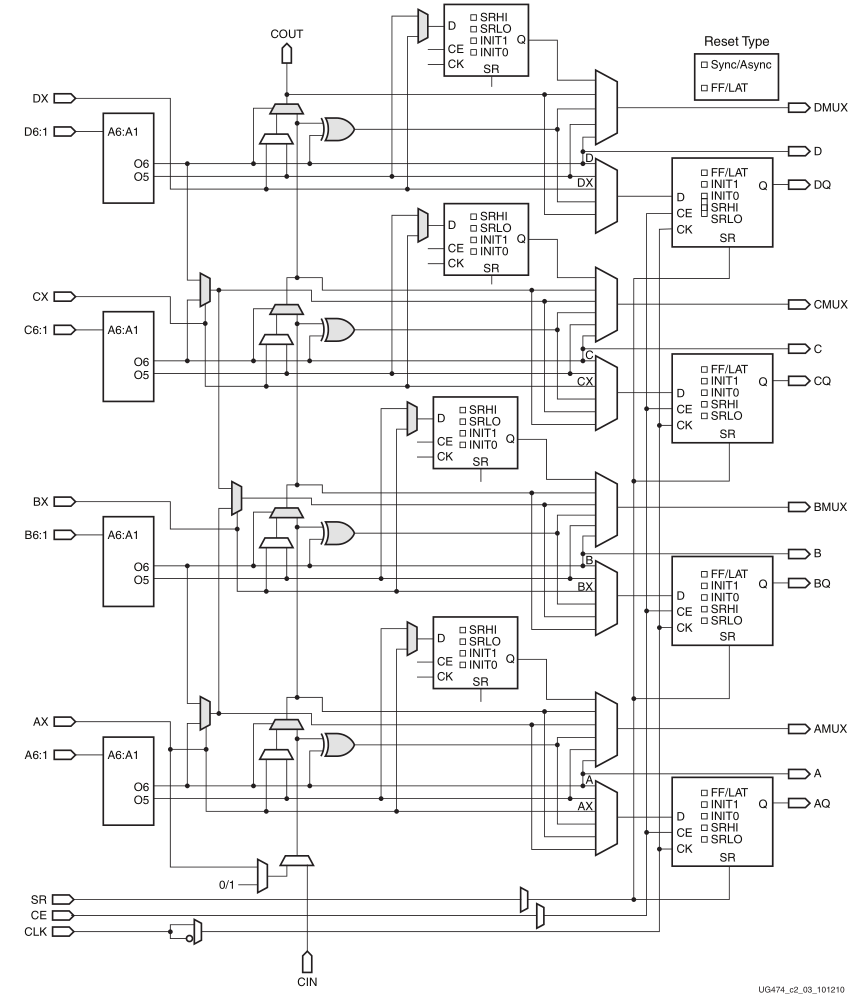

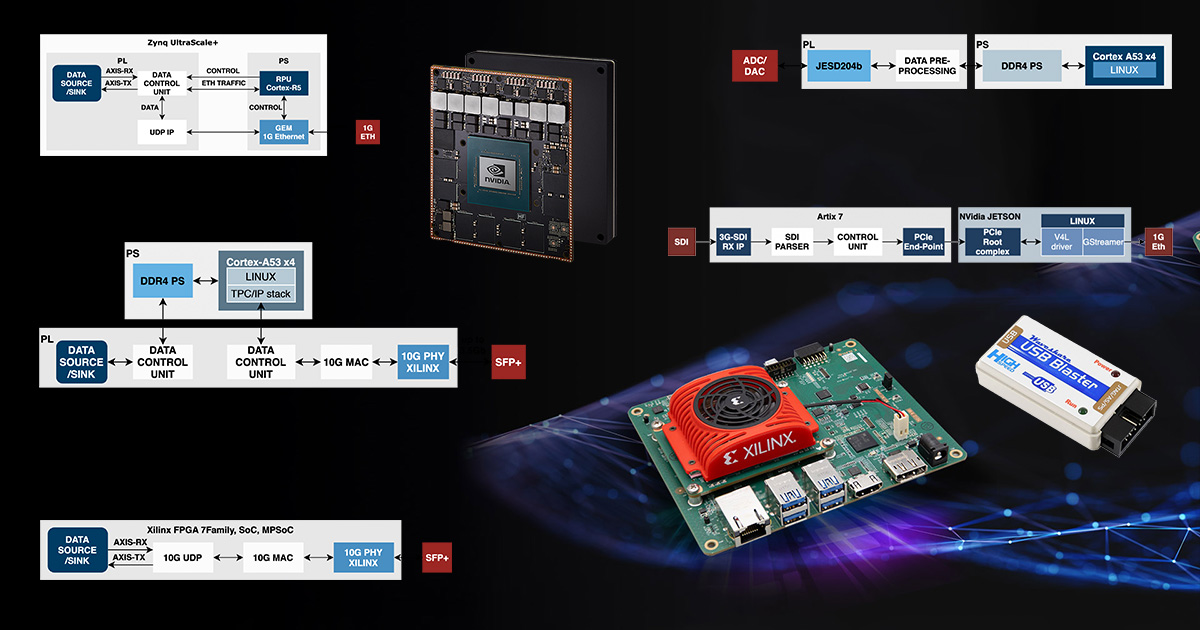

Что внутри ПЛИС или то, о чем не говорят в обучающих видео

LUT-Привет!

Часто в роликах на ютубе или в различных статьях о том «Что же такое ПЛИС?» приводят одну и ту же концепцию ее построения, то есть ПЛИС изображают как набор конфигурируемых логических блоков, соединенных между собой матрицей соединений или интерконнектами.

С одной стороны, это верно, именно так и устроены самые простые представители программируемых логических микросхем, но сегодня ПЛИС – это нечто более сложное и в рамках этой статьи мы разберемся из чего же на самом деле состоят современные FPGA.

10934

0

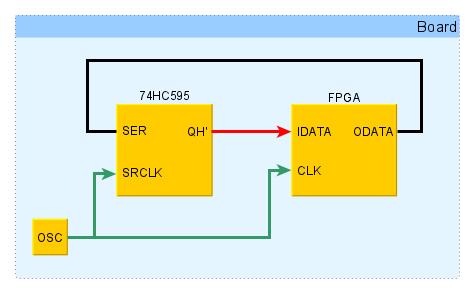

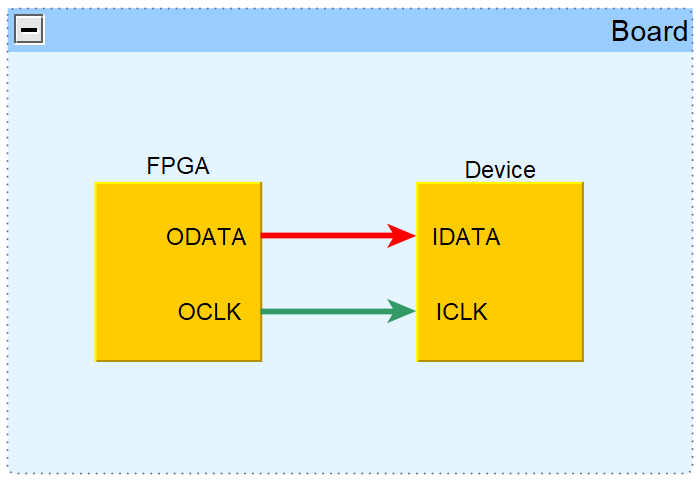

Основы статического временного анализа. Часть 2.2: System Synchronous Output Delay Constraint.

Статья является продолжением серии статей по временным ограничениям в FPGA. Главная цель – познакомить начинающих разработчиков с основами статического временного анализа. Далее будет рассмотрен анализ передачи данных из FPGA во внешнее устройство и показано два способа создания ограничений для выходных сигналов.

7207

6

Основы статического временного анализа. Часть 2.1: System Synchronous Input Delay Constraint.

Статья является продолжением серии статей по временным ограничениям в FPGA. Главная цель – познакомить начинающих разработчиков с основами статического временного анализа. Далее будет рассмотрен анализ передачи данных в FPGA из внешнего устройства и показаны два способа создания ограничений для входных сигналов.

8558

12

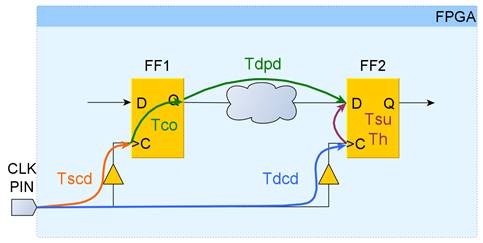

Основы статического временного анализа. Часть 1: Period Constraint.

Статья является первой из планируемой серии статей по временным ограничениям в FPGA. Основная цель – познакомить начинающих разработчиков с основами статического временного анализа. В этой статье будет рассмотрен анализ самого простого случая – передача данных между двумя последовательными элементами внутри FPGA с общим тактовым сигналом. Показан вывод уравнений временного анализа и продемонстрировано их применение анализатором Vivado.

20149

8

Искусство отладки FPGA: как сократить срок тестирования за счет грамотной разработки

Статья о полезных инструментах и типичных ошибках при отладке прошивки для FPGA. Основана на реальных событиях, а точнее — на опыте разработок для FPGA Xilinx, Lattice и Microchip. Внутри вас ждет принцип 20/80 для планирования времени, правило жизни У. Черчилля и полезные практические советы.

4621

0

0