Основы статического временного анализа. Часть 2.2: System Synchronous Output Delay Constraint.

Оглавление

- Введение

- 1. Цель временных ограничений для выходных сигналов

- 2. Задержки при временном анализе для выходных сигналов

- 3. Максимальное время распространения

- 4. Минимальное время распространения

- 5. Первый способ создания временных ограничений в Vivado

- 6. Второй способ создания временных ограничений в Vivado

- Заключение

- Ссылки

*О найденных опечатках и замечаниях просим сообщить admin@fpga-systems.ru

Статья доступна в формате PDF

Введение

Данная статья является продолжением серии статей по временным ограничениям в FPGA. Главная цель – познакомить начинающих разработчиков с основами статического временного анализа. Далее будет рассмотрен анализ передачи данных из FPGA во внешнее устройство и показано два способа создания ограничений для выходных сигналов.

1. Цель временных ограничений для выходных сигналов

В цифровых синхронных устройствах данные передаются между двумя триггерами, которые разделены комбинационной логикой. Ранее в [1] был представлен временной анализ для входных сигналов. В данной статье будут рассмотрены ограничения для выходных сигналов. Часть параграфов будут совпадать с материалом, представленным в [1]. Это сделано намеренно чтобы данные работы можно было читать независимо друг от друга.

Обычно обрабатываемые данные пересылаются между FPGA и другими микросхемами, расположенными на той же печатной плате. Эти пути передачи должны удовлетворять ограничениям по Setup и Hold, чтобы плата как единое целое могла работать корректно. Поэтому практически всегда для выходных сигналов FPGA требуется вводить временные ограничения.

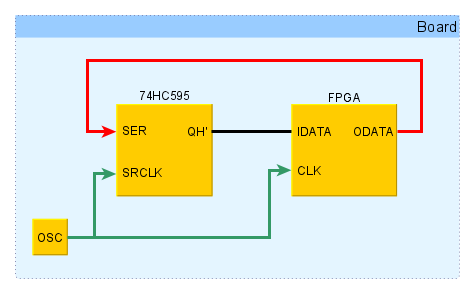

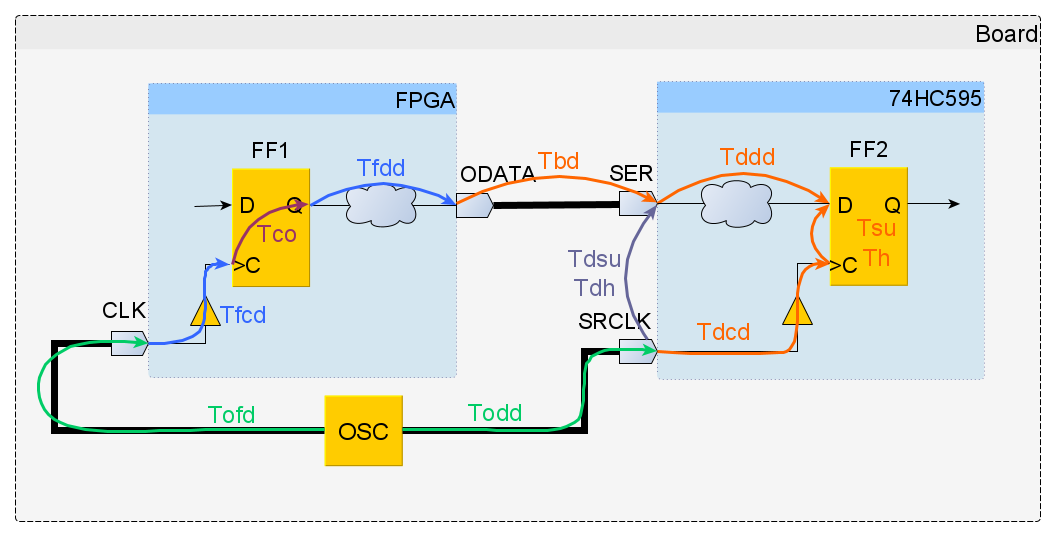

В качестве примера будем рассматривать устройство, схема которого показана на рисунке 1. Помимо FPGA на плате присутствует микросхема 74HC595 [3], которая представляет из себя обычный регистр сдвига и часто поставляется в составе обучающих наборов для Arduino. Также на плате располагается генератор (OSC), формирующий тактовый сигнал для FPGA и 74HC595.

Данная конфигурация, при которой тактовый сигнал для источника и приемника данных поступает от внешнего генератора, называется System Synchronous. Другой вариант, когда источник помимо данных также формирует тактовый сигнал, называется Source Synchronous.

На рисунке 1 отмечены только те ножки микросхемы 74HC595, которые будут рассматриваться в дальнейшем. Ножка SER соответствует входу регистра сдвига, ножка QH’ – его выходу. Регистр сдвига тактируется сигналом, который поступает на ножку SRCLK. В дальнейшем микросхему 74HC595 для краткости будем иногда называть Device. Далее будет представлен временной анализ передачи данных с выхода ODATA FPGA на вход SER 74HC595. На рисунке 1 данный путь отмечен красным цветом.

Рисунок 1. Схема соединения устройств на плате.

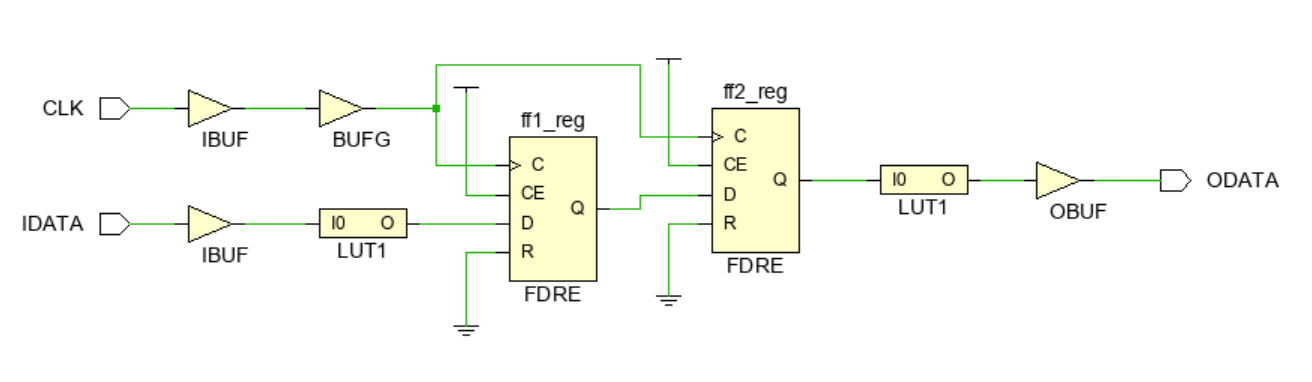

Также пусть в FPGA загружен простой проект, состоящий из двух триггеров и двух LUT, которые реализуют логическое отрицание. Схема проекта показана на рисунке 2.

Рисунок 2. Схема FPGA проекта.

Описание проекта на System Verilog представлено ниже:

|

Данный проект не имеет какой-либо практической ценности, однако на его примере можно продемонстрировать, как проводится временной анализ для выходных сигналов.

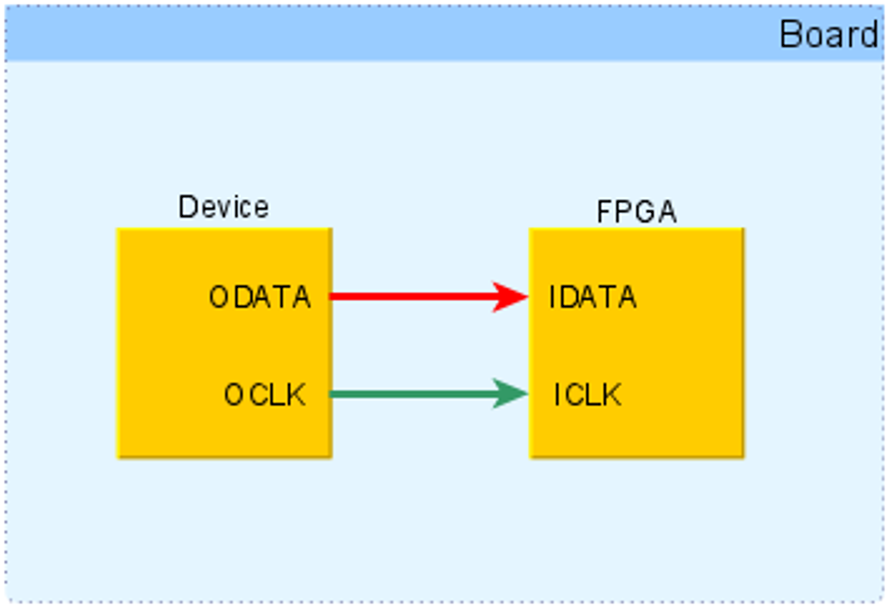

2. Задержки при временном анализе для выходных сигналов

Анализ передачи данных между FPGA и Device мало отличается от случая, рассмотренного в [2] для двух триггеров внутри FPGA. Особенностью является то, что запускающий триггер располагается в одном устройстве, а защелкивающий в другом. На рисунке 3 показан анализируемый путь, на который нанесены задержки для данных и тактового сигнала.

Рисунок 3. Путь с задержками для выходных данных и тактового сигнала.

Ниже даны определения задержек, представленных на рисунке 3.

• Todd (Osc to Device Delay) – задержка тактового сигнала от генератора до ножки SRCLK микросхемы 74HC595;

• Tofd (Osc to FPGA Delay) – задержка тактового сигнала от генератора до ножки CLK FPGA;

• Tdcd (Device Clock Delay) – задержка тактового сигнала от ножки SRCLK микросхемы 74HC595 до тактового входа защелкивающего триггера;

• Tbd (Board Delay) – задержка распространения данных по дорожкам платы между FPGA и микросхемой 74HC595;

• Tddd (Device Data Delay) – задержка распространения данных от ножки SER микросхемы 74HC595 до защелкивающего триггера;

• Tsu (SetUp time) – время установки защелкивающего триггера;

• Th (Hold time) – время удержания защелкивающего триггера;

• Tfcd (FPGA Clock Delay) – задержка тактового сигнала от ножки CLK FPGA до тактового входа запускающего триггера;

• Tfdd (FPGA Data Delay) – задержка распространения данных от запускающего триггера до ножки ODATA FPGA;

• Tco (Clock to Output) – интервал времени между приходом фронта на тактовый вход триггера и появлением данных на его выходе Q.

Период тактового сигнала будем обозначать Tclk. Оранжевым и зеленым цветом на рисунке 3 представлены задержки для участков пути, которые располагаются вне FPGA. Данные задержки необходимо указать временному анализатору Vivado.

3. Максимальное время распространения

Для начала рассмотрим, каким образом выполняется анализ для проверки ограничения на максимальное время распространения (Setup). Напомним, что временной анализ по Setup всегда проводится для самого пессимистичного случая, которому соответствует максимально задержанный запускающий фронт, максимально медленное распространение данных и максимально быстро распространяющийся защелкивающий фронт.

Сначала найдем фактическое время прибытия данных ко входу защелкивающего триггера, расположенного внутри микросхемы 74HC595. Будем считать, что запускающий фронт появляется в нулевой момент времени. Уравнения для расчета представлены ниже (см. рисунок 3):

• Время прибытия фронта к запускающему триггеру (Source Сlock Arrival time):

• Задержка распространения данных (Data Delay):

• Время прибытия данных на вход защелкивающего триггера внутри микросхемы 74HC595 (Data Arrival time):

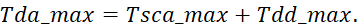

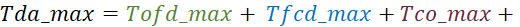

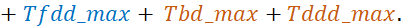

Подставив предыдущие результаты в уравнение для Tda_max, получим:

Теперь вычислим требуемое время прибытия данных. Защелкивающий фронт появляется через один такт после запускающего, поэтому ко времени прибытия фронта добавлен один период тактового сигнала.

• Время прибытия фронта к защелкивающему триггеру внутри микросхемы 74HC595 (Destination Clock Arrival time):

• Требуемое время прибытия данных (Data Required time):

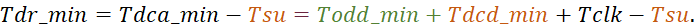

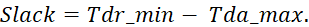

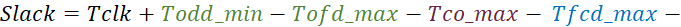

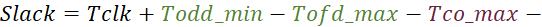

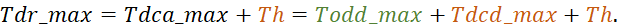

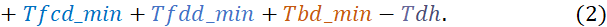

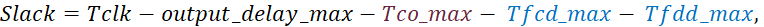

В предыдущем уравнении учитывается, что данные на входе защелкивающего триггера должны быть стабильны в течении времени установки Tsu до прихода фронта тактового сигнала. При анализе по Setup величина запаса (Slack) вычисляется по формуле:

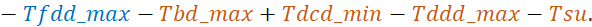

Если Slack принимает отрицательное значение, то это указывает, что данные приходят на вход защелкивающего триггера позже, чем требуется. То есть, ограничение по Setup нарушено. Используя полученные ранее уравнения, можно записать полное выражение для расчета Slack:

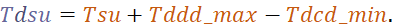

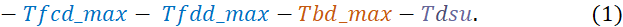

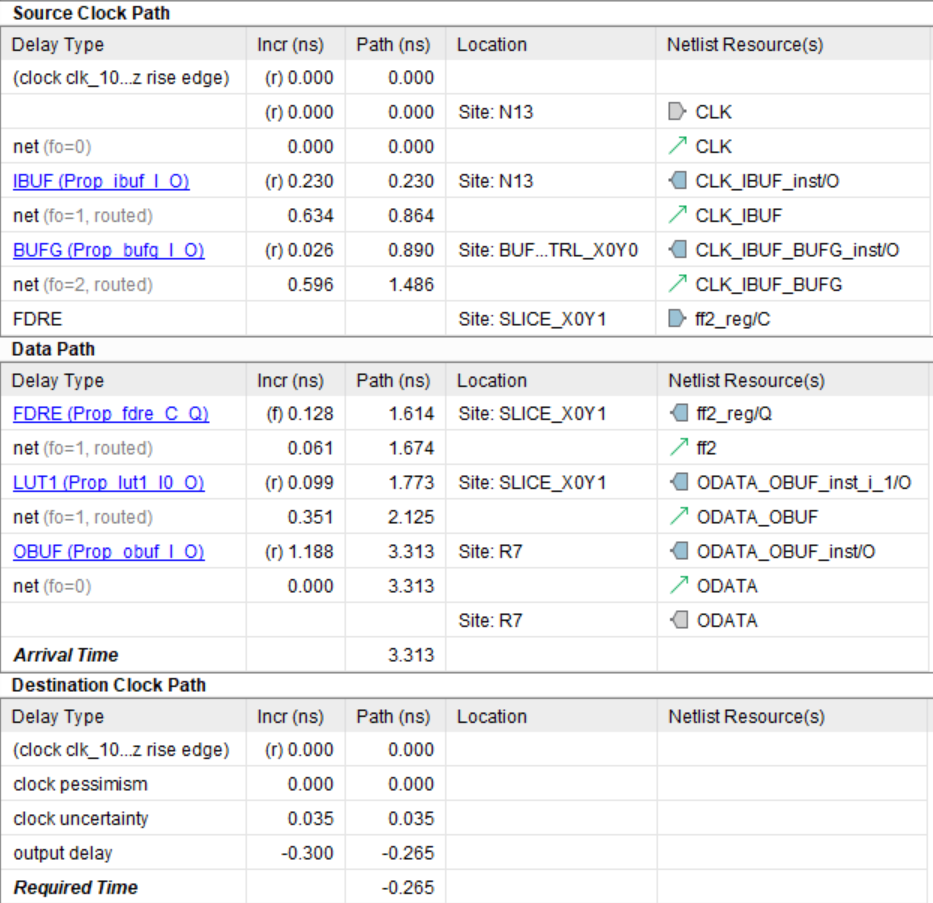

Введем обозначение Tdsu (Device SetUp time):

Задержка Tdsu соответствует времени установки для сигнала на входе SER микросхемы 75HC595 относительно ее тактового входа SRCLK. Тогда уравнение для Slack можно записать в виде:

4. Минимальное время распространения

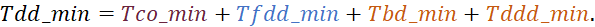

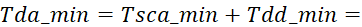

Теперь рассмотрим, как выполняется анализ для проверки ограничения на минимальное время распространения (Hold). При анализе по Hold считается, что задержки для запускающего фронта и данных имеют минимальное значение, а для защелкивающего фронта – максимальное. Расчет фактического времени прибытия данных представлен ниже:

• Время прибытия фронта к запускающему триггеру (Source Сlock Arrival time):

• Задержка распространения данных (Data Delay):

• Время прибытия данных на вход защелкивающего триггера внутри микросхемы 75HC595 (Data Arrival time):

Далее представлены уравнения для вычисления требуемого времени прибытия данных:

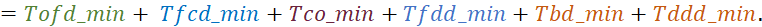

• Время прибытия фронта к защелкивающему триггеру внутри микросхемы 75HC595 (Destination Clock Arrival time):

• Требуемое время прибытия данных (Data Required time):

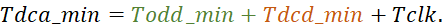

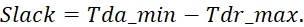

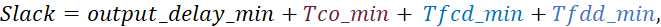

Защелкивающий фронт для предыдущих данных появляется в тот же момент времени, что и запускающий фронт для следующих данных. По этой причине в задержке распространения Tdca_max отсутствует слагаемое, равное периоду тактового сигнала. Уравнение для расчета Slack при анализе по Hold имеет вид:

Введем обозначение Tdh (Device Hold time):

Задержка Tdh соответствует времени удержания для сигнала на входе SER микросхемы 75HC595 относительно ее тактового входа SRCLK. То есть, данные на входе SER не должны изменяться в течении времени Tdh после защелкивающего фронта на входе SRCLK. Используя полученные выше результаты, выражение для Slack можно представить в виде:

5. Первый способ создания временных ограничений в Vivado

Перейдем от теории к практике и рассмотрим первый способ создания временных ограничений для выходных сигналов. Для начала разберемся с ограничениями для анализа по Setup.

В уравнении (1) слагаемые, выделенные зеленым и оранжевым цветом, неизвестны анализатору Vivado, так как они описывают задержки для участков пути вне FPGA. Также неизвестным является значение периода Tclk. Создание ограничений на период тактового сигнала с помощью команды create_clock было рассмотрено в [2].

Для определенности будем считать, что напряжение источника питания микросхемы 74HC595 равно 4.5 В. Из таблицы 6.6 datasheet для 74HC595 [3] находим, что в этом случае максимальная рабочая частота равна 31 МГц. Пусть требуется, чтобы плата на рисунке 1 могла работать при частоте тактового генератора (OSC) равной 10 МГц. Тогда ограничение на период тактового сигнала можно записать в виде:

|

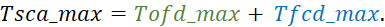

Данная команда объявляет тактовый сигнал clk_10MHz с периодом 100 нс, который поступает в FPGA через ножку CLK. Объединим все оставшиеся неизвестные слагаемые из уравнения (1) в одну переменную output_delay_max. Тогда выражение для Slack можно переписать в виде:

где

В уравнении (3) слагаемые Todd_max, Tofd_min и Tbd_max описывают задержки, обусловленные распространением сигнала по дорожкам печатной платы. Их значения зависят от многих факторов, например, материала подложки, длины дорожек, типа дорожек (полосковые, микрополосковые и т.д.).

Для каждого типа дорожек существуют приближенные выражения для вычисления скорости распространения сигнала. Зная скорость сигнала и длину дорожки, можно оценить задержку распространения. Примеры приближенных расчетов для различных типов дорожек можно найти в [4].

Будем считать, что мы смогли оценить минимальные и максимальные задержки распространения сигналов по дорожкам печатной платы. В качестве примера примем следующие значения в наносекундах: Tbd_max = 0.6, Tbd_min = 0.5, Todd_max = 0.4, Todd_min = 0.2, Tofd_max = 0.3 и Tofd_min = 0.2. Значения задержек можно указать в файле с временными ограничениями (xdc-файл) в следующем виде:

|

Рассмотрим задержку Tdsu из уравнения (3), которая соответствует времени установки для сигнала на входе SER микросхемы 75HC595 относительно тактового входа SRCLK. Ее значение можно получить из таблицы 7.6 datasheet для 74HC595 [3]. Данная задержка обозначена как tsu и при напряжении питания 4.5 В равна 20 нс. Это значение также записывается в xdc-файл:

|

Теперь можно создать временное ограничение на выходной сигнал для анализа по Setup. Для этого в файл с ограничениями нужно внести следующие команды [5]:

|

В первой строке объявлена переменная odelay_max, значение которой приравнивается output_delay_max из уравнения (3). Далее с помощью команды set_output_delay создается ограничение для выходного сигнала. Опция -max $odelay_max задает задержку для анализа по Setup. Конструкция [get_ports ODATA] указывает, что ограничение накладывается на выходной сигнал, выдаваемый из FPGA через ножку ODATA.

Важно отметить, что анализатору Vivado необходимо указать, каким сигналом тактируется защелкивающий триггер, так как он находится вне FPGA. Это делается с помощью опции -clock clk_10MHz. Данный тактовый сигнал был создан ранее с помощью команды create_clock. Запускающий триггер располагается внутри FPGA, поэтому временному анализатору его тактовый сигнал известен.

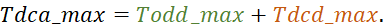

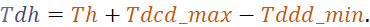

Аналогичным образом создаются ограничения для анализа по Hold. Объединив все неизвестные слагаемые в уравнении (2) в одну переменную, выражение для Slack можно записать в виде:

где

Значение задержки Tdh можно получить из таблицы 7.6 datasheet для 74HC595 [3]. Данная задержка обозначена как th и равна 0 нс. Ее также следует записать в xdc-файл:

|

Команды, создающие временное ограничение, представлены ниже:

|

Как и ранее, сначала объявляется переменная, значение которой равно output_delay_min, после чего с помощью команды set_output_delay создается временное ограничение. Опция –min указывает, что ограничение предназначено для проведения анализа по Hold. Полное содержимое xdc-файла представлено ниже:

|

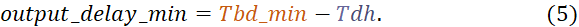

Рассмотрим, как введенные ограничения будут отражены во временных отчетах, полученных после размещения и трассировки проекта. На рисунке 4 представлен раздел Summary для анализа по Setup, в котором указан запускающий триггер (ff2_reg), выходной порт FPGA (ножка ODATA), задержка данных внутри FPGA (Data Path Delay) и количество уровней логики (Logic Levels). Также можно увидеть полученный Slack, расфазировку (Clock Path Skew) и неопределенность (Clock Uncertainty) тактового сигнала.

Рисунок 4. Общие сведения о выходном пути (Setup).

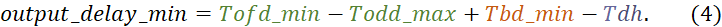

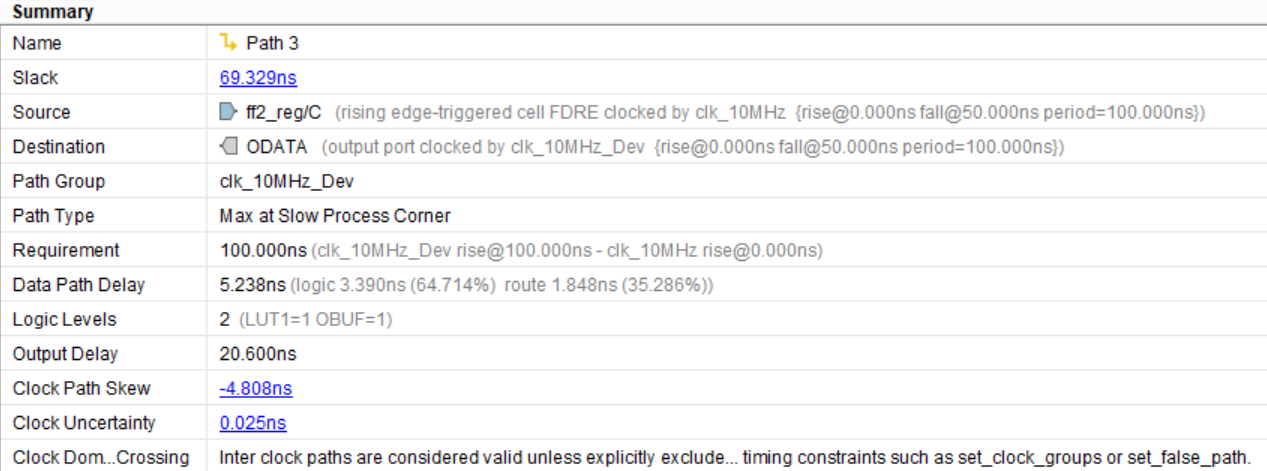

На рисунке 5 показаны задержки для запускающего фронта, защелкивающего фронта и данных. Представленные результаты можно интерпретировать следующим образом. Из раздела Source Clock Path получаем, что запускающий фронт приходит на ножку CLK FPGA в нулевой момент времени. Далее через входной и тактовый буферы он попадает на вход триггера и через 4.708 нс запускает передачу данных. В свою очередь данные проходят через LUT1 и выходной буфер и появляются на выходной ножке ODATA в момент времени 9.946 нс. Эта задержка показана на рисунке 5 в разделе Data Path.

Из раздела Destination Clock Path видно, что спустя один период тактового сигнала, равный 100 нс, защелкивающий фронт попадает на вход триггера внутри микросхемы 74HC595. Время распространения данных вне FPGA учитывается c помощью задержки output delay. Ее значение вычисляется по формуле (3) и равно 0.3 - 0.2 + 0.6 + 20 = 20.7 нс.

Таким образом, с учетом неопределенности тактового сигнала в 0.035 нс данные должны дойти до ножки ODATA в момент времени 100 - 20.7 - 0.035 = 79.265 нс. Отсюда получаем, что Slack равен 79.265 - 9.946 = 69.319 нс, что соответствует значению, представленному на рисунке 4.

Рисунок 5. Задержки тактового сигнала и данных (Setup).

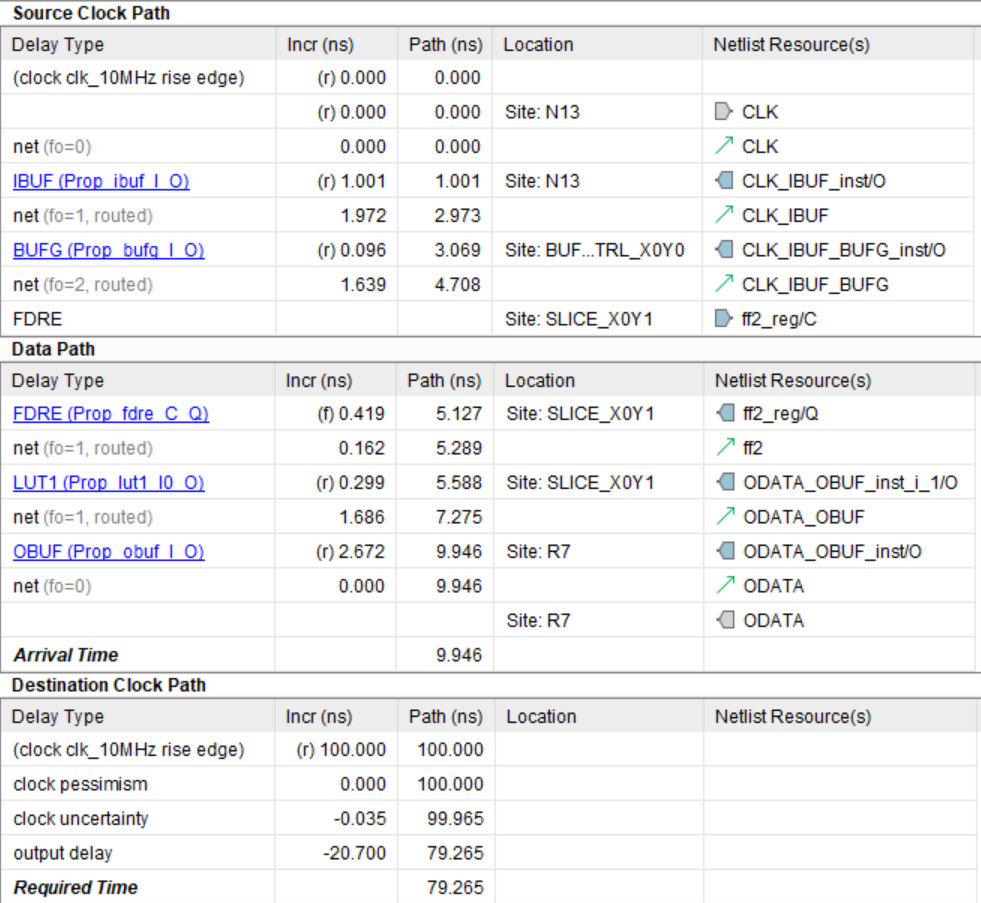

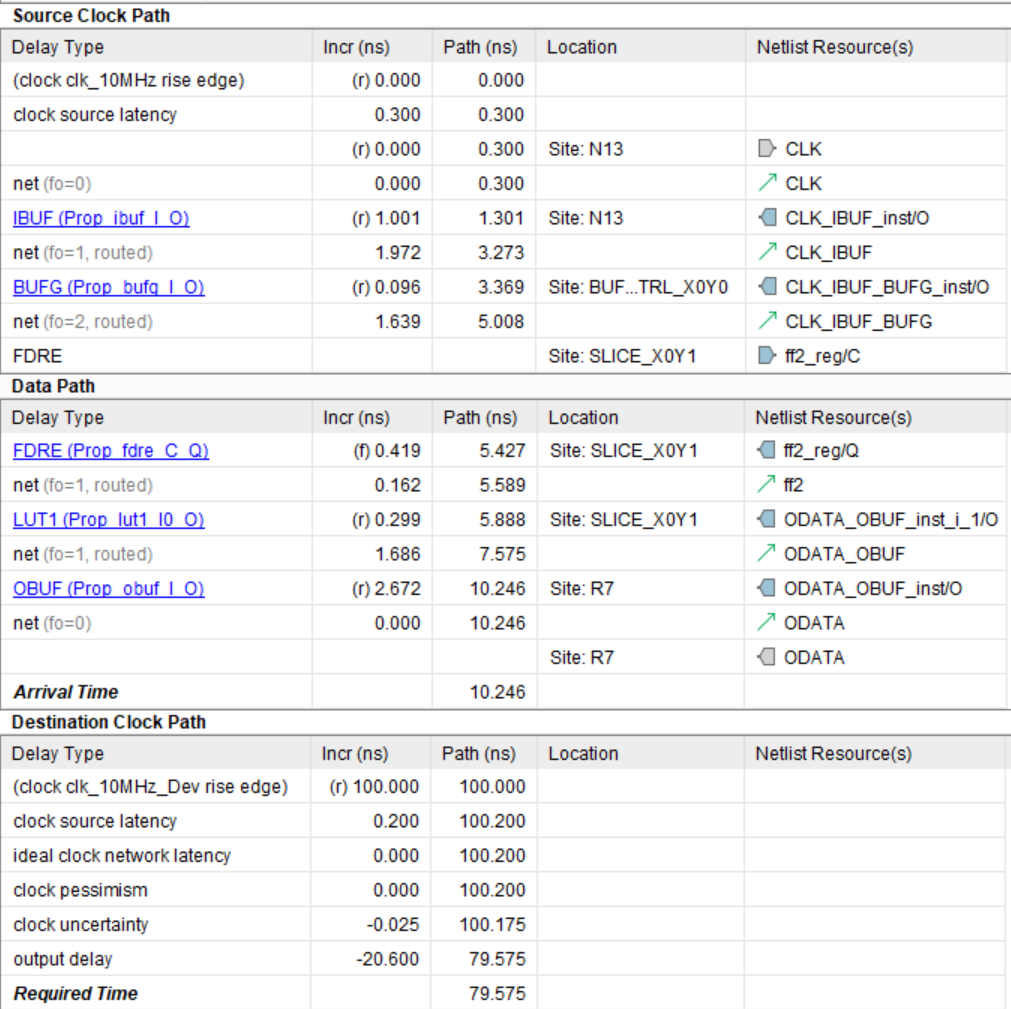

Ту же картину получаем для анализа по Hold. На рисунке 6 можно увидеть, что запускающий фронт достигает FPGA в нулевой момент времени, после чего спустя 3.313 нс на ножке ODATA появляются данные. Для анализа по Hold запускающий и защелкивающий фронты формируются одновременно, поэтому на вход SRCLK микросхемы 74HC595 фронт приходит также в нулевой в момент времени.

Значение задержки output delay вычисляется по формуле (4) и равно 0.2 - 0.4 + 0.5 - 0 = 0.3 нс. Учитывая неопределенность тактового сигнала получаем, что данные должны появится на ножке ODATA в момент времени -0.265 нс. Отрицательное значение Required Time означает, что данные должны появится на выходе ODATA FPGA раньше, чем генератор сформирует защелкивающий фронт.

Рисунках 6. Задержки тактового сигнала и данных (Hold).

Данный подход прост тем, что достаточно представить все неизвестные задержки в виде одной величины output_delay. Объединение всех задержек в одну переменную имеет и негативный эффект, который заключается в отсутствии точного соответствия между временными отчетами и реальными задержками на плате. Например, считается, что фронты тактового сигнала доходят до запускающего триггера в нулевой момент времени.

6. Второй способ создания временных ограничений в Vivado

Рассмотрим второй способ создания временных ограничений для выходных сигналов. С помощью команды set_clock_latency [5] можно отдельно указывать время распространения тактового сигнала по дорожкам печатной платы. Ниже представлены команды для создания задержки распространения между генератором и FPGA:

|

C помощью команды create_clock создается ограничение на период тактового сигнала, который поступает на ножку CLK FPGA. Далее первая команда set_clock_latency с опцией –early устанавливает минимальную задержку распространения равной Tofd_min. Конструкция [get_clocks clk_10MHz] указывает тактовый сигнал, для которого формируются задержки.

Вторая команда set_clock_latency с опцией –late задает максимальное время распространения. Опция -source означает, что задержка указывается от источника тактового сигнала до ножки FPGA. Так как задержка распространения до микросхемы 74HC595 отличается от задержки до FPGA, в файле с временными ограничениями требуется создать еще один тактовый сигнал:

|

С помощью команды create_clock создается тактовый сигнал с именем clk_10MHz_Dev и периодом 100 нс. Обратите внимание, что этот сигнал поступает только в микросхему 74HC595, поэтому команда get_ports, указывающая ножку FPGA, не используется. Тактовый сигнал, который не попадает в FPGA, но присутствует на плате, называется виртуальным (virtual clock). Для виртуального сигнала clk_10MHz_Dev минимальная и максимальная задержки распространения заданы равными Todd_min и Todd_max соответственно.

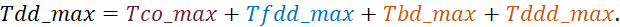

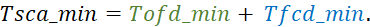

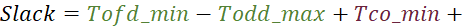

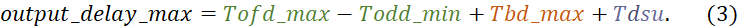

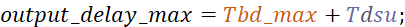

Так как задержки для тактового сигнала уже установлены, уравнения для output_delay_max и output_delay_min упростятся и будут содержать только задержки распространения данных:

Временные ограничения для выходного сигнала создаются с помощью команды set_output_delay в виде:

|

Опция -max указывает, что задержки предназначены для анализа по Setup, а опция -min – для анализа по Hold. Обратите внимание, что теперь защелкивающий триггер, расположенный внутри микросхемы 74HC595, тактируется виртуальным сигналом, поэтому опция –clock задана с сигналом clk_10MHz_Dev. Полное содержимое xdc-файла представлено ниже:

|

Рассмотрим, что изменилось во временных отчетах при использовании данного способа создания ограничений. На рисунке 7 представлены общие сведения о выходном пути для анализа по Setup. В третьей строке указано, что данные для микросхемы 74HC595 появляются на выходе ODATA FPGA и защелкиваются виртуальным сигналом clk_10MHz_Dev.

Рисунок 7. Общие сведения о выходном пути (Setup).

Расчет задержек для данных и тактового сигнала представлен на рисунке 8. В разделе Source Clock Path можно увидеть, что запускающий фронт появляется на выходе генератора в нулевой момент времени и спустя 0.3 нс (clock source latency) достигает тактовой ножки FPGA. Это соответствует задержке Tofd_max. Далее после прохождения через входной и тактовый буферы фронт доходит до запускающего триггера. Это событие начинает передачу данных, которые, как показано в разделе Data Path, появляются на выходе ODATA FPGA в момент времени 10.246 нс.

Рисунок 8. Задержки для данных и тактового сигнала (Setup).

Из раздела Destination Clock Path рисунка 8 можно увидеть, что защелкивающий фронт тактового сигнала появляется на выходе генератора спустя один период в 100 нс и через Todd_min = 0.2 нс достигает микросхемы 74HC595. Слагаемое output delay, равное output_delay_max из уравнения (5), указывает, что данным требуется 20.6 нс, чтобы дойти от выхода FPGA до входа микросхемы 74HC595 и оставаться стабильными в течении времени установки. Поэтому с учетом неопределённости тактового сигнала данные должны появится на ножке ODATA FPGA в момент времени 79.575 нс.

Задержки для анализа по Hold показаны на рисунке 9. Можно увидеть, что запускающий фронт формируется на выходе генератора в нулевой момент времени и через Tofd_min = 0.2 нс доходит до тактовой ножки FPGA. Далее в момент времени 3.513 нс на выходе ODATA появятся данные.

Рисунок 9. Задержки для данных и тактового сигнала (Hold).

Защелкивающий фронт появится на выходе генератора также в нулевой момент времени и дойдет до ножки SRCLK микросхемы 75HC595 через Todd_max = 0.4 нс. Учитывая задержку распространения и неопределенность тактового сигнала, требуемое время появления данных на выходе ODATA FPGA равно -0.075 нс.

Использование виртуальных тактовых сигналов для создания ограничений несколько упрощает интерпретацию временных отчетов. Более того, данный способ рекомендуется Vivado. Если открыть вкладку XDC в Language Templates, то можно найти пример временных ограничений для выходного сигнала:

|

В данном случае значение output_delay для анализа по Setup задается в виде суммы задержек tsu (Tdsu) и trce_dly_max (Tbd_max), а для анализа по Hold – как разность trce_dly_min (Tbd_min) и thd (Tdh). Это полностью соответствует уравнениям (5). Заметим также, что, если пренебречь задержками тактового сигнала Todd и Tofd, то оба рассмотренных выше способа создания ограничений будут эквивалентны.

В заключении отметим следующий интересный момент. Можно увидеть, что значения Slack, представленные на рисунках 4 и 7, отличаются и равны 69.319 нс и 69.329 нс соответственно. Разница в 0.01 нс возникает из-за разной величины неопределенности тактового сигнала. Более подробно о причине такого несоответствия можно прочитать в [1].

Заключение

В данной статье был рассмотрен временной анализ для выходных сигналов FPGA. Показан вывод уравнений статического временного анализа. Представлено два способа создания временных ограничений, а также рассказано о виртуальных тактовых сигналах.

Ссылки

1. Основы статического временного анализа. Часть 2.1: System Synchronous Input Delay Constraint

2. Основы статического временного анализа. Часть 1: Period Constraint

4. How to Calculate Trace Length from Time Delay Value for High-speed Signals

Статья доступна в формате PDF