Статья: IP-блок DPUv3E для акселератора Alveo Accelerator Card

26.01.2020 10:33

1390

0

0.0

На сайте Xilinx Developer опубликована новая статья по DPUv3E.

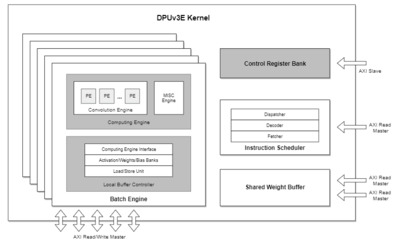

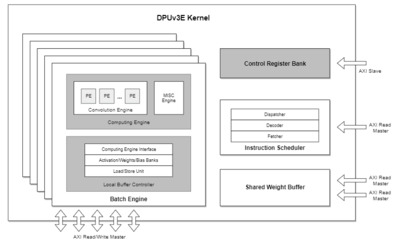

DPUv3E - один из IP-блоков серии DPU фирмы Xilinx для задач, решаемых с помощью свёрточных нейронных сетей (CNN). Блок разработан для новейших ускорителей Alveo U50/U280 с HBM памятью. DPUv3E - высокопроизводительный IP, оптимизированный под высокую пропускную способность и нагрузки ЦОДов. Набор инструкций блока поддерживает большинство современных нейронных сетей - VGG, ResNet, GoogLeNet, YOLO, SSD, MobileNet, FPN и др.

DPUv3E - один из основных блоков среды разработки Xilinx Vitis™ AI. В этой среде разработчик может использовать полный набор инструментов для разработки машинного обучения с этим блоком, а также интегрировать DPUv3E с другими частями ядра акселератора Alveo.

DPUv3E предоставляется в виде зашифрованного RTL или XO файла, который добавляется в среду Vivado или Vitis.

Основные операторы работы с CNN: Читать далее

Читать далее

DPUv3E - один из IP-блоков серии DPU фирмы Xilinx для задач, решаемых с помощью свёрточных нейронных сетей (CNN). Блок разработан для новейших ускорителей Alveo U50/U280 с HBM памятью. DPUv3E - высокопроизводительный IP, оптимизированный под высокую пропускную способность и нагрузки ЦОДов. Набор инструкций блока поддерживает большинство современных нейронных сетей - VGG, ResNet, GoogLeNet, YOLO, SSD, MobileNet, FPN и др.

DPUv3E - один из основных блоков среды разработки Xilinx Vitis™ AI. В этой среде разработчик может использовать полный набор инструментов для разработки машинного обучения с этим блоком, а также интегрировать DPUv3E с другими частями ядра акселератора Alveo.

DPUv3E предоставляется в виде зашифрованного RTL или XO файла, который добавляется в среду Vivado или Vitis.

Основные операторы работы с CNN:

- Convolution / Deconvolution

- Max pooling / Average pooling

- ReLU, ReLU6, and Leaky ReLU

- Concat

- Elementwise-sum

- Dilation

- Reorg

- Fully connected layer

- Batch Normalization

- Split