SPI :: Часть 1:: Общие сведения

Скачать файлы презентации и статью в формате PDF

Здравствуйте друзья. C вами проект FPGA-systems.ru.

Один из подписчиков попросил нас рассказать о разработке интерфейса SPI на ПЛИС. Ну что ж, не оставим его просьбу без ответа.

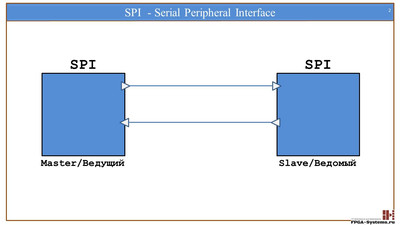

SPI - Serial Peripheral Interface - это последовательный интерфейс обмена данными между несколькими устройствами. Одно из этих устройств является ведущим / master, а другое или другие устройства ведомым / slave.

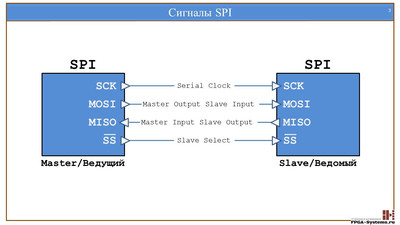

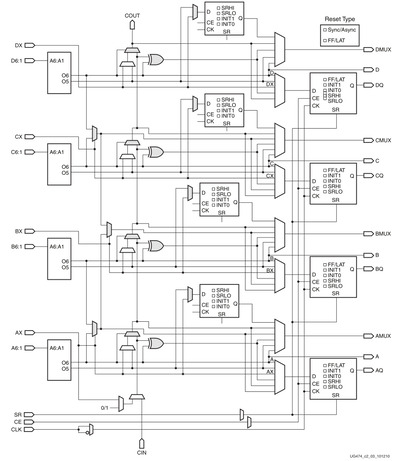

Интерфейс SPI содержит 4 сигнала

- Сигнал SCLK Serial Clock – представляет собой ни что иное как тактовый сигнал, поэтому SPI интерфейс является синхронным

- Сигнал MOSI - Master Output Slave Input – это линия данных, передаваемых от ведущего к ведомому

- Сигнал MISO - Master Input Slave Output – это линия данных, передаваемых от ведомого к ведущему

- Сигнал SS – Slave Select – сигнал выбора ведомого устройства для проведения сеанса обмена данными

Следует отметить, что названия сигналов и их наличие могут отличаться в зависимости от производителя микросхемы, но их функциональное назначение сохраняется. Так например, в документации на АЦП AD7895 мы видим отсутствие сигналов MOSI, а выход ведомого устройства называется SDATA, вместо MISO.

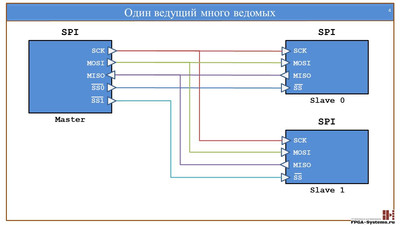

К мастеру с интерфейсом SPI может быть подключено одновременно несколько ведомых устройств. При этом все сигналы, за исключением сигнала Slave Select, являются общими для всех устройств.

Установка сигнала Slave Select в активное состояние позволяет выбрать соответствующее ведомое устройство, к которому обращается мастер.

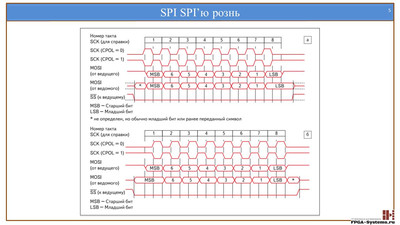

Интерфейс SPI имеет несколько конфигураций, каждая из которых определяется полярностью и фазой тактового сигнала относительно линий данных. Такой подход даёт производителям микросхем определённую гибкость, и они вольны в выборе того, каким образом данные будут обработаны или переданы. Для примера, в одном случае данные могут появляться на линии данных по возрастающему фронту тактового сигнала SCK, а в другом по нисходящему фронту тактового сигнала. Могут также присутствовать и служебные, пустые данные.

О том, как устроен обмен информацией по SPI для конкретной микросхемы, следует смотреть в документации на нее.

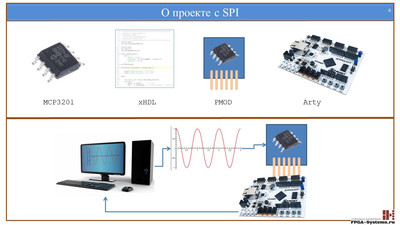

Для того, чтобы немного попрактиковаться в имплементации интерфейса SPI на FPGA мы предлагаем Вам следующий проект, который затронет не только написание кода для FPGA, но и создание своего собственного небольшого и недорого модуля формата PMOD для подключения к платке Arty.

Итак, что мы предлагаем:

- Мы возьмем простенький и недорогой аналогово цифровой преобразователь с интерфейсом SPI. Допустим это будет MCP3201.

- Разработаем на VHDL и Verilog код для считывания данных с АЦП и проведём отладку кода с помощью моделирования.

- В соответствии с рекомендуемой схемой включения из документации на выбранный АЦП, мы разработаем плату, которую подключим к PMOD порту платы Arty.

- Сгенерируем файл для прошивки ПЛИС

- Используя аудиовыход компьютера или ноутбука, сгенерируем синусоиду и подадим ее на вход нашего АЦП

- Считанные с помощью нашего написанного HDL модуля данные с АЦП мы отобразим на экране с помощью интегрированного логического анализатора ILA

Разумеется, проект не претендует на оригинальность, но наш взгляд он достаточно прост и показателен, поскольку мы не ограничимся моделированием написанного модуля, а проверим его работоспособность на практике.

Скачать файлы презентации и статью в формате PDF

Скачать файлы презентации и статью в формате PDF