Новая отладка Xilinx VCU1525 на Virtex UltaScale+

Новый отладочный комплект Xilinx Virtex UltraScale+ FPGA VCU1525

|

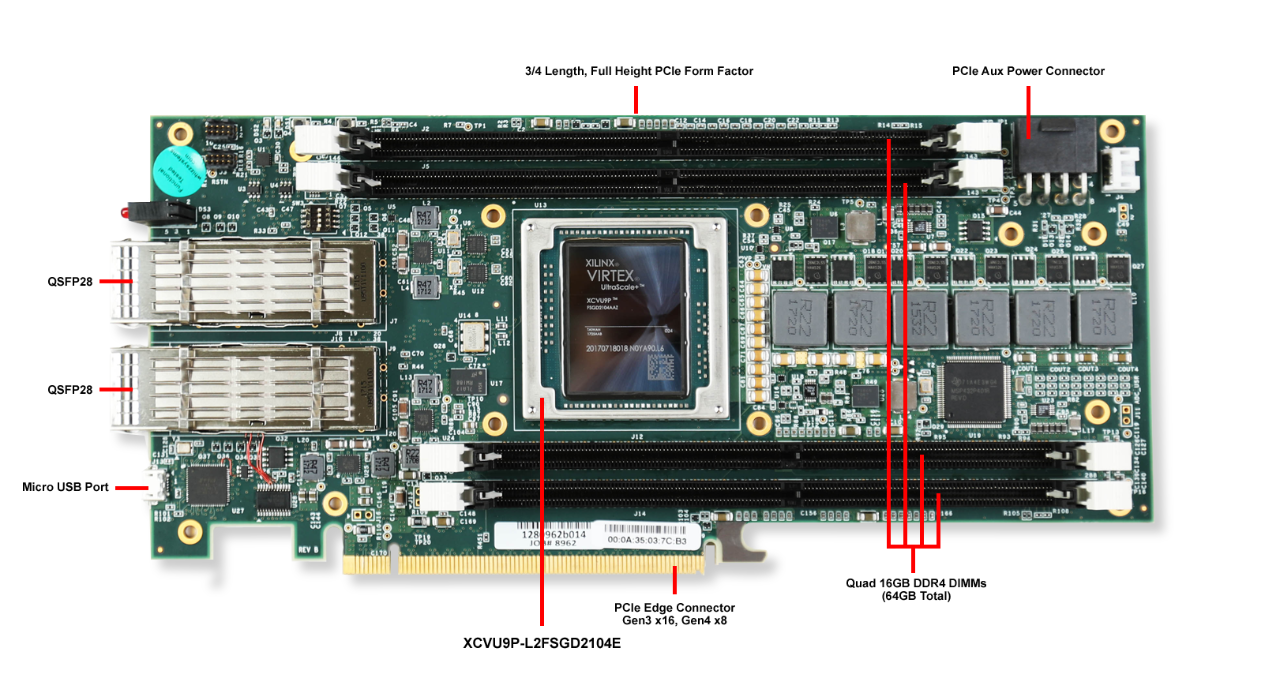

Кодовое название (по типу охлаждения): DK-U1-VCU1525-P-G - пассивное DK-U1-VCU1525-A-G - активное Срок поставки и стоимость: по запросу Семейство: Virtex UltraScale+ |

Описание продукта

Отладочный комплект VCU1525 является идеальным решением для разработчиков приложений для дата центров, дающий возможность использовать все преимущества кристаллов семейства Virtex® UltraScale+™. Отладочный комплекс VCU1525 доступен в облаке и локально с необходимыми фреймворками, библитотеками, драйверами и средствами разработки для программирования на языках OpenCL™, C, C++ и RTL с использованием среды Xilinx SDAccel™ Development Environment. Доступна в двух модификациях: с пассивным охлаждением и активным охлаждением.

Ключевые особенности и преимущества

- Специализированное перепрограммируемое оборудование для вычислительно интенсивных приложений, ориентированное на быстрорастущие рынки для перекодирования видео в реальном времени, анализа данных, геномики и машинного обучения

- Обеспечивает 10-100x ускорение производительности по сравнению с серверными процессорами,

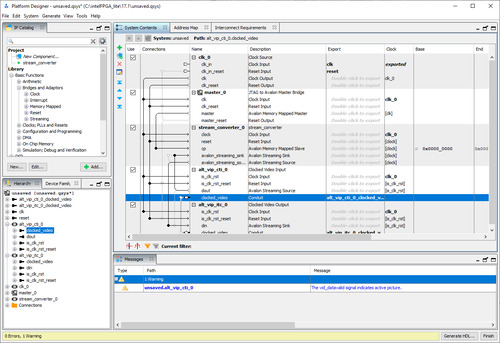

- Тестовый проект описания платформы в SDAccel для поддержки пользовательских плат

- Поддержка SDAccel Development Environment для программирования на OpenCL, C, C++ и RTL

- 346Mb on chip memory

- VU9P Virtex UltraScale+ FPGA

- 64GB DDR4 DIMM памяти установленной на плате

Особенности платы

- 4 - 16GB DDR4 DIMM

Потребляемая мощность и охлаждение

- Доступна версия с активным охлаждением

- Максимальная потребляемая мощность 225Вт

- До 75Вт потребление через PCIe Edge

- Дополнительные 150Вт через PCIe Aux Power Connector

Конфигурация

- Конфигурирование FPGA через JTAG (micro USB порт)

- QSPI конфигурационная флэш

Communication & Networking

- Два QSFP28 100G

- PCIe Gen3 x 16 или Gen4 x8 через Edge Connector

Особенности кристалла XCVU9P-L2FSGD2104E

Документация доступна по ссылке

Средства проектирования и IP

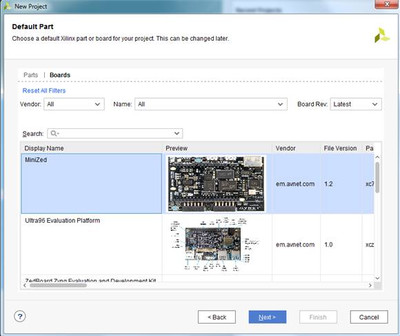

Средства проектирования (лицензии)

| Название | Описание | Тип лицензии |

| Vivado Design Suite Design Edition | Xilinx Vivado® - это специализированное ПО, ориетированное на процесс проектирования с помощью IP блоков (IP Centric), предназначенное для ускорения времени разработки на устройствах программируемой логики | Node locked и device locked для кристаллов XCVU9P с возможностью получения обновлений в течении одного года. Поддержка частичной реконфигурации |

| SDAccel Development Environment | SDAccel представляет собой среду разработки для приложений на OpenCL, предназначенную для разработки ускорителей на основе ПЛИС фирмы Xilinx. Эта среда позволяет одновременно программировать системный процессор и логику FPGA без необходимости разработки RTL. | Node locked и device locked для кристаллов XCVU9P с возможностью получения обновлений в течении одного года. |

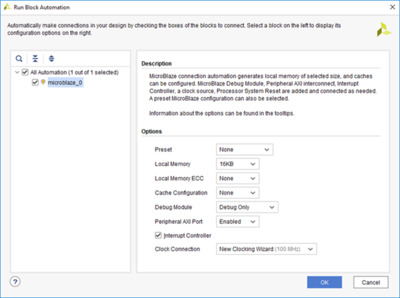

| Partial Reconfiguration | Partial Reconfiguration - это возможность динамически изменять блоки логики путем загрузки частичных битовых файлов, в то время как оставшаяся логика продолжает работать без перерыва. Технология частичной реконфигурации Xilinx позволяет разработчикам изменять функциональность платы ускорителя на лету, исключая необходимость полной перепрошивки FPGA и восстановления связи по PCIe во время загрузки частичных битовых файлов. |

Node locked and device-locked to the XCVU9P FPGA, with one year of updates. |

IP (Intellectual Property)

| Название | Описание | Тип лицензии |

| DDR4 SDRAM контроллер - это бесплатное IP-ядро, доступное в IP каталоге | Бесплатно | |

DMA for PCI Express (PCIe) Subsystem |

Xilinx® LogiCORE™ DMA для PCI Express (PCIe) реализует высокопроизводительный, конфигурируемый Scatter Gather DMA для использования с интегрированным блоком PCI Express 3.x. IP обеспечивает дополнительный AXI4 или AXI4-Stream интерфейс | Бесплатно |

Xilinx SmartConnect Technology |

Технология Xilinx SmartConnect обеспечивает высокий уровень производительности для линейки устройств UltraScale+™, решая проблему системного интерконнекта. |

Бесплатно |

SDAccel Platform Reference Design for Custom Board Support |

Проекты SDAccel компилируются для целевой платформой. SDAccel Platform reference Design представляет собой сочетание платы и компонентов аппаратной/программной инфраструктуры, на которых выполняются ядра приложения OpenCL. Этот эталонный дизайн предназначен для использования в качестве отправной точки, чтобы помочь разработчикам платформы добавить поддержку SDAccel для своих пользовательских плат PCIe. |

Бесплатно |