Архив новостей из мира FPGA

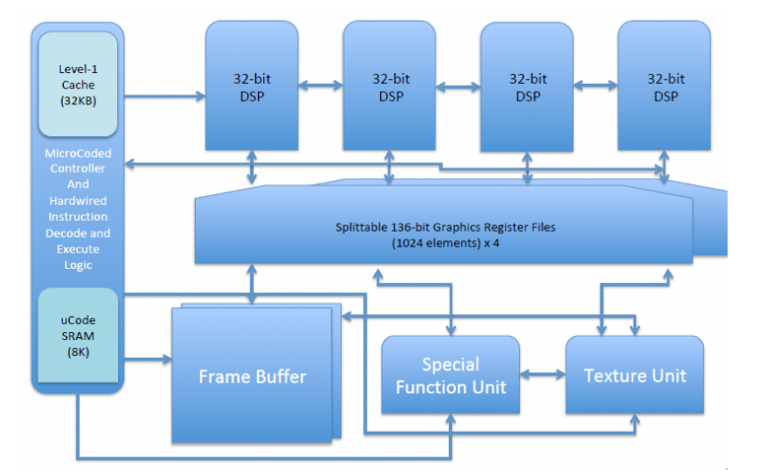

RV64X: бесплатный GPU RISC-V с открытым исходным кодом

Группа энтузиастов разработала графический процессор (GPU) RV64X на базе RISC-V. В рамках разработки предложен новый набор векторных инструкций, которые заточены под задачи 3Д графики. Данный GPU может быть реализован на FPGA и ASIC. Дизайн разрабатывается с учетом возможности масштабирования: ... Читать дальше »

3083

Поднимаем OpenCL

В блоге Адама Тейлора похоже появляется новая ветка статей, которая будет связана с написанием OpenCL кода под различные целевые платформы. В частности, в первой статье Адам поднимает простой проект на OpenCL для ускорителя Alveo U50. ... Читать дальше »

1921

3

ИИ в дата-центре: использование возможностей ПЛИС

В последние несколько лет машинное обучение (ML) стало наиболее перспективным методом извлечения значимых паттернов из данных. Этот радикально новый тип ИТ-нагрузки создает гораздо более интеллектуальные программные системы, но создает серьезные проблемы для традиционной инфраструктуры центров обработки данных. ... Читать дальше »

1770

1

Gowin объявляет о доступности ПЛИС автомобильного класса

Стандарт AEC-Q100 существует уже более 20 лет, определяя квалификационные требования к надежности автомобильных интегральных схем. Чтобы получить сертификат, соответствующий требованиям AEC-Q100 Grade 2, производитель должен представить продукт, способный работать в экстремальных условиях. ... Читать дальше »

1791

0

Разбираемся в типах программных лицензий. Заметка от Synopsys

Зачастую разработчики в своей работе используют готовые библиотеки, фреймворки, находят интересные решения на github или stack overflow и внедряют в свой продукт. Стоит иметь в виду, что используемый код идет с соответствующей лицензией, упоминание о которой вы легко можете найти в крупных репозиториях на github. ... Читать дальше »

2951

0

FPGA или микроконтроллер: что же выбрать?

Ох уж эти бесконечные холивары! Вот вам еще одна небольшая заметка формата "за/против", но в разрезе программируемой логики и микроконтроллеров (на русском). ... Читать дальше »

3060

0

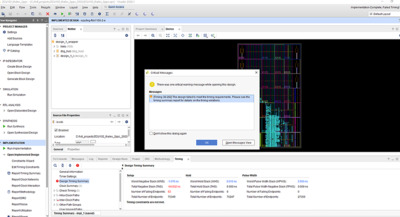

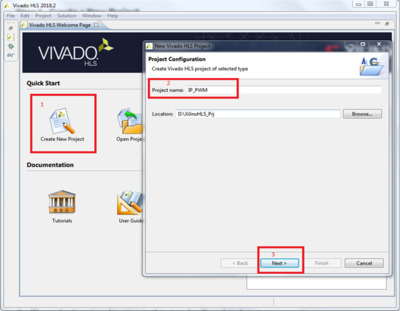

Silexica запускает первый коммерческий плагин для Vitis HLS

Компания Silexica анонсировала запуск плагина для Vitis. SLX Plugin позволит добавлять новые директивы и возможности по оптимизации компилятора. Появление такого плагина демонстрирует значимость, которую приносит иницитатива открытого исходного кода, утверждает вице-президен ... Читать дальше »

1391

0

Реализация интерпретатора CHIP-8 на Verilog

В блоге Juraj's Blog начат цикл статей по реализации интерпретатора CHIP-8 на языке Verilog. В первой части блога коротко рассказывается о структуре предстоящего проекта и ... Читать дальше »

1759

0

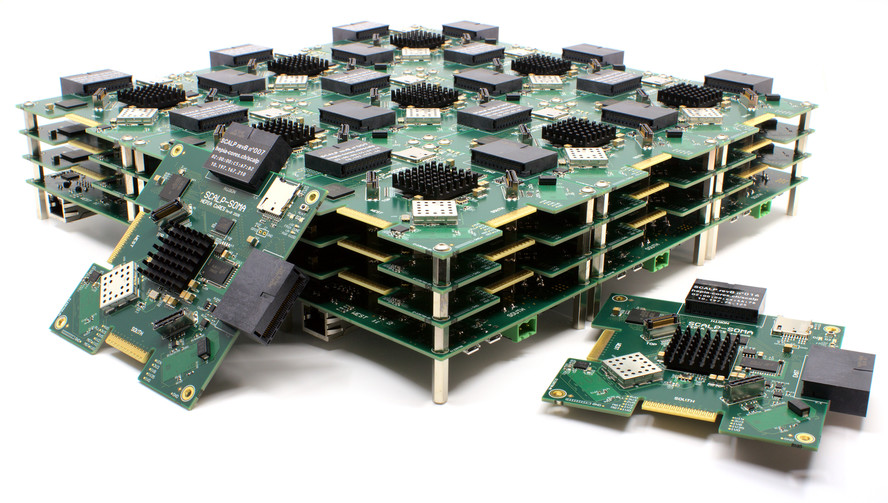

Самоконфигурируемая трехмерная мультиПЛИСовая адаптивная платформа

SCALP - вот такое вот многообещающее название имеет один интересный проект. SCALP - Self-configurable 3-D Cellular multi-FPGA Adaptive Platform - это аппаратная 3D multi-FPGA платформа, позволяющая создавать прототипы 3D-архитектур NoC с динамическими топологиями. ... Читать дальше »

1724

0

Microchip’s Анонсировала доступность PolarFire для космического применения

Компания Microchip анонсировала отгрузку чипов RT PolarFire®, выпущенных фирмой в соответствии со стандартом изделий космического назначения. Компания аттестовала данные ПЛИС по стандартам Mil Std 883 Class B, QML Class Q and QML Class V - самым высоким стандартам для монол ... Читать дальше »

1379

0 |

0