Статьи из раздела: Языки

Раздел: Языки

Распутываем виртуальные методы в SystemVerilog

В статье рассматривается работа виртуальных методов в SystemVerilog. Текст расчитан как на людей с базовыми познаниями в ООП. Впрочем, и более опытные инженеры, быть может, найдут для себя интересные примеры.

7378

Реализация базовых компонентов ЦОС: КИХ фильтр

В данной статье рассматриваются особенности реализации одного из базовых компонентов цифровой обработки сигналов – фильтра с конечной импульсной характеристикой

6981

2

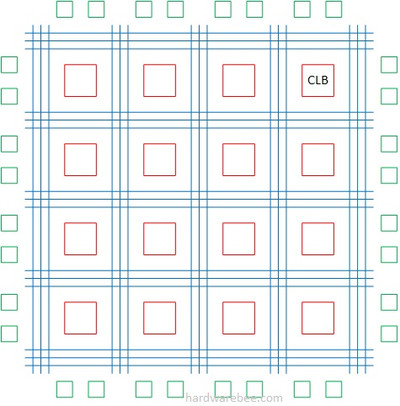

Поточное вычисление двоичного логарифма

В статье рассматриваются варианты реализации поточного вычисления двоичного логарифма, приводятся результаты измерения точности и ресурсоёмкости для ПЛИС Artix-7 и синтезатора Vivado 2020.2. Было протестировано 3 алгоритма вычисления log2(x) с некоторыми вариациями.

7550

2

Статическое в SystemVerilog

В данной статье мы рассмотрим отличия статических и автоматических переменных и функций. Мы увидим, что понятие “статический” имеет различные значения для модулей и классов, разберёмся, почему это так, и научимся выбирать нужный нам вариант.

Говорить будем преимущественно о симуляции, а также рассмотрим один пример синтеза.

11944

8

Вычисление двоичного логарифма итерационным методом на ПЛИС

Вниманию читателя предлагается алгоритм вычисления логарифма по основанию 2, предоставляется исходный код RTL-блока, анализируется вычислительная точность и ресурсоемкость реализации

10599

0

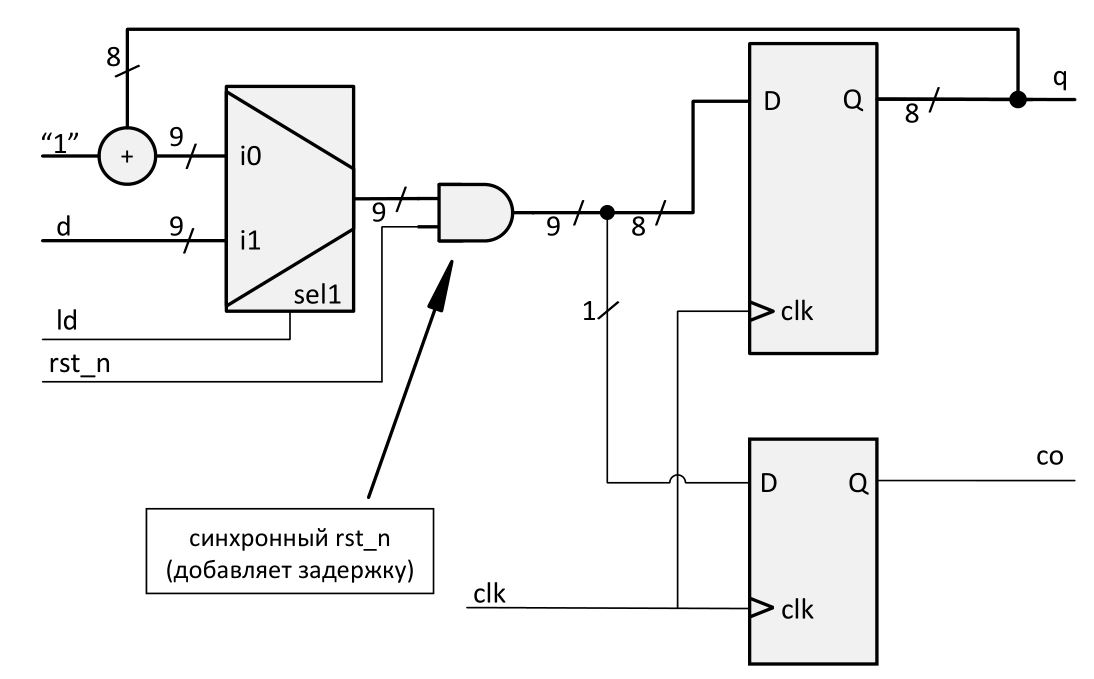

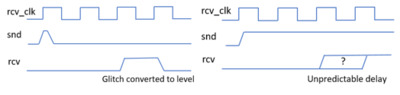

Асинхронный и синхронный сброс: Методы проектирования - часть вторая (раздел 4)

Вторая часть перевода (раздел 4) одной из фундаментальных статей о проектировании и применении синхронного и асинхронного сбросов. В этом разделе речь идёт об использовании синхронных сбросов.

7777

0

Что нового в VHDL 2019?

Эта статья, взята из доклада VHDL 2018: New and Noteworthy. С этим докладом выступил наш коллега Ливен Лемиенгре на DVCON 2018. Поскольку новый стандарт VHDL был утвержден и опубликован в 2019 году, все ссылки на 2018 год в этой статье были заменены на 2019 год

5524

0

0