ZYNQ HW: EBAZ4205: Часть 1 (Vivado 2020)

Оглавление

- Аннотация

- Обзор платы

- Приступаем к работе

- Сборка и настройка HW части

- SW часть проекта см часть 2

- Итоги см часть 2

- Ссылки см часть 2

Ссылка на PDF версию в конце статьи

Аннотация

Цель данного туториала - повторить создание проекта Hello World с выводом текстовой строки в последовательный интерфейс UART, но на плате EBAZ4205. Для этого нужно будет учесть аппаратные особенности этой платы. Так же, отличием этого туториала является использование Vitis вместо более раннего варианта SDK.

Обзор платы

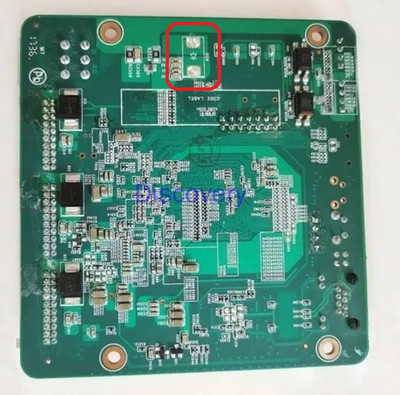

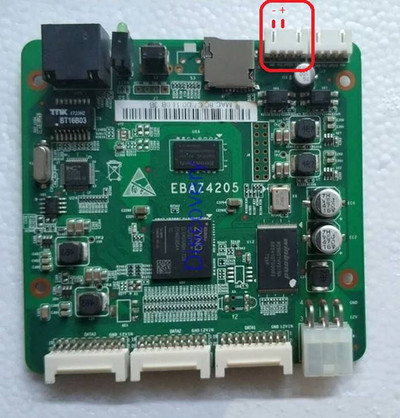

Плата EBAZ4205 является управляющей картой от крипто майнера Ebit E9 + BTC. Сейчас как майнер стала не актуальна, поэтому б/у платы появились по доступной цене (порядка 1000р) на ebay и aliexpress (поисковая фраза "ZYNQ 7000"). При покупке я выбрал более дорогой вариант, где продавец припаивает слот для MicroSD карточки на плату. По умолчанию слот не припаян. Кроме слота, продавец припаял еще разъем для подключения UART и JTAG для программирования. Кроме этого, перепаян резистор R2577, R2584 для загрузки системы не с flash а с MicroSD.

Параметры платы

ПЛИС XC7Z010CLG400, Dual Core Cortex A9 @ 666.66MHz and Artix-7 FPGA with 28k LEs.

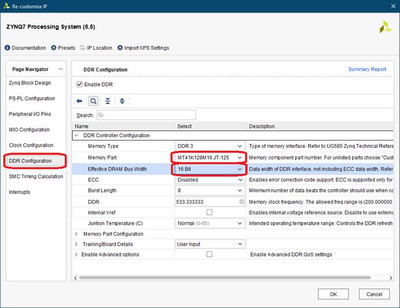

Внешняя память DDR3 256MB

Внешняя FLASH память - 128MB SLC NAND FLASH.

Ethernet трансивер для сети 10/100Mbps: IP101GA

Как становится ясно, плата требует небольшой доработки перед использованием. Для того, чтобы подать питание на плату, нужно запаять недостающий диод с обратной стороны.

После чего, питание можно будет подавать через стандартный разъем, похожий на Molex 6pin. Я же для подачи питания, использую раэъем подключения вентиляторов. Напряжение 5..12 вольт, ток 500 мА.

Программатор

В качестве программатора использую китайский Platform Cable USB II Model DLC10

Приступаем к работе

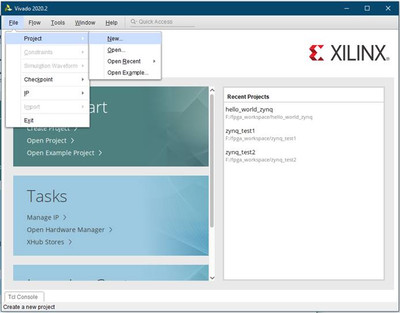

Еще одно отличие этой статьи от серии статей про Minized это использование Vivado 2020.2 и Xilinx Vitis 2020.2 (в отличие от SDK в более ранних версиях)

Сборка и настройка HW части

Создаем новый проект и попробуем повторить функционал, который выведет строчку "Hello world" чере UART порт (для того, чтобы это увидеть, нам потребуется переходник USB UART). В таком проекте потребуется настроить по-минимуму аппаратную часть ZYNQ: порт UART, DDR память; и написать прошивку для ядра.

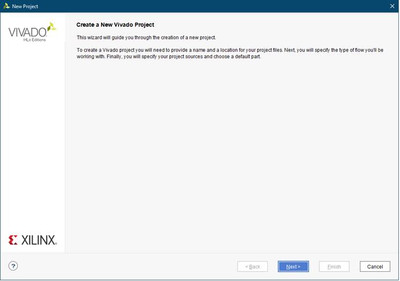

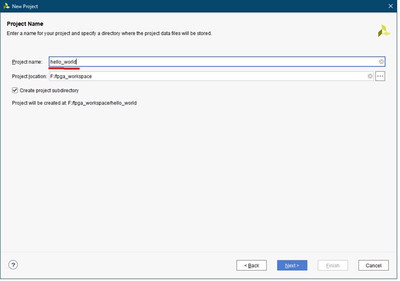

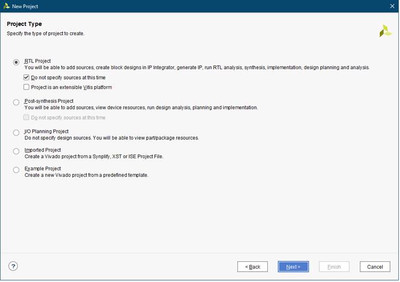

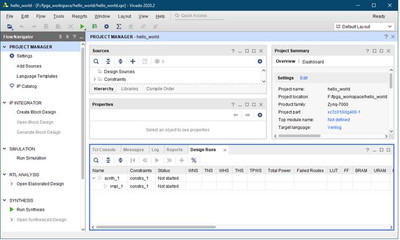

Задаем имя проекта

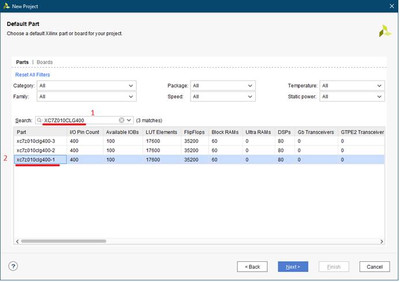

Выберем модель ПЛИС

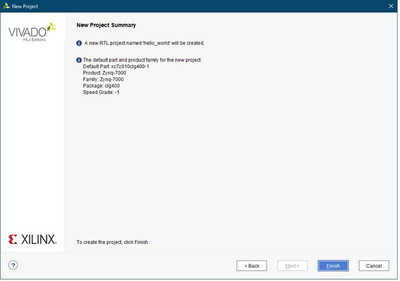

Нажмем Finish

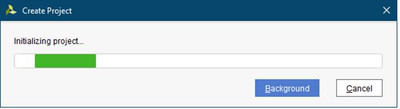

Дождемся инициализации проекта

Готово!

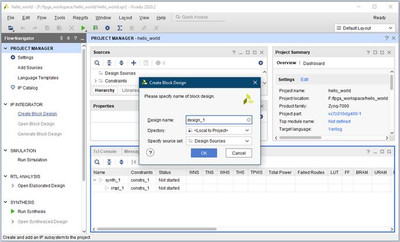

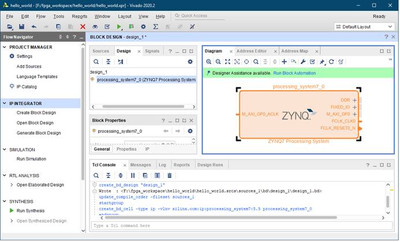

В IP INTEGRATOR создаем блок Create Block Design имя оставлю по умолчанию

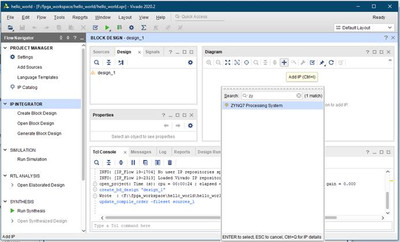

Добавлю систему ZYNQ7 на диаграмму

ZYNQ на диаграмме

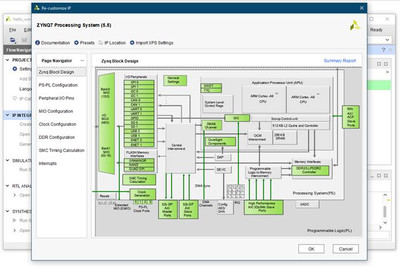

Дважды кликаем по блоку ZYNQ на диаграмме, чтобы перейти в настройки системы ZYNQ

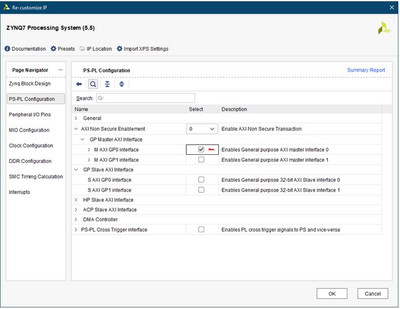

Переходим во вкладку PS-PL Configuration и на всякий случай снимаем галочку

Настроим аппаратные блоки, хотя некоторые могут и не потребоваться.

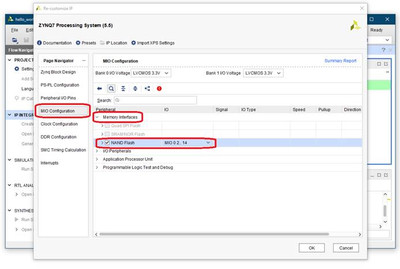

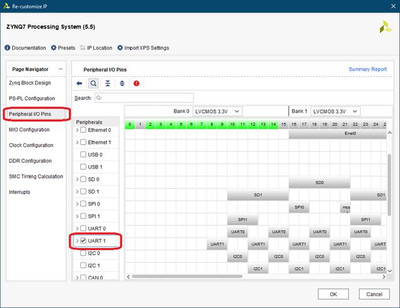

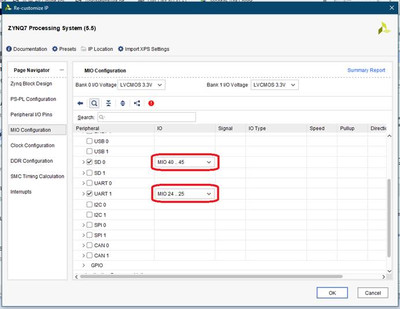

На вкладке MIO Configuration настроим SD и UART1

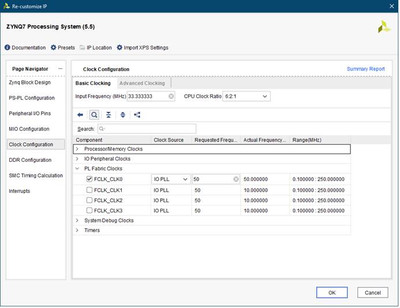

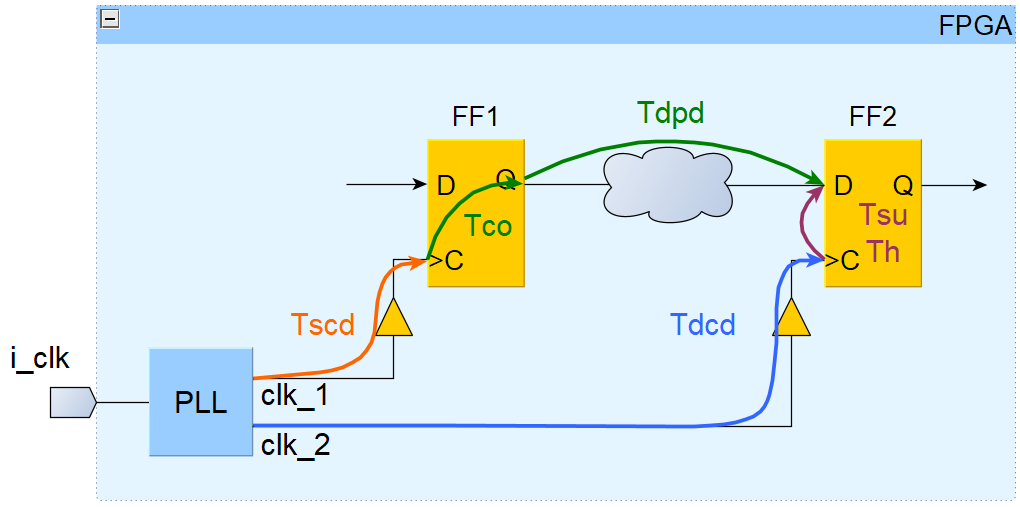

Если в будущих проектах планируется тактировать PL логику от системы ZYNQ в качестве источника, то это можно настроить во вкладке Clock Cinfiguration выход FCLK_CLK0

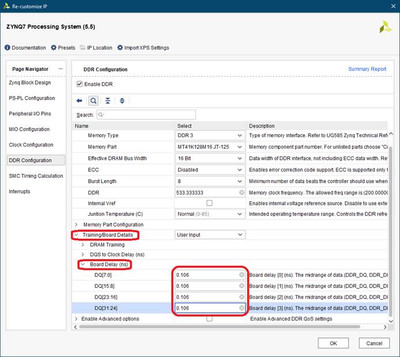

Далее, настроим параметры DDR

Там же параметры задержки

На этом все. Нажимаем "OK".

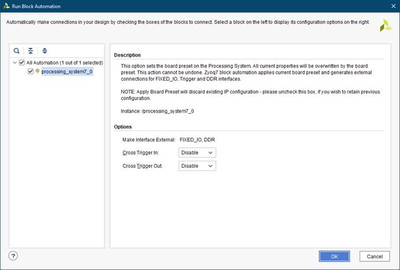

На диаграмме запускаем "Run Block Automation" оставляя параметры по умолчанию и тоже нажимаем "ОК"

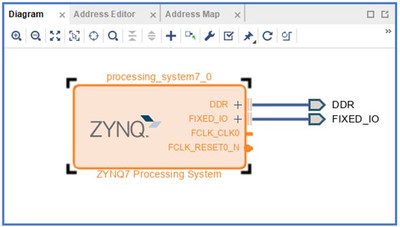

На диаграмме увидим следующее

Сохраняем диаграмму.

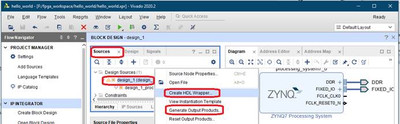

Переходим на вкладку Sources, выбираем диаграмму, создаем обертку и генерируем че-то там еще. Моя не понимать

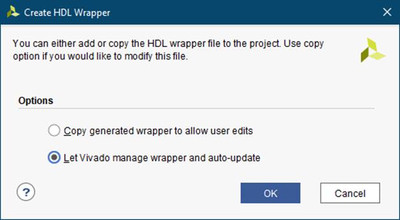

Create HDL Wrapper - cоглашаемся, пусть система обновляет файлы в случае изменения дизайна.

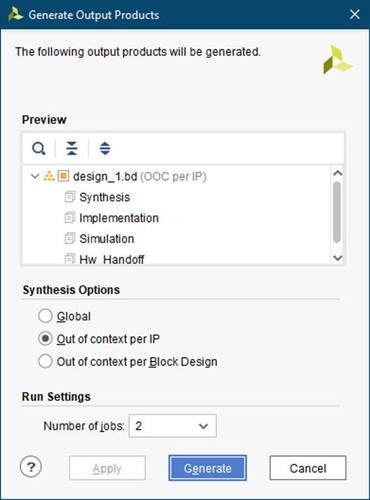

В Generate тоже оставляем все без изменений

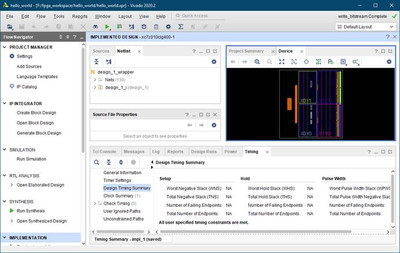

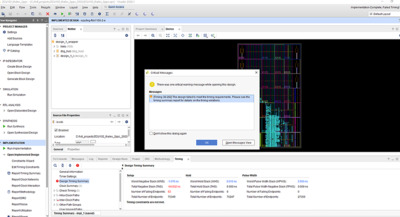

Далее запускаем Run Synthesis, Run Implementation, Generate Bitstream. В итоге можно открыть Implementation Design и посмотреть на него (как на новые ворота)

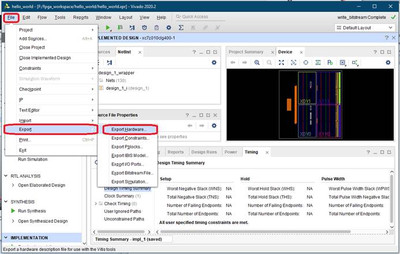

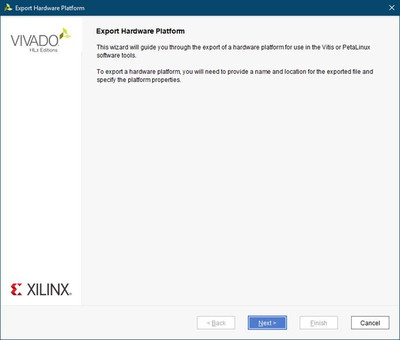

Далее экспортируем полученный результат

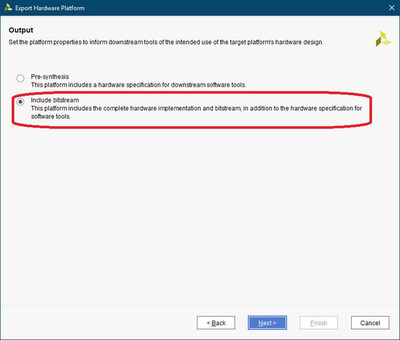

Включая bitstream

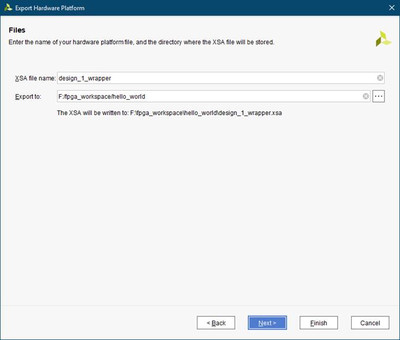

Пути и имя не меняем

Готово

Мы настроили аппаратную часть, экспортировали ее и готовы к написанию прошивки.

Продолжение Часть 2

|

Скачать статью в формате PDF (залогиньтесь) |

Поддержать автора | Поддержать проект fpga-systems |