Статьи из категории: Xilinx Vivado

Категория:Xilinx Vivado

Vivado Quality of Result (Перевод статьи MicroZed Chronicles)

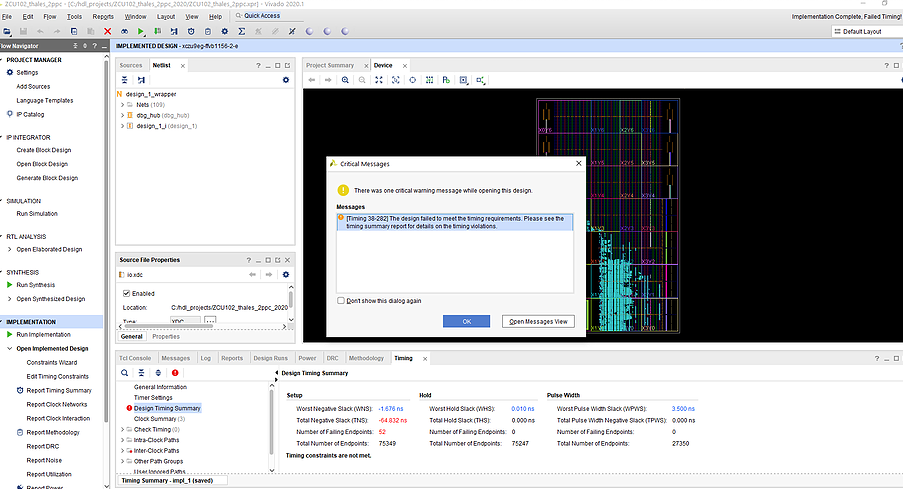

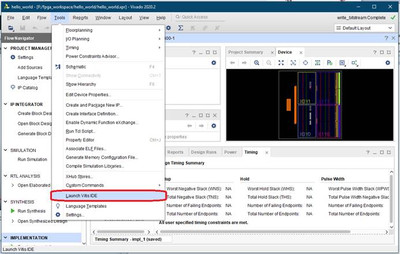

В данной статье будут рассмотрены инструменты Quality of Result Assesment [QoRA] и Quality of Result Suggestions [QoRS] поскольку оба этих инструмента предоставляют информацию для достижения необходимых временных ограничений [timing closure - временное соответствие, временные ограничение]

6521

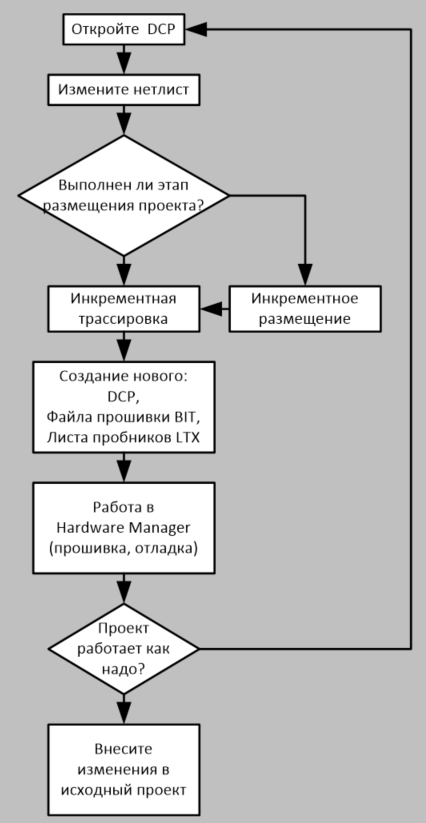

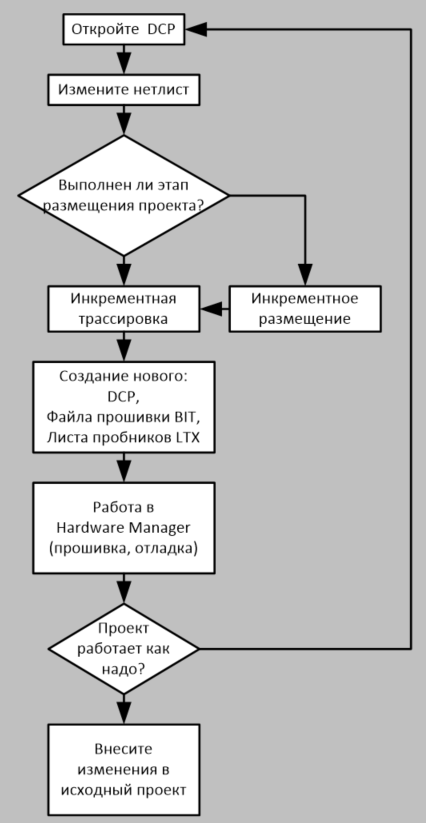

ECO Flow в Vivado или работа в режиме редактирования нетлиста. Часть 2

Продолжение руководства по работе Vivado Eco Flow

8136

0

ECO Flow в Vivado или работа в режиме редактирования нетлиста. Часть 1.

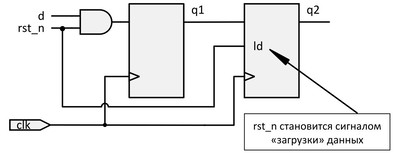

В статье рассмотрен режим работы Vivado, позволяющий вносить изменения в проект на уровне редактирования списка соединений (в дальнейшем – нетлиста). Описаны как сам режим ECO, так и некоторые нюансы, которые появляются во время работы в нём. Приведён демонстрационный пример и описана полная последовательность действий для получения результата, в работоспособности которой может убедиться каждый желающий. Статья будет полезна для «общего развития» FPGA-разработчикам, а особенно — тем, кто часто отлаживает проекты в Logic Analyzer. Надеюсь, работа в этом режиме вызовет интерес у разработчиков, работающих с большими кристаллами, время компиляции в которых может достигать часов (а то и десятков часов), поскольку в этом режиме время, затрачиваемое на имплементацию, при внесении изменений в нетлист может сократиться до буквально пары минут.

6492

0

Методика работы с Си модулями в симуляции стандартными средствами Vivado

Vivado и system Verilog позволяют разработчику использовать модули, написанные на Си. Данный метод называется DPI (Direct Programming Interface).

7582

0

Заметка о проблеме с контроллером памяти LPDDR2 Xilinx 7 Series MIS

В данном материале кратко изложена история о нетривиальной проблеме с имплементацией контроллера памяти LPDDR2 Xilinx 7 Series MIS.

4069

0

Vivado reprorts => report_clock_networks

Рассматриваем и разбираем отчёты Vivado. Эта статья посвящена report_clock_networks

5503

0

Vivado reprorts => report_clock_interaction

Рассматриваем и разбираем отчёты Vivado. Эта статья посвящена report_clock_interaction.

6815

2

7